引言

為了解決傳統DSP所面臨的速度低、硬件結構不可重構、開發升級周期長和不可移植等問題,本文應用Altera公司推出的NiosIl嵌入式軟核處理器,提出了一種具有常規DSP的NiosII系統功能SOPC解決方案。由于可編程的NiosII核含有許多可配置的接口模塊,用戶可根據設計要求,利用QuartusII和SOPC Builder對NiosII及其外圍系統進行構建。

用戶還可通過Matlab和DSP Builder,或直接用VHDL等硬件描述語言,為NiosII嵌入式處理器設計各類硬件模塊,并以指令的形式加入到NiosII的指令系統中,使其成為NiosII系統的一個接口設備,與整個片內嵌入式系統融為一體,而不是直接下載到FPGA中生成龐大的硬件系統。正是NiosII所具有的這些重要特點,使得可重構單片DSP系統的設計成為可能。

Nios II嵌入式系統設計流程

NiosII嵌入式處理器專為單芯片可編程系統設計而優化,是一種面向用戶、可以靈活定制的通用RISC(精簡指令集)嵌入式CPU。它采用Avalon總線結構通信接口,帶有增強的內存、調試和軟件功能,可采用匯編或C、C++等進行程序優化開發。NiosII具有32位指令集、32位數據通道和可配置的指令及數據緩沖。

與普通嵌入式CPU系統的特性不同,其外設可以靈活選擇或增刪,可以自定制用戶邏輯為外設,可以允許用戶定制自己的指令集。由硬件模塊構成的自定制指令可通過硬件算法操作來完成復雜的軟件處理任務,也能訪問存儲器或NiosII系統外的接口邏輯。設計者可以使用NiosII及外部的Flash、SRAM等,在FPGA上構成一個嵌入式處理器系統。

完整的基于NiosII的SOPC系統是一個軟硬件復合的系統,因此在設計時可分為硬件和軟件兩部分。NiosII的硬件設計是為了定制合適的CPU和外設,在SOPC Buider和QuartusII中完成。在這里可以靈活定制NiosII CPU的許多特性甚至指令,可使用Altera公司提供的大量IP核來加快開發NiosII外設的速度,提高外設性能,也可以使用第三方的IP核或VHDL來自行定制外設。

完成NiosII的硬件開發后,SOPC Buider可自動生成與自定義的NiosII CPU和外設系統、存儲器、外設地址映射等相應的軟件開發包SDK,在生成的SDK基礎上,進入軟件開發流程。用戶可使用匯編或C,甚至C++來進行嵌入式程序設計,使用GNU工具或其它第三方工具進行程序的編譯連接以及調試。

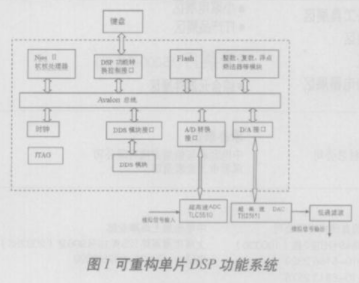

單片DSP系統構架

本系統為單片DSP可重構系統,能完成數字信號處理方面各功能的操作。其中NiosII軟件處理器主要完成人機交互和控制作用;FPGA的邏輯模塊從NiosII處理器接收控制信號和數據后,完成相應的硬件功能。系統框圖如圖1所示,除了軟核處理器NiosII外,存儲器、I/O接口以及FIR數字濾波器、IIR數字濾波器、DDS等應用模塊等均可作為外設嵌入在FPGA中。

這樣,整個DSP的數字信號處理部分全部集成在FPGA器件中,各模塊受NiosII處理器的控制。NiosIl處理器系統中有Avalon總線,它規定了控制器與從屬模塊間的端口連接以及模塊間通信的時序。數字頻率合成器(DDS)通過Avalon總線與NiosII處理器相連,能很方便地完成控制及數據傳送。

在本系統中,FPGA采用Cyclone EPICl2,它有12060個邏輯單元(LE)和2個鎖相環(PLL),提供6個輸出和層次時鐘結構以及復雜設計的時鐘管理電路。整個系統在NiosII處理器的控制下,可實現FIR、IIR數字濾波、快速傅立葉變換(FFT)算法、編/解碼等功能,系統還能進行DDS功能模塊設計,并構成具有數控頻率調制、正交載波調制解調、數控相位調制等功能的信號發生器。

系統中各功能模塊的選擇以及輸出信號調制方式和頻率的選擇均可通過外接的按鍵自由選擇。

系統硬件設計

系統的硬件系統包括FPGA、存儲器和外圍元器件3個部分。FPGA部分需要在SOPC Buider中設計,包含NiosII CPU核、內部時鐘、Avalon總線控制器、連接NiosII核的下載和調試程序的JTAG_UART通信模塊、DDS接口模塊及DDS模塊、FIR、IIR數字濾波器接口模塊及功能模塊、編/解碼模塊及接口模塊、Flash存儲器模塊等。

各外設模塊核通過在片上的Avalon總線與NiosII相連。為使具有DSP處理器功能的NiosII系統正常工作,在FPGA外圍接有一些控制鍵,以調度各模塊的應用。

建立Nios II嵌入式處理器系統

首先利用QuartusII建立項目工程,選用的目標器件為CycloneEPIC12,用SOPC Buider創建NiosII組件模型,生成硬件描述文件,鎖定引腳后進行綜合與適配,生成NiosII硬件系統下載文件。然后建立NiosII嵌入式系統,從SOPCBuider組件欄中加入需要的各種組件:如NiosIICPU Core、定時器Timer、JTAG_UART、Avalon三態總線橋、鍵輸入I/O口、Flash等。

另外,為了實現NiosII處理器對EPCSFlash存儲器的讀寫訪問,還要加入一個EPCS Serial Flash Controller組件,通過此控制器將用于FPGA配置的SOF文件和CPU運行的軟件一并存于EPCS器件中,以便大大簡化硬件系統組成結構。

為了保證所有組件的地址安排合法,要對各組件地址進行自動分配,最后進行全程編譯,即進行分析、綜合、適配和輸出文件裝配,以完成NiosII硬件系統的設計。 在NiosII硬件系統設計完成后,將配置文件下載到指定的FPGA中。通過SOPC Buider軟件窗口,可進入NiosII DSK軟件開發環境進行軟件設計。

DSP處理器功能系統的建立

使用DSP Buider在FPGA上進行DSP模塊的設計,可實現高速DSP處理。但是,在實際應用中,由于DSP處理的算法往往比較復雜,如果單純使用DSP Buider來實現純硬件的DSP模塊,會耗費過多的硬件資源,有時也無法完成復雜的運算。在DSP算法巾反復出現的一些運算,如復數乘法、整數乘法、浮點乘法等,在通用的CPU中都沒有專門的相關指令。

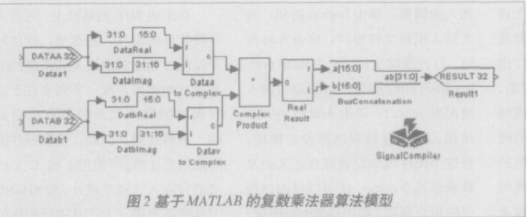

利用Nios II的自定制指令特性,在系統設計中,可利用MATLAB、DSPBuider或VHDL設計并生成復數乘法器、整數乘法器、浮點乘法器等硬件模塊,在QuartusII環境中對上述文件作一些修正后,在SOPC Buider窗口中將它們定制為相應的指令,并可設定或修改執行該指令的時鐘周期。在進行DSP算法運算時,可通過匯編或C,甚至C++來運用這些自定義指令進行嵌人式程序設計。

用MATLAB、DSP Buider設計的復數乘法器模型如圖2所示,它完成了16位的復數乘法,虛部和實部的位寬都是16位,可以用一個32位的值來表示該復數。在設計中,NiosII為32位數據,正好可以放置2個復數。

要將這個復數乘法器硬件模塊設置成相應的指令,還要進行以下操作:單擊圖標SignalCompiler對其進行轉換,選擇器件(用Cyclone)、選擇Quartusll綜合器,轉換后使其生成SOPCBuider的PTF文件。退出MATLAB后,在QuartusII環境中對轉換后所生成的復數乘法器的頂層VHDL文件進行修改。

在SOPCBuider窗口中雙擊cpu項,進入指令加入編輯窗;單擊Import按鈕,進入加入模塊文件窗口;單擊Add按鈕,打開頂層文件;單擊Read port-list from files按鈕,得到端幾加人情況顯示窗口;單擊Add to System按鈕,加入復數乘法器設計模塊,將這個硬件模塊設置成白定義的復數乘法指令comp。還可以修改該指令的指令周期。單擊Generate按鈕,進行SOPC生成。

另外,NiosII的外設是可任意定制的,NiosII系統的所有外設都通過Avalon總線與NiosII CPU相接。Avalon總線是一種協議較為簡單的片內總線,NiosII通過Avalon總線與外界進行數據交換。在本系統中,采用Avalon Slave外設方式加入了自定制Avalon總線組件A/D轉換接口模塊、D/A接口模塊,用于控制采樣ADC的工作并控制高速DAC的波形數據輸出。

而白定義的Avalon總線組件DDS模塊接口和DSP功能轉換控制接口則用于NiosII CPU對DDS模塊的控制及通過外部鍵盤來控制DSP功能的選擇。

系統軟件設計

指令生成并加入總線和各種需要加入的外設組件(如各類接口、flash等)后,對基于NiosII的SOPC系統進行編譯并下載到FPGA中。在NiosII的硬件系統生成的同時,SOPC Buider幫助用戶生成相應的SDK(軟件開發包)。由于在硬件開發中的Nios CPU及其外設構成的系統是自定制的,存儲器、外設地址的映射等都各不相同,需要專有的SDK,用戶新定制的指令也必須修改原有的編譯工具,這些都由SOPC Buider自動生成。

在生成SDK的基礎上,可進入系統軟件的設計。在這里,軟件的開發設汁與通常的嵌入式系統的開發設計相類似,唯一不同點在于這時面對的嵌入式系統是自己定制的、裁剪過的,因此,受到硬件的局限性會小些。可使用匯編、C、C++來進行嵌入式程序設計,使用GNU工具或其它第三方工具進行程序的編譯連接以及調試。

比如,將復數乘法器硬件模塊設置成相應的指令后,鎖定引腳,全程編譯。然后利用QuartusII編輯C程序進行測試。在FPGA中的NiosCPU中運行C程序。測試成功后,在DSP計算中遇到復數乘法就可以運用復數乘法指令。

DDS模塊還是以硬件形式固化在FPGA中,可以根據需要,利用DDS設計出幅度、相位和頻率調制器。

結語

這種將常用的硬件模塊生成指令,軟、硬件并存的設計方法在FPGA中可實現較復雜的DSP運算。整個系統除了ADC、DAC和控制選擇鍵盤外,都可在1片FPGA可編程芯片中實現。還可通過Avalon總線白定義各種接口模塊組件,提高整個DSP系統的靈活性,將軟件的靈活性和硬件的高速性予以結合。

編輯:jq

-

dsp

+關注

關注

554文章

8059瀏覽量

350420 -

FPGA

+關注

關注

1630文章

21796瀏覽量

606003 -

cpu

+關注

關注

68文章

10902瀏覽量

213013

發布評論請先 登錄

相關推薦

一種高靈敏的化學檢測系統

基于相變材料的可重構超構表面用于圖像處理

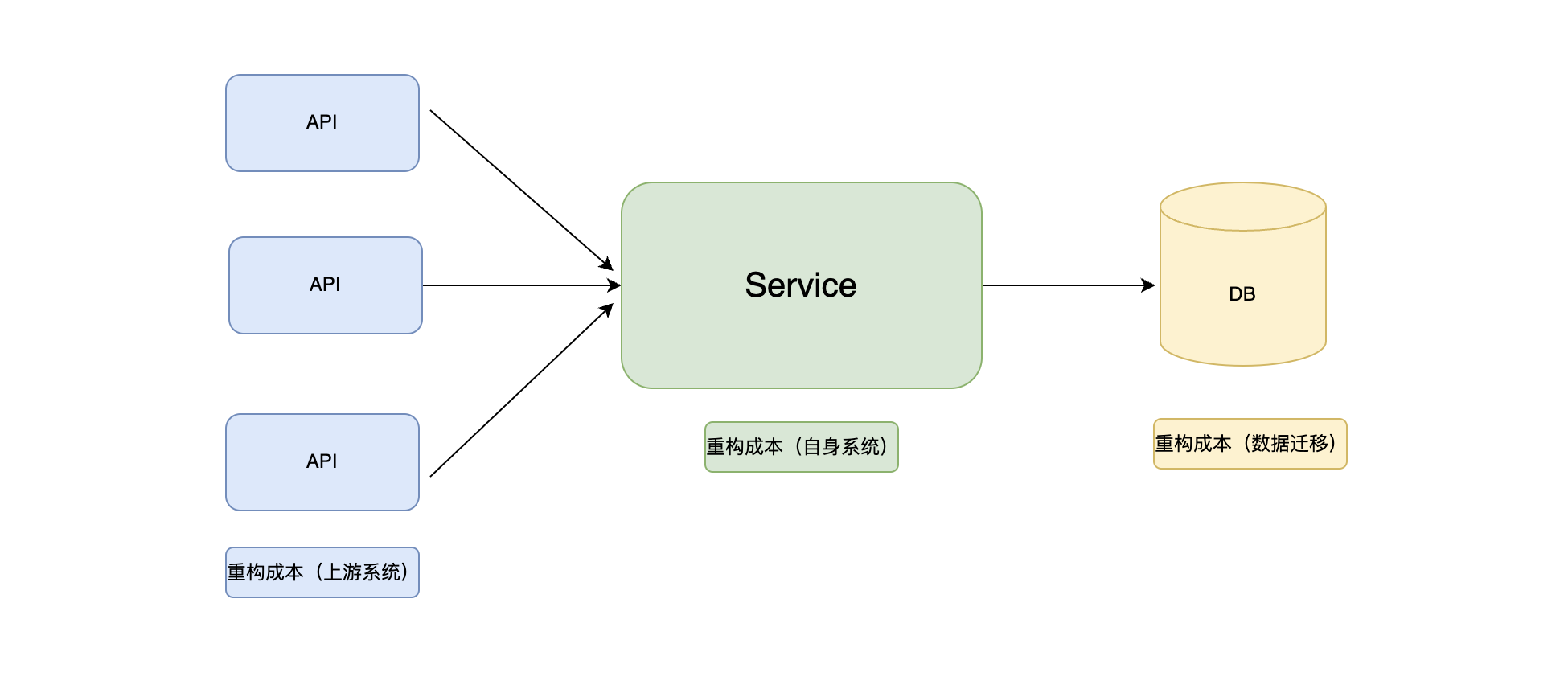

「重構:改善既有代碼的設計」實戰篇

66AK2L06多核DSP+ARM KeyStone II片上系統(SoC)數據表

66AK2Hxx多核DSP+ARM? KeyStone II片上系統(SoC)數據表

66AK2E0x多核DSP+ARM KeyStone II片上系統(SoC)數據表

一種供電總線技術POWERBUS二總線

rup是一種什么模型

Altera SOPC 嵌入式系統設計(一)

麥格納為中國本土汽車制造商提供可重構座椅系統

求助,關于TRAVEO? II MCU安全調試的幾個問題求解

dsp是嵌入式微處理器的一種設備嗎 ARM嵌入式微處理器有何特點?

【量子計算機重構未來 | 閱讀體驗】+ 了解量子疊加原理

介紹一種OpenAtom OpenHarmony輕量系統適配方案

一種關于Nios II的可重構DSP系統設計

一種關于Nios II的可重構DSP系統設計

評論