本文對Video out IP和Video Timing Controller IP進行簡要介紹,為后文完成使用帶有HDMI接口的顯示器構(gòu)建圖像視頻顯示的測試工程做準備。

Video out IP

簡介

AXI4-Stream to Video Out核心設(shè)計用于從實現(xiàn)視頻協(xié)議的AXI4-Stream接口連接到視頻源(并行視頻數(shù)據(jù)、視頻同步和空白)。該IP與Xilinx視頻定時控制器(VTC)核心一起工作。該核心提供了一個具有AX14-Stream接口的視頻處理核心和視頻輸出之間的橋梁。

特點

視頻輸出(帶同步信號的特定時序下的并行視頻數(shù)據(jù)--帶有行場同步信號和消隱信號的有效視頻數(shù)據(jù))。

輸入數(shù)據(jù)是通過AXI-stream的從接口。

可選擇的視頻時序同步模式,允許VTC發(fā)生器自由運行(主模式)或被控制(從模式)使用一個滯后機制。

自動同步視頻時間到AXI4-Stream視頻。

支持AXI4-Stream和視頻時鐘域之間的普通或獨立時鐘模式。

可選擇的FIFO深度32-8192位。

可選擇的輸入數(shù)據(jù)寬度8-256位。

支持隔行操作。

組件寬度轉(zhuǎn)換為8,10,12,16位。

AXI4-Stream to Video Out IP將AXI4-Stream視頻協(xié)議從使用此協(xié)議的Xilinx視頻處理IP轉(zhuǎn)換為帶有行場同步和特定時序信號的視頻輸出接口,從而與使用該視頻時序的普通視頻系統(tǒng)接口相互連接。

輸入輸出信號

AXI4-Stream to Video Out IP的輸入信號是一個AXI4-Stream從接口。該接口由并行視頻數(shù)據(jù),tdata,握手信號tvalid和ready,以及兩個標(biāo)志,tlast和tuser組成,用于識別視頻流中的特定像素。tlast信號指定每一行的最后一個有效像素,也稱為行結(jié)束(EOL)。tuser信號指定幀的第一個有效像素,稱為幀的開始(SOF)。這兩個標(biāo)志對于標(biāo)識AXI4流接口上的像素位置是必要的,因為不存在行場同步信號。只有有效的像素數(shù)據(jù)被攜帶在總線上。

AXI4-Stream to Video Out IP的輸出信號是常用的視頻接口。視頻接口包含以下信號:

Parallel video data

Pixel clock

Vsync

Hsync

Vbank

Hblank

Data Valid

Field ID

IP架構(gòu)圖

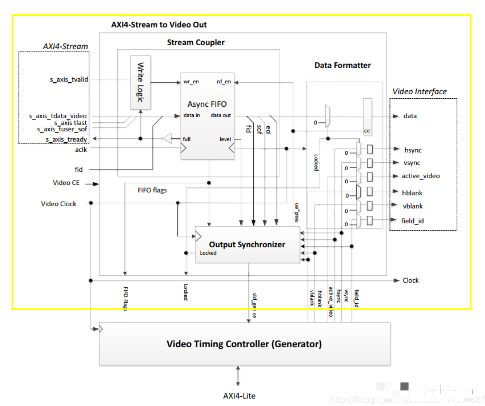

該IP設(shè)計要和VTC IP一起使用。 VTC IP核提供視頻時序參數(shù),并產(chǎn)生視頻時序信號。下圖給出的是AXI4-Stream to Video Out IP的系統(tǒng)架構(gòu):

在AXI4-Stream to Video Out IP的內(nèi)部,通過一個異步的FIFO進行跨時鐘域的數(shù)據(jù)信息的緩存處理,然后經(jīng)過一個輸出同步器(output synchronizer)將AXI-stream的視頻數(shù)據(jù)和VTC生成的視頻時序參數(shù)進行同步,最終生成輸出端口的視頻輸出的接口。

支持時鐘模式

AXI4-Stream to Video Out IP支持兩種時鐘模式:slave和master時鐘模式。這里的主從模式是對于 VTC ip而言的。

slave模式

在slave模式下,AXI4-Stream to Video Out IP輸出的視頻數(shù)據(jù)的時序信號(行場同步、消隱等),將由VTC生成相對應(yīng)的時序信號進行自適應(yīng),AXI4-Stream to Video Out IP通過vid_gen ce信號進行控制時序信號的輸出,從而達到輸出的視頻信號和輸出信號同步的目的。

master模式

在master模式下,VTC IP核將會不受限制地運行,相位差取決于啟動條件。這時就要求AXI4-Stream to Video Out IP的視頻數(shù)據(jù)盡量滿足VTC IP核產(chǎn)生的時序信號。

通常,建議使用slave模式來最小化緩沖區(qū)域和延遲時間都需求。

FIFO深度配置

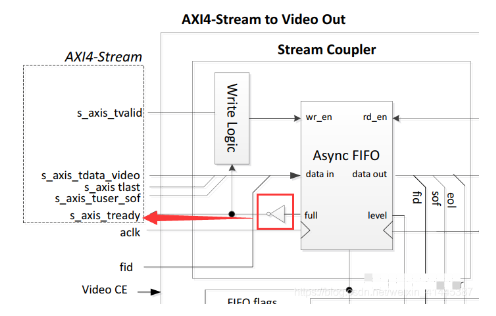

在AXI4-Stream to Video Out IP,通過一個異步的FIFO進行跨時鐘域的數(shù)據(jù)信息的緩存處理,這里就要考慮FIFO的深度的具體配置,當(dāng)FIFO的深度不合適時,很容易造成FIFO讀空或者寫滿讀滿,得到的視頻數(shù)據(jù)容易造成丟失。這里讀滿的時候影響不太大因

為到FIFO讀滿后,F(xiàn)ULL信號會進行取反使得tready信號拉低,從而使得視頻數(shù)據(jù)傳輸暫停。

考慮FIFO為空時,當(dāng)輸出的視頻信號處于數(shù)據(jù)有效輸出的階段,也就是正常的顯示器顯示的區(qū)域,則會造成當(dāng)前像素點讀取錯誤,并且后續(xù)的像素點都可能錯位。

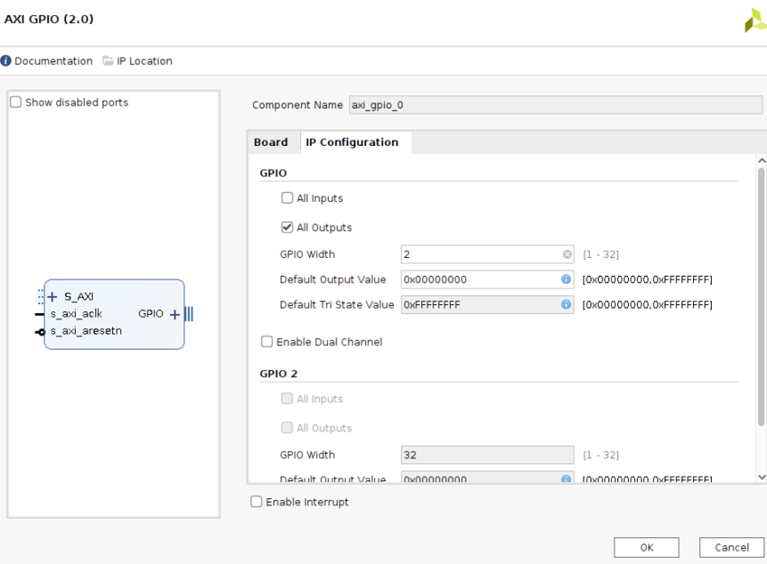

當(dāng)調(diào)用該IP時,F(xiàn)IFO深度可以通過GUI界面進行選擇。異步FIFO的緩沖要求主要取決于上游處理器通過AXI4-Stream時鐘(aclk)和視頻輸出時鐘(vid_io_out_clk)頻率之間的相對數(shù)據(jù)速率,以及正在傳輸?shù)男盘栕鳛闃?biāo)準。如果上游AXI4-Stream來源不能提供數(shù)據(jù)以持續(xù)的速度等于或大于視頻時鐘頻率,然后需要額外的緩沖存儲傳入的像素之前,當(dāng)他們需要這樣的像素可以生成一個連續(xù)流輸出沒有過早讀空的FIFO。換句話來說,就是如果輸入數(shù)據(jù)的時鐘小于輸出數(shù)據(jù)的時鐘,我們可以通過提前存儲數(shù)據(jù)的方式來彌補傳輸時的數(shù)據(jù)傳輸速度差異。如果從AXI4-Stream時鐘(Faclk)獲得的持續(xù)像素率等于或大于視頻輸出像素時鐘(Fvclk),那么當(dāng)輸入的AXI4-Stream數(shù)據(jù)中沒有停頓時,只需要最小緩沖區(qū)大小(32個位置)。在該情況下,F(xiàn)IFO在每行的EOL拉高后讀空。如果Faclk小于Fvclk,可能需要額外的緩沖。FIFO必須存儲足夠的像素,以供應(yīng)他們在整個活動線連續(xù)。這意味著輸入FIFO還必須足夠大,以在此期間連續(xù)提供輸出像素。

可以計算出先進先出初始填充水平的一階近似。假設(shè)R小于1,則計算最小初始填充層:FIFO Initial Fill Level = 32 + Nhactive * (1- R) + Nhstall * (1/R)

其中Nhactive是行活動周期的時鐘滴答數(shù)。Nhblank是水平消隱周期的時鐘滴答數(shù)。Nhstall是進入的流在水平活動期間被停止的時鐘滴答數(shù)。R是計算為Faclk/Fvclk的時鐘比率。當(dāng)R大于等于1時,可以去掉第二項[Nhactive * (1 - R)]。Nhstall很難通過分析來確定。

總FIFO深度必須略大于初始填充水平,以防止FIFO溢出:FIFO depth min = 32 + FIFO initial Fill Level在每種情況下,這都少于一整行數(shù)據(jù),所以如果提供了行緩沖區(qū),就足夠了。然而,在許多情況下,不需要完整的行緩沖區(qū)。

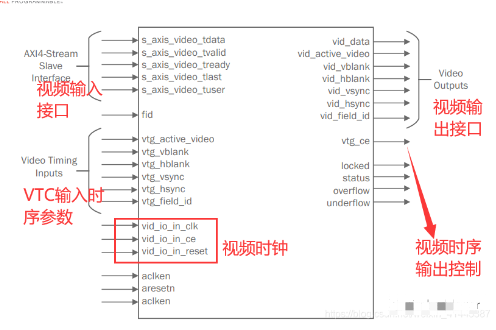

接口框圖

下圖描述了該IP可用的各種接口。

Video Timing Controller IP

簡介

Video Timing Controller IP是一個通用視頻時序信號發(fā)生器和檢測器。所有的視頻系統(tǒng)都需要視頻時序信號的管理,這些信號用于同步傳輸進程。VTC IP核的功能是檢測和產(chǎn)生這些時序信號。在該IP的輸入端,自動檢測水平和垂直同步脈沖,極性,消隱時間和活動視頻像素相關(guān)時序參數(shù);在輸出端口,它產(chǎn)生水平和垂直消隱和同步脈沖使用的標(biāo)準視頻系統(tǒng),包括支持可編程脈沖極性。該IP通常與Video in to AXI4-Stream IP一起用于檢測傳入視頻數(shù)據(jù)的格式和時序信息,或與AXI4-Stream to Video out IP一起用于為視頻輸出設(shè)備(如視頻監(jiān)視器)生成輸出視頻時間。

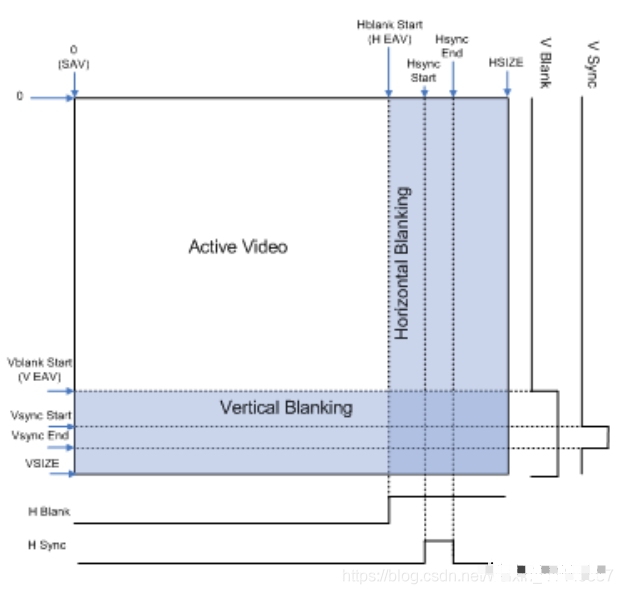

視頻時序

在對視頻數(shù)據(jù)輸出時,要根據(jù)視頻時序參數(shù)來進行時序信號的驅(qū)動從而保證視頻數(shù)據(jù)的正常輸出。視頻系統(tǒng)可以利用不同極性的行場同步或消隱信號的不同組合來同步處理和控制視頻數(shù)據(jù)。VTC IP通過提供一個高度可編程和靈活的核心,允許檢測和生成視頻系統(tǒng)內(nèi)的各種時序信號,從而簡化了視頻時序信號產(chǎn)生的工作。

支持工作模式

Video Timing Controller IP支持AXI4-Lite接口和一個固定模式接口。

AXI4-Lite接口允許將IP輕松地合并到Vivado項目中,并且可以通過AXI4-Lite。

Constant接口利用圖形用戶界面(GUI)可配置的IP參數(shù)來設(shè)置固定模式操作的IP。

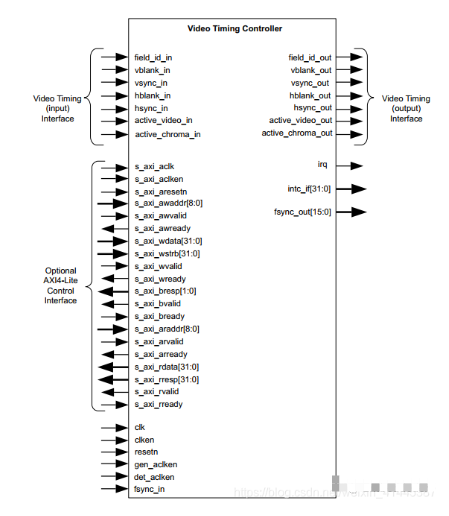

接口框圖

下圖描述了該IP可用的各種接口。

責(zé)任編輯:lq6

-

顯示器

+關(guān)注

關(guān)注

21文章

5010瀏覽量

140406 -

發(fā)生器

+關(guān)注

關(guān)注

4文章

1368瀏覽量

61858 -

fifo

+關(guān)注

關(guān)注

3文章

389瀏覽量

43857 -

HDMI接口

+關(guān)注

關(guān)注

1文章

134瀏覽量

34180

原文標(biāo)題:ZYNQ-Video out IP和Video Timing Controller IP簡介

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Multi-Scaler IP的Linux示例以及Debug(上)

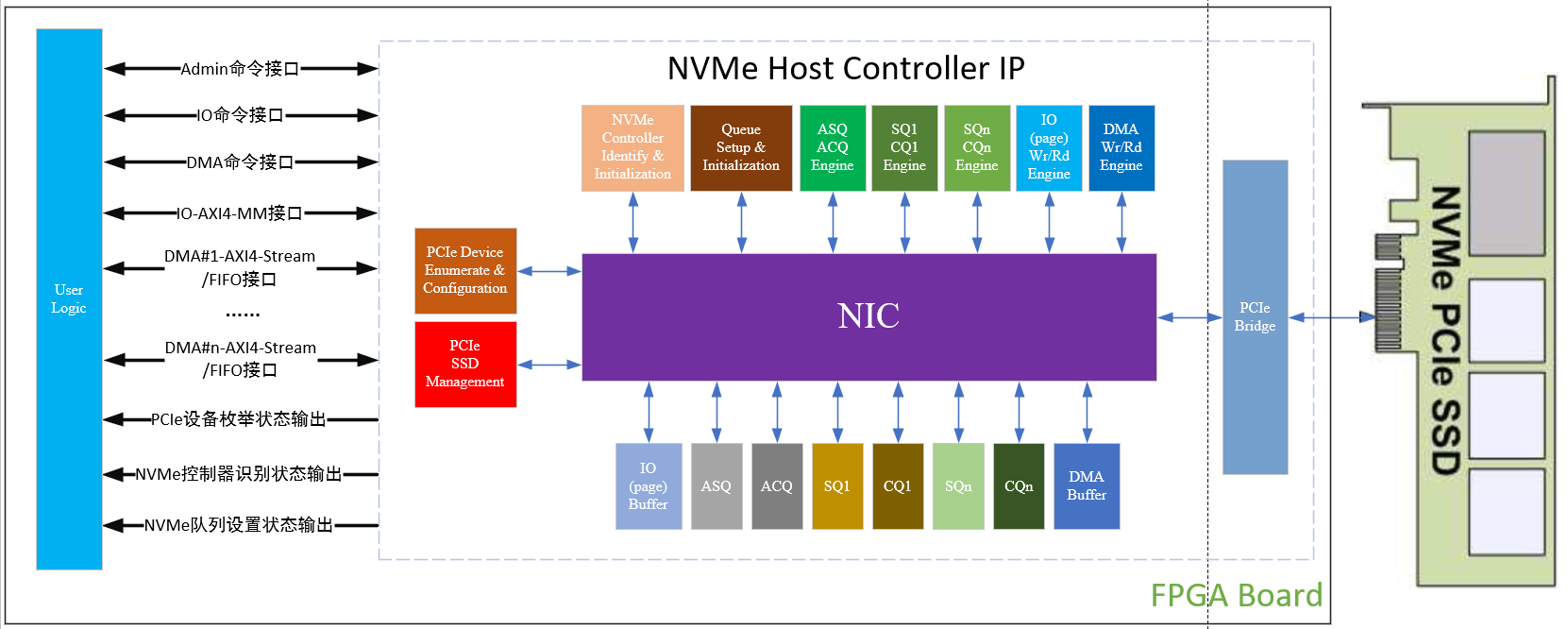

Xilinx FPGA高性能NVMe SSD主機控制器,NVMe Host Controller IP

Xilinx FPGA NVMe主機控制器IP,高性能版本介紹應(yīng)用

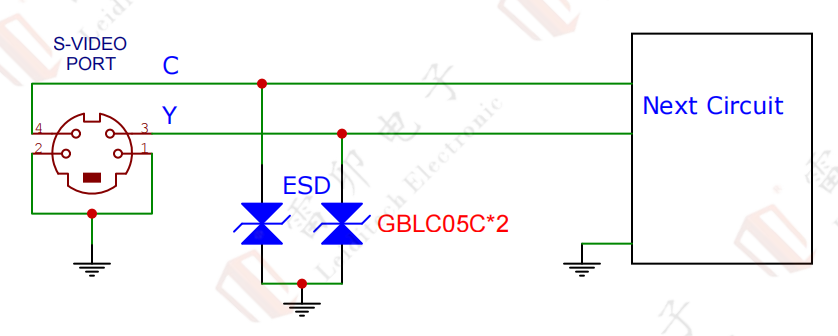

淺談S-VIDEO接口靜電浪涌防護

淺談S-VIDEO接口靜電浪涌防護

SATA3.0 Host Controller IP介紹

NVMe Host Controller IP實現(xiàn)高性能存儲解決方案

Xilinx FPGA NVMe Host Controller IP,NVMe主機控制器

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

關(guān)于Video out IP和Video Timing Controller IP的介紹

關(guān)于Video out IP和Video Timing Controller IP的介紹

評論