隨著后疫情時代的來臨,大多數(shù)人依然在采用線上視頻會議的工作方式 但是您是否曾經(jīng)想過 所有會議內(nèi)容和數(shù)據(jù)的傳輸需要怎樣的技術? 面對疫情造成的前所未有的視頻流量激增 數(shù)據(jù)中心運營商也開始重新思考其當前架構并探索在本質(zhì)上更便于擴展且效率更高的新配置在此背景下 一種有望大幅提升資源利用率的新架構正在興起 這就是“可組合式基礎設施”

可組合式基礎設施

可組合式基礎設施能夠解耦資源并將資源匯集,從而實現(xiàn)了資源的隨處調(diào)用。它還能為工作負載提供數(shù)量恰好的資源,并經(jīng)由軟件迅速完成重新配置。 可組合式基礎設施由 CPU 池、SSD 池和加速器池構成,它們互聯(lián)在一起并由基于標準的配置框架控制,能極大提高數(shù)據(jù)中心的資源利用率。在這樣的架構中,不同的工作負載可能有不同的計算、存儲和加速要求,而資源將進行相應分配,避免浪費硬件資源。

時延挑戰(zhàn)

上述方法在理論上似乎很完美,但實際上存在一個嚴重的問題:時延。當您分解資源并將它們移得更遠的時候,就會因 CPU 和 SSD 或 CPU 與加速器之間的網(wǎng)絡流量而導致延遲增大和帶寬縮小。除非您有某種方法來減少網(wǎng)絡流量并提高資源間的互聯(lián)效率,否則這會造成嚴重的限制。在解決時延難題方面,FPGA 能發(fā)揮三大關鍵作用:

將 FPGA 作為靈活應變的加速器,針對每種工作負載進行定制以實現(xiàn)最佳性能;

FPGA 讓算力貼近數(shù)據(jù),從而降低時延,并最大限度縮小所需帶寬;

FPGA 的靈活應變智能架構能夠在不產(chǎn)生額外延遲的情況下實現(xiàn)資源的高效率池化。

靈活應變的加速

基于 FPGA 的計算加速器的第一大優(yōu)勢就是顯著提升如今亟需的工作負載的性能。在實時視頻流應用的視頻轉碼用例中,F(xiàn)PGA 解決方案的性能通常比 x86 CPU 高出 30 倍,這有助于數(shù)據(jù)中心運營商解決并發(fā)流大幅增加的問題。另一個示例是在基因組測序的關鍵領域。一位近期成為賽靈思客戶的基因組研究機構發(fā)現(xiàn),基于賽靈思 FPGA 的加速器能以比 CPU 快 90 倍的速度獲得結果,幫助醫(yī)療研究人員以過去幾分之一的時間完成 DNA 樣本測試。

讓算力更貼近數(shù)據(jù)

可組合式數(shù)據(jù)中心內(nèi)的 FPGA 能發(fā)揮的第二大優(yōu)勢是,讓靈活應變的算力貼近數(shù)據(jù)。在 SmartSSD 計算存儲器件中使用賽靈思 FPGA,能為過去一般由 CPU 運行的高速搜索、解析、壓縮和加密等功能提速。這有利于卸載 CPU,將其用于更復雜的任務,而且還有助于減少 CPU 和 SSD 之間的流量,從而減少帶寬消耗并降低時延。 與之類似,賽靈思 FPGA 現(xiàn)在也用在 SmartNIC 中。例如賽靈思新款 Alveo SN1000,它不僅能為活動數(shù)據(jù)加速,提供線速數(shù)據(jù)包處理、壓縮和加密服務,還能針對特定數(shù)據(jù)中心或客戶適應定制的切換要求。

智能架構

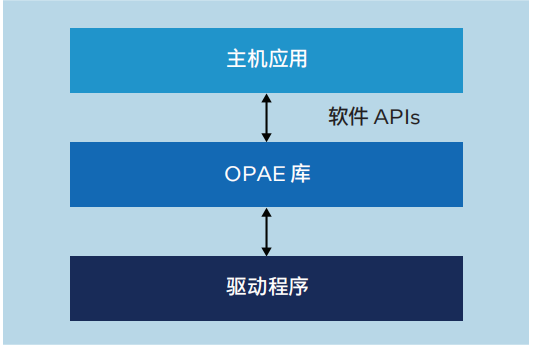

如果將 FPGA 靈活應變的計算加速與低時延連接結合,便會使得可組合式數(shù)據(jù)中心更進一步。您可以將高計算強度的工作負載分配給采用自適應智能架構互聯(lián)的加速器集群,按需創(chuàng)建高性能計算機。 當然,如果不能以最優(yōu)加速算法為計算加速器、SmartSSD 和 SmartNIC 編程,然后按正確數(shù)量將它們配置給每個工作負載,那么這些好處都是空談。在這方面,我們已經(jīng)開發(fā)出一個綜合全面的軟件協(xié)議棧,它利用 TensorFlow 和 FFMPEG 等特定領域行業(yè)框架,并配合賽靈思的 Vitis 開發(fā)平臺運行。在智能資源分配方面, RedFish 等更高級的配置框架也有用武之地。 在可組合式數(shù)據(jù)中心掀起的激動人心的變革中 賽靈思器件和加速器卡將成為新型高效架構的關鍵模塊依托快速的可重配置能力、低時延以及能夠適應不斷變化的工作負載的靈活架構賽靈思已經(jīng)為在這場變革中發(fā)揮重大作用做好準備

原文標題:可組合數(shù)據(jù)中心:讓算力更貼近數(shù)據(jù)

文章出處:【微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606035 -

數(shù)據(jù)

+關注

關注

8文章

7145瀏覽量

89583

原文標題:可組合數(shù)據(jù)中心:讓算力更貼近數(shù)據(jù)

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發(fā)圈】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

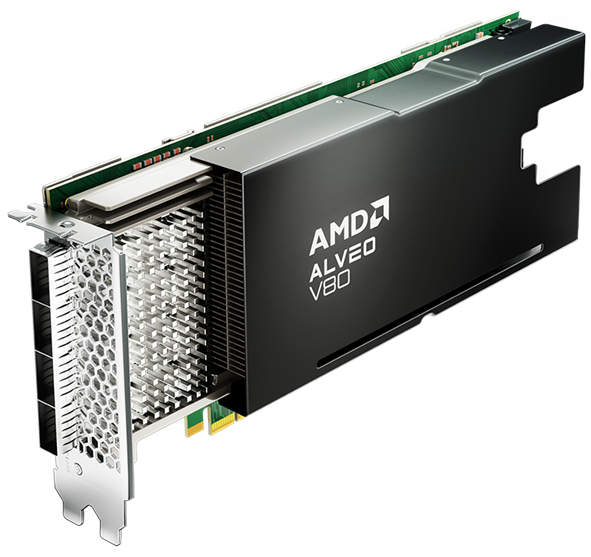

2.34納秒超低時延,滿足金融市場高頻交易,AMD發(fā)布新一代金融加速卡

ARM開發(fā)板與FPGA的結合應用

GPU加速計算平臺是什么

FPGA加速深度學習模型的案例

云計算與邊緣計算的結合

應變片的靈敏系數(shù)是什么,它與電阻絲連接方式

基于菲數(shù)科技FA728Q加速卡實現(xiàn)低時延LLT應用

FPGA在人工智能中的應用有哪些?

基于FPGA的類腦計算平臺 —PYNQ 集群的無監(jiān)督圖像識別類腦計算系統(tǒng)

電阻應變片的連接方式有哪些?

借助全新 AMD Alveo? V80 計算加速卡釋放計算能力

將FPGA靈活應變的計算加速與低時延連接結合

將FPGA靈活應變的計算加速與低時延連接結合

評論