軟件無線電(Software Radios)是一種新的無線電通信的體系結構。具體來說,軟件無線電是以可編程的DSP或CPU為中心,將模塊化、標準化的硬件單元用總線方式連接起來,構成通用的硬件平臺,并通過軟件加載來實現各種無線通信功能的開放式體系結構。

隨著通信的發展,高速傳輸技術引起廣泛的研究和注意。到目前為止,無線傳輸的速率受限于硬件條件。要實現高速傳輸,就必須結合各種芯片的特點,使硬件平臺具有簡單、通用的特點,因此需要開發一個通用平臺。

DSP在控制和信號處理方面有優勢,基帶信號的調制、解調及FFT/IFFT等運算可以由DSP實現,但是在實時處理方面受到現有DSP處理速度和能力的制約。對于信號突發檢測這種運算量大的處理,尤其是在高速傳輸時,通常要使用FPGA。FPGA特有的流水線設計結構可以使前后級在時間上并發,達到高效、高速。為了減小DSP在信號處理上的壓力,同時滿足高速要求,采用專用數字變頻芯片來實現數字上下變頻。

為了和軟件無線電的思想統一,在系統設計時考慮兼容單載波調制解調方式,采用DSP、FPGA、上下變頻器的方案,不使用專用調制解調芯片。

1 OFDM原理和基帶信號模

正交頻分復用[1]OFDM(Orthogonal Frequency Division Multiplex)是一種多載波調制方式,通過減小和消除碼間串擾的影響來克服信道的頻率選擇性衰落。它的基本原理是將信號分割為N個子信號,然后用N個子信號分別調制N個相互正交的子載波。由于子載波的頻譜相互重疊,因而可以得到較高的頻譜效率。近幾年OFDM在無線通信領域得到了廣泛的應用。

當調制信號通過無線信道到達接收端時,由于信道多徑效應帶來的碼間串擾的作用,子載波之間不再保持良好的正交狀態,因而發送前需要在碼元間插入保護間隔。如果保護間隔大于最大時延擴展,則所有時延小于保護間隔的多徑信號將不會延伸到下一個碼元期間,從而有效地消除了碼間串擾。當采用單載波調制時,為減小ISI的影響,需要采用多級均衡器,這會遇到收斂和復雜性高等問題。

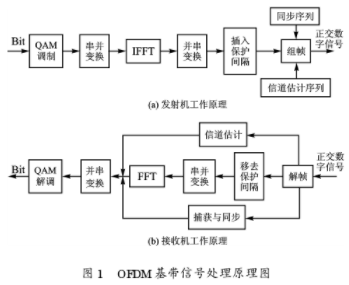

圖1是OFDM基帶信號處理原理圖。其中,圖1(a)是發射機工作原理,圖1(b)是接收機工作原理。

在發射端,首先對比特流進行QAM或QPSK調制,然后依次經過串并變換和IFFT變換,再將并行數據轉化為串行數據,加上保護間隔(又稱“循環前綴”),形成OFDM碼元。在組幀時,須加入同步序列和信道估計序列,以便接收端進行突發檢測、同步和信道估計,最后輸出正交的基帶信號。

當接收機檢測到信號到達時,首先進行同步和信道估計。當完成時間同步、小數倍頻偏估計和糾正后,經過FFT變換,進行整數倍頻偏估計和糾正,此時得到的數據是QAM或QPSK的已調數據。對該數據進行相應的解調,就可得到比特流。

這里僅討論軟件功能模塊,具體算法不在此涉及。

2 硬件結構

OFDM調制解調與常規調制解調相比,所需的運算量大,尤其是當系統選用的子載波個數多時,僅在發射端的IFFT變換和接收端的FFT變換所需的時間就很長。通常使用FPGA和高速的DSP解決該問題。由于在接收端還要完成信號突發檢測、同步和頻偏校正等數字信號處理,所以接收端對實時性要求更高。在該系統中,使用FPGA完成信號的突發檢測和定時,DSP完成FFT/IFFT變換和QAM/QPSK調制解調

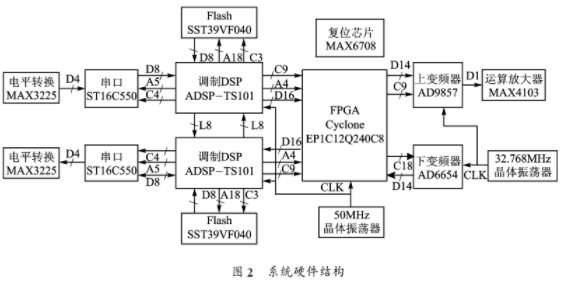

本系統主要由4部分組成: DSP、FPGA、正交數字上變頻器(Quadrature Digital Upconverter)、正交數字下變頻器(Quadrature Digital Downconverter)。系統硬件結構如圖2所示。圖中,D表示數據總線,A表示地址總線,C表示控制總線, L表示鏈路口數據線, 字母后面的數字表示總線的位數。50 MHz晶振為兩片DSP及FPGA提供時鐘信號,32.768 MHz高穩定度晶振為AD9857和AD6654提供高質量的時鐘信號。復位芯片MAX6708控制DSP、FPGA、AD9857、AD6654和ST16C550的復位。

DSP完成QAM或QPSK的調制解調和FFT/IFFT變換。系統所使用的DSP[2]是ADI公司的Tiger sharc TS101。該DSP具有以下特性: 最高工作頻率為300 MHz,3.3 ns指令周期;6 MB片內SRAM;2個計算模塊,每個模塊都有1個ALU、1個乘法器、1個移位寄存器和1個寄存器組;2個整型ALU,用來提供尋址和指針操作;14個DMA控制器;1149.1 IEEE JTAG口。對于OFDM基帶處理,該DSP最大的特點是: 進行256點的復數FFT變換,僅需3.67 μs。

正交數字上變頻器采用ADI公司的AD9857。AD9857[34]最高工作頻率為200 MHz,輸出中頻頻率范圍為0“80 MHz;內部集成半帶濾波器、CIC(Cascaded Integrator Comb)濾波器, 反SINC濾波器和高速的14位數/模轉換器,其核心是一個相位連續的直接數字頻率合成器DDS (Direct Digital Synthesizer)。在該方案中,AD9857工作在正交調制模式,其32位頻率控制字使輸出頻率的最高精確度為:SYSCLK(系統時鐘)除以232。

正交數字下變頻器采用ADI公司的AD6654。AD6654[5]內部集成了一個14位、92.16 Msps的模/數轉換器和4/6通道的數字下變頻器。每個通道可獨立配置。數字下變頻內部集成了頻率變換器、可編程級聯梳狀濾波器(CIC)、2個濾波器組和數字自動增益控制。其中: 頻率變換是通過32位數控振蕩器實現的;CIC實現1”32倍的抽取;2個濾波器組包括FIR濾波器和2倍抽取的半帶濾波器。輸入的中頻模擬信號經過ADC和頻率變換后,使用濾波器組進行濾波和抽取,最后并行輸出正交基帶數字信號。輸入中頻信號頻率最高可到200 MHz,此時,使用欠采樣技術。

3 參數設計及調制

信號波形作者采用PCB八層板設計,實現了該系統的硬件平臺,并在此平臺基礎上實現了高速OFDM傳輸和常規單載波調制解調,形成了一個通用寬帶高速調制解調平臺。設計的目的是要在該平臺上實現現有的全部物理層的算法,特別是實現實時OFDM傳輸系統。對OFDM系統提出的指標要求如表1所列。

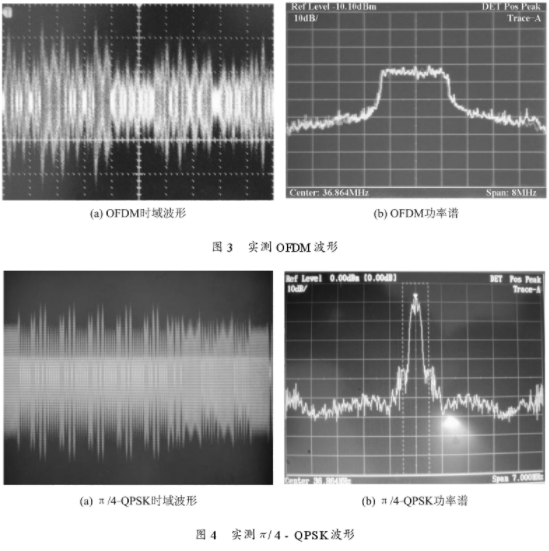

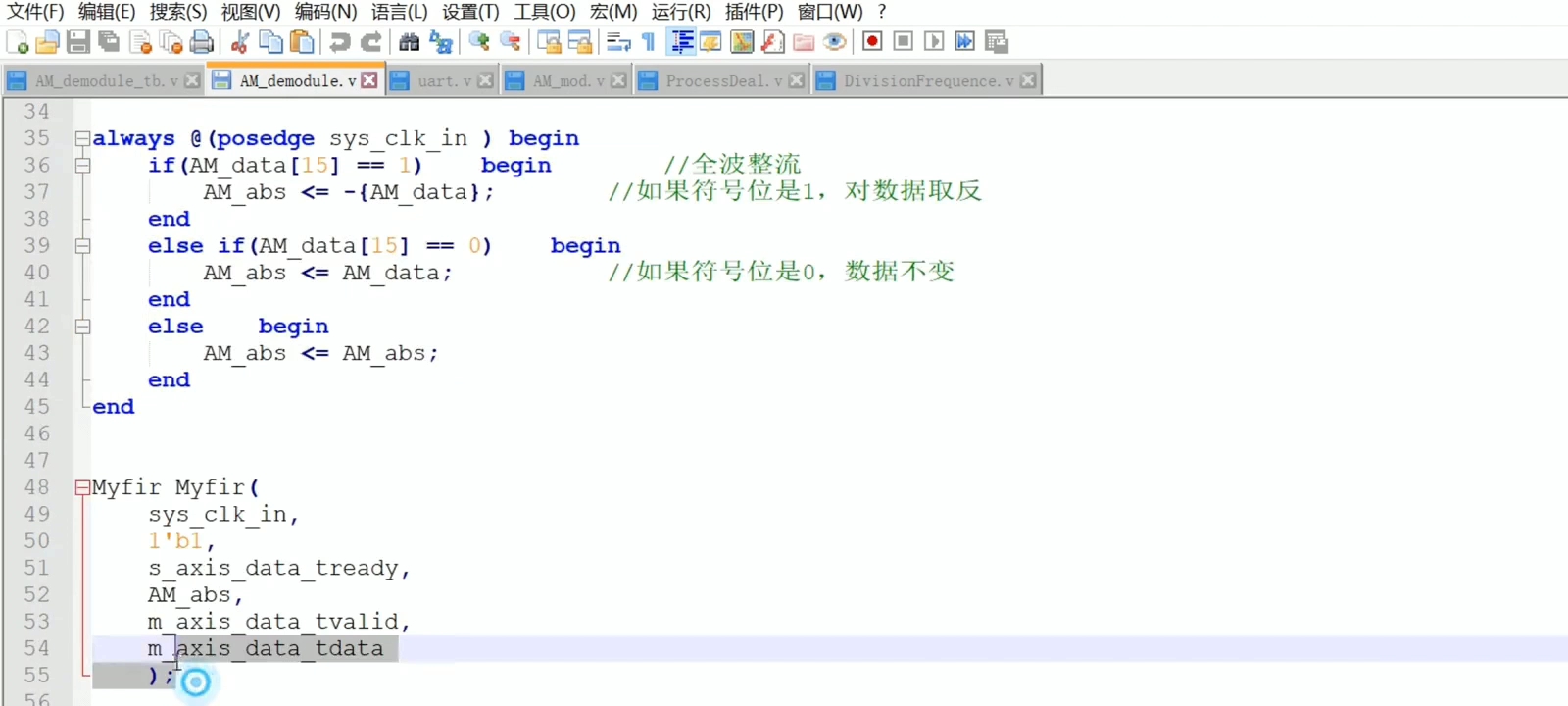

圖3給出了32路子載波OFDM在上述參數設計下的已調信號波形(見圖3(a))及其功率譜(見圖3(b))。圖中子載波調制方式為QPSK,碼元頻率為中頻頻率36.864 MHz,帶寬是2.048 MHz。圖4給出了一種單載波調制制式(以π/4QPSK為例)的時域波形(見圖4(a))及其功率譜(見圖4(b))。另外,數字調制方式的碼元頻率可達2 MHz(即對于四相調制,比特速率可達4 Mbps;對于32QAM調制,比特速率可達10 Mbps),且子載波調制方式、比特(或碼元)速率、輸出中頻均可調。

圖4 實測π/4-QPSK波形

4 結論

本文所提出的方案有以下特點:

① 基于雙DSP的結構,可工作在雙工方式,同時完成信號的發射和接收;工作在TDMA方式下或半雙工時,DSP可通過Link口進行高速通信,有利于并行處理,以提高傳輸速率。DSP利于基帶信號的實時處理,可以實現高速調制解調。

② 變頻器具有頻率分辨率高、頻率變化速度快、相位連續、易于數字控制等特點。采用DSP和變頻器的方案,不僅可以實現模擬調制解調,而且可以實現各種數字調制解調,兼容傳統調制解調和新型調制解調方式。

③ 在DSP和變頻器之間使用FPGA,實現突發信號的同步捕獲,可以分擔DSP的部分任務,從而提高系統的實時性。

責任編輯:gt

-

dsp

+關注

關注

554文章

8059瀏覽量

350394 -

FPGA

+關注

關注

1630文章

21796瀏覽量

605976 -

變頻器

+關注

關注

251文章

6584瀏覽量

145805

發布評論請先 登錄

相關推薦

如何實現多天線多載波的數字上下變頻的FPGA?

多天線多載波的數字上下變頻的FPGA實現方法有哪些?

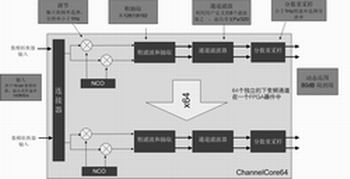

使用一個FPGA便可實現的64通道下變頻器

基于FPGA的數字下變頻器的設計與實現

多天線多載波的數字上下變頻的FPGA實現

基于專用數字下變頻芯片GC5016的寬/窄帶數據下變頻系統設計及數據分析與解調

介紹多天線多載波數字上下變頻的FPGA實現方法

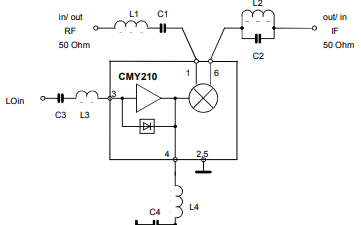

CMY210全端口,單端,通用上下變頻器的詳細資料免費下載

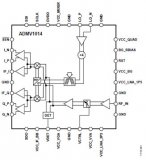

ADI ADMV1014 24-44GHz寬帶微波下變頻器解決方案

基于FPGA的數字下變頻器(DDC)的設計

采用DSP和FPGA和上下變頻器實現單載波調制解調系統的設計

采用DSP和FPGA和上下變頻器實現單載波調制解調系統的設計

評論