處理器內(nèi)核越復(fù)雜,面積和功耗就越大。但是,隨著處理器處理數(shù)據(jù)的方式變得更加復(fù)雜,復(fù)雜性并不是一個(gè)單一的衡量維度。在選擇處理器IP內(nèi)核時(shí),為您的項(xiàng)目選擇正確的復(fù)雜性很重要。

思考復(fù)雜性的一些方法包括:

字節(jié)長(zhǎng)

執(zhí)行單元

特權(quán)/保護(hù)

虛擬內(nèi)存

安全功能

通常,字節(jié)越短,內(nèi)核越小,功率越低,但是,并非總是如此。8位內(nèi)核(例如8051)的門數(shù)可與最小的32位內(nèi)核相比,但功耗通常更差。8位內(nèi)核需要更多的存儲(chǔ)器訪問權(quán)限,這是因?yàn)槊總€(gè)時(shí)鐘周期需要較少的計(jì)算量,需要更多的周期。最終的影響是它需要更多功能來完成計(jì)算。

處理器內(nèi)核在其執(zhí)行單元的復(fù)雜性方面差異很大。最簡(jiǎn)單的是基本的單個(gè)ALU,它們需要通過簡(jiǎn)單的指令來實(shí)現(xiàn)許多通用操作。例如,使用shift和add來實(shí)現(xiàn)乘法。因此,內(nèi)核具有硬件乘法器和除法器是普遍的。如果需要良好的浮點(diǎn)性能,則添加硬件浮點(diǎn)單元將提供明顯更好的性能。此選項(xiàng)可用于Codasip的Bk3和Bk5RISC-V內(nèi)核,但價(jià)格更貴。

到目前為止,我們已經(jīng)假設(shè)單個(gè)計(jì)算線程和標(biāo)量處理單元可以一次執(zhí)行一條指令。超標(biāo)量體系結(jié)構(gòu)具有指令級(jí)并行性,能夠提取多個(gè)指令并將其發(fā)送到不同的執(zhí)行單元。例如,Western Digital EH1和EH2 SweRV內(nèi)核有兩個(gè)執(zhí)行單元。理論上,單線程雙核處理器可以具有單核兩倍的性能。但是,線程可能會(huì)掛起,這會(huì)使兩個(gè)執(zhí)行單元暫時(shí)處于非活動(dòng)狀態(tài)。如果有兩個(gè)硬件線程,一個(gè)線程掛起后,另一個(gè)線程可以繼續(xù)執(zhí)行。

處理器的流水線深度可能有很大差異,并且深度與延遲之間存在直接關(guān)系。一些應(yīng)用程序可以忍受高延遲,結(jié)果是對(duì)中斷的響應(yīng)變慢,以換取較高的時(shí)鐘頻率和吞吐量。其他應(yīng)用程序需要對(duì)中斷的快速響應(yīng),因此需要更短的流水線。

復(fù)雜性的另一個(gè)方面是特權(quán)模式。模式越多,核心邏輯就越復(fù)雜。許多嵌入式應(yīng)用程序以機(jī)器模式運(yùn)行,這意味著代碼具有對(duì)內(nèi)核的完全訪問權(quán)限。例如Linux中的root特權(quán)。必須完全信任此類代碼,以避免產(chǎn)生負(fù)面后果。在更復(fù)雜的應(yīng)用程序中,可以提供一系列特權(quán),例如機(jī)器,管理員和用戶。普通應(yīng)用程序?qū)⒃诰哂凶畲蟊Wo(hù)程度的用戶模式下運(yùn)行,而一些需要更高權(quán)限的軟件將使用管理員模式。Linux需要這三種模式,這就是Codasip開發(fā)具有Linux功能的Bk7內(nèi)核的原因。

虛擬內(nèi)存還需要其他處理器資源,例如內(nèi)存管理單元(MUU)和轉(zhuǎn)換后備緩沖器(TLB),以處理將虛擬內(nèi)存地址轉(zhuǎn)換為物理地址的操作。這在面積和功耗方面帶來了額外的成本,而沒有提高處理器的吞吐量。但是,虛擬內(nèi)存對(duì)于使用豐富的操作系統(tǒng)(例如Linux)是必不可少的,該操作系統(tǒng)可以使用更復(fù)雜的軟件。

因此,在選擇處理器內(nèi)核時(shí),請(qǐng)確定所需的執(zhí)行單元,內(nèi)存管理,特權(quán)和安全性。這種結(jié)合將決定內(nèi)核的復(fù)雜性。

責(zé)任編輯:lq6

-

處理器

+關(guān)注

關(guān)注

68文章

19407瀏覽量

231186 -

內(nèi)核

+關(guān)注

關(guān)注

3文章

1382瀏覽量

40422

原文標(biāo)題:如何選擇合適的處理器內(nèi)核

文章出處:【微信號(hào):zhixinkeji2015,微信公眾號(hào):芯片逆向】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

AN-400:選擇DSP處理器的注意事項(xiàng)--為什么選擇ADSP-2181

EE-345:SHARC處理器的啟動(dòng)內(nèi)核定制和固件可升級(jí)性

EE-290:管理SHARC處理器上的內(nèi)核PLL

杰和課堂|如何快速選擇一款合適的云終端

組成放大電路時(shí)必須遵循的原則

組合邏輯電路設(shè)計(jì)時(shí)應(yīng)遵循什么原則

電源空載電壓的確定應(yīng)遵循的原則是什么

分壓接法滑動(dòng)變阻器選擇原則

信號(hào)分析和信號(hào)處理必須遵循的原則

嵌入式系統(tǒng)的微處理器選擇

嵌入式微處理器如何選擇 嵌入式微處理器體系結(jié)構(gòu)有哪兩種

FPGA開發(fā)如何降低成本,比如利用免費(fèi)的IP內(nèi)核

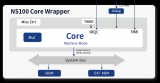

芯來科技發(fā)布超低功耗嵌入式RISC-V處理器CPU IP—NS100系列內(nèi)核

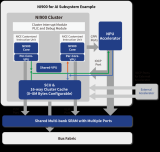

芯來科技正式發(fā)布首款專用處理器產(chǎn)品線Nuclei Intelligence系列

選擇處理器IP內(nèi)核時(shí)應(yīng)遵循哪些原則?

選擇處理器IP內(nèi)核時(shí)應(yīng)遵循哪些原則?

評(píng)論