作者:謝玲,甘良才,郭見兵

跳頻通信是一種載頻按照一定規(guī)律變化的多頻率移頻鍵控,具有抗干擾性強(qiáng)、保密性好、頻帶利用率高的特點,易于兼容,便于構(gòu)成多種通信網(wǎng)。正是由于這些特點,跳頻通信系統(tǒng)在現(xiàn)代軍事和交通運(yùn)輸通信中得到了廣泛的應(yīng)用。國外近幾年推出了大量跳頻電臺的產(chǎn)品,如美國HAKRIS公司的中速跳頻電臺RF-5010、美國Rockwell公司的SINGARS-U超快速跳頻電臺等。這些電臺均采用微處理機(jī)控制,功能齊全,輕便靈活,操作簡單。

利用跳頻圖案的良好正交性和隨機(jī)性,可以在一個寬的頻帶內(nèi)容納多個跳頻通信系統(tǒng)同時工作,將多個電臺組成通信網(wǎng)絡(luò),完成專向通信或網(wǎng)絡(luò)通信,達(dá)到頻譜資源共享的目的,從而提高頻譜的有效利用率,增加用戶通信的靈活性。短波信道是一種時變衰落信道,為保證各接收端均能在適當(dāng)時刻進(jìn)行取樣判決,從而正確接收傳輸信息;短波跳頻網(wǎng)對位同步有較高的要求。因此,位同步問題是短波跳頻通信網(wǎng)中的一個重要問題。

位同步的實現(xiàn)方式很多,如常用的插入導(dǎo)頻法和自同步法等。本文提出了一種新的同步方案——隙同步的概念,并基于TI 公司TMS320C54X系列DSP,采用TMS320匯編語言對該隙同步方案進(jìn)行了硬件仿真和數(shù)值分析。

1 跳頻網(wǎng)位同步原理

在跳頻通信系統(tǒng)中,為了正確接收數(shù)據(jù),接收端必須提供一個作為取樣判決用的定時脈沖序列。該序列的重復(fù)頻率與碼元速率相同,相位與最佳判決時刻一致。因此,跳頻通信系統(tǒng)位同步過程就是指收發(fā)兩地跳頻速率與起始相位的偏差在允許的范圍內(nèi)(通常小于1/2個碼元)提取正確的定時脈沖序列的過程。基于跳頻信號的特點,本文提出了一種隙同步的方法,可以較好解決短波跳頻系統(tǒng)位同步問題。

1.1 隙同步原理

某段時間間隔內(nèi)的跳頻信號波形如圖1所示。

圖1 跳頻信號波形

由圖1可見,相鄰兩個跳頻信號的載頻頻率是不同的,而且兩個載頻交界處的相位通常并不連續(xù),存在突變。隙同步原理就是利用了跳頻信號的這個特點來實現(xiàn)位同步的。

在圖1中,從t0時刻開始提取一個碼元長度的信號,通常在該段信號內(nèi)包含著一個躍變點。若不存在躍變點,即碼元準(zhǔn)確同步,則跳頻信號的幅度譜表現(xiàn)為如圖2所示的單音信號形式。

圖2 同步時跳頻信號幅度譜

若在該段信號內(nèi)存在躍變點,則信號的幅度譜將有所不同,在載頻頻率f0之外還有一些因躍變而產(chǎn)生的頻率分量fi、fj等,這些分量的幅度較之f0要小得多,如圖3所示。

圖3 不同步時跳頻信號幅度譜

由此可見,通過分析信號的幅度譜,可以判斷躍變點的位置。具體而言,首先對信號均勻抽樣得到長度為N的離散信號序列,對該離散序列進(jìn)行快速傅立葉變換(FFT)得到其幅度譜,然后通過比較載頻頻率f0與相位躍變所產(chǎn)生頻率分量的幅度,即可以判斷信號是否同步。若因相位躍變而產(chǎn)生的頻率分量的幅度之和為0,則表明信號已同步;否則,將信號延遲若干點,繼續(xù)作N點FFT,直到信號同步。

以上討論不存在噪聲干擾的理想情況。然而,在實際應(yīng)用中,噪聲時刻存在,這使得信號即使同步了,除載頻f0以外的各頻率分量的能量也不會為0。但是在環(huán)境不十分惡劣的情況下,即當(dāng)信號沒有完全淹沒在噪聲中時,上述原理仍然適用。

1.2 隙同步實現(xiàn)方法

基于上述隙同步原理,本文設(shè)計了如下的同步點尋找方法:

(1) 以t0時刻為起始點取一段跳頻信號,對該段跳頻信號進(jìn)行A/D轉(zhuǎn)換得到離散信號序列。

(2) 從所得信號序列中順序取出一個碼片長度(N點)的信號,進(jìn)行N點FFT運(yùn)算得到該部分信號幅度譜。若該幅度譜中峰值對應(yīng)的頻率分量是約定頻率之一,則將除該頻率分量以外的所有頻率分量的幅度求平方和,并記為a1,然后延遲W點(一般取W使N/W為整數(shù)),順序取出N點信號,重復(fù)以上過程,直到完成N/W次(一個碼片長度)的分析,所得的幅度和依次記為a2,a3,…,aN/W。若該幅度譜中峰值對應(yīng)的頻率分量不是約定的頻率之一,則延遲W點取出后續(xù)的N點信號,重復(fù)上述操作。

(3) 從所得到的{a1,a2,…,aN/W}中取一個最小值ai,并將該點對應(yīng)的時刻(即點序號)記為A1,初步認(rèn)為該時刻即為同步點。A1可以根據(jù)下式計算,即

A1=startpoint+(i-1)×W(1)

(4) 重復(fù)(2)、(3)步驟,進(jìn)一步得到A2、A3值。然后比較A1與A2、A2與A3的距離是否為一個碼元的長度,若是,則表明所取同步點A1正確。

2 隙同步TMS320算法設(shè)計

2.1 隙同步程序

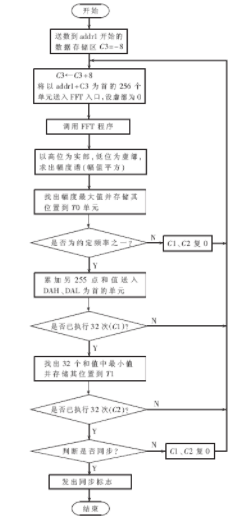

根據(jù)上述隙同步原理和同步點尋找方法,本文采用TI公司TMS320C54X系列DSP芯片進(jìn)行硬件仿真,具體程序流程圖如圖4所示。

圖4 隙同步程序流程圖

為了便于數(shù)值仿真分析,本文將FFT運(yùn)算所用到的余弦表值模擬為跳頻信號的A/D輸入數(shù)據(jù),并規(guī)定一個碼元周期內(nèi)信號抽取點數(shù)為256點。具體輸入數(shù)據(jù)設(shè)計如下:每個頻率的數(shù)值表占用256個存儲單元,存儲順序依次為選定頻率的基頻、倍頻、4倍頻、8倍頻和16倍頻值。

輸入數(shù)據(jù)送入以addr1為首地址的數(shù)據(jù)存儲區(qū)中,偶地址單元存儲實部,奇地址單元存儲虛部。指定C3為延遲指針,用于指定點搜索的起始位置。每次點搜索過程由程序控制將從地址(addr1+C3)開始的256個單元的數(shù)據(jù)送入FFT模塊進(jìn)行幅度譜分析,本文中C3每次移動8個數(shù)據(jù)單元。在判斷峰值頻率是否為約定頻率之一時,通過約定頻率的存儲器位置進(jìn)行判決,本文選取8個約定頻率。

C1和C2為運(yùn)算次數(shù)計數(shù)器。當(dāng)C1=32時,表示已經(jīng)完成一個碼元長度的同步點搜索,可以開始尋找32個和值中的最小值,否則繼續(xù)計算。C2用于計算尋找到的同步點的個數(shù)。本文采用3個同步點輔助判斷,因此,當(dāng)C2=3時即可進(jìn)行同步判決。若同步成功,在程序結(jié)束時將地址大于3000的10個單元置1。

2.2 FFT算法設(shè)計

上述同步點尋找算法是一種基于信號頻譜分析的幅度同步方法,對信號的幅度譜分析主要是利用快速傅立葉變換(FFT)算法完成的。因此,F(xiàn)FT算法的設(shè)計對上述隙同步方法是至關(guān)重要的。

按時間抽取FFT(DIT-FFT)算法是FFT算法的一種。它通過不斷地把時間序列N點x(n)按照序號n奇偶性分解為偶序列和奇序列,并進(jìn)行L=log2N級蝶形運(yùn)算,從而減少乘法和加法的運(yùn)算次數(shù),盡可能地減小運(yùn)算量。

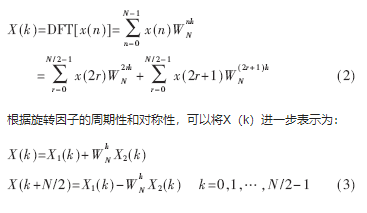

DFT變換式為:

式(3)中,X1(k)和X2(k)分別為偶序列和奇序列的N/2點DFT。由此可見,只要求出0到(N/2-1)區(qū)間內(nèi)的所有X1(k)和X2(k)值,即可求出0到(N-1)內(nèi)所有X(k)值,這就大大節(jié)省了運(yùn)算。

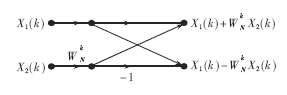

利用蝶形信號流圖,(3)式可以表示為如圖5所示的蝶形運(yùn)算形式。

圖5 蝶形運(yùn)算單元

對于N點的FFT運(yùn)算,共包含有L=log2N級蝶形運(yùn)算。通過不斷對序列進(jìn)行奇偶序列分解,即可以得到N點FFT運(yùn)算的流圖。根據(jù)DIT-FFT算法的特點可知FFT程序設(shè)計有如下三個關(guān)鍵的問題:

(1)輸入序列應(yīng)該是反序輸入,即按照序號n的比特反轉(zhuǎn)值輸入;

(2)與各級蝶形單元相應(yīng)的旋轉(zhuǎn)因子值的確定;

(3)蝶形單元的控制,包括輸入數(shù)據(jù)的讀取、輸出數(shù)據(jù)的存儲及時序控制等。

FFT算法的流程圖如圖6所示。

圖6 FFT算法的流程圖

根據(jù)短波跳頻信號的特點,本文提出了一種新的跳頻通信網(wǎng)位同步方案——隙同步的方法,并基于TI公司TMS320C54X系列DSP,采用TMS320匯編語言對隙同步方案進(jìn)行了硬件實現(xiàn)和分析。

仿真結(jié)果表明:隙同步原理能較好地解決跳頻通信網(wǎng)中接收端的位同步問題,為后續(xù)單元實現(xiàn)正確譯碼奠定了基礎(chǔ)。而且,由于TMS320C54X系列DSP具有運(yùn)算速度快、精度高的特點,采用該方法可以獲得較短的同步時間,有利于提高通信網(wǎng)的性能。

責(zé)任編輯:gt

-

dsp

+關(guān)注

關(guān)注

554文章

8059瀏覽量

350396 -

存儲器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164340 -

仿真

+關(guān)注

關(guān)注

50文章

4124瀏覽量

133983

發(fā)布評論請先 登錄

相關(guān)推薦

TMS320C54x DSP 的cpu和外圍設(shè)備原理 pdf

基于TMS320C54X系列DSP實現(xiàn)跳頻通信網(wǎng)位同步方案

基于TMS320C54x的DSP實驗

TMS320C54x|DSP在OMAP5910上的實現(xiàn)

TMS320C54X DSP實現(xiàn)UART的技術(shù)

TMS320C54X DataSheet

TMS320C54X的LJART串口通信功能

TMS320C54X系列DSP的體系結(jié)構(gòu)學(xué)習(xí)課件免費(fèi)下載

基于TMS320C54X系列DSP實現(xiàn)跳頻通信網(wǎng)位同步方案

基于TMS320C54X系列DSP實現(xiàn)跳頻通信網(wǎng)位同步方案

評論