隨著FPGA的不斷發展,FPGA本身自帶的PCIE硬核的數量越來越多,本文以ZU11EG為例介紹,如何進行對應的硬件引腳分配。

設計目標:ZU11EG FFVC1760封裝,掛載4組NVME,接口為PCIE X4 ,

先我們先對ZU11EG的資源進行分析,在UG1075中我們可以清楚的看到其包含4個PCIE塊,分別位于X0Y2,X0Y3,XIY1,XIY0.

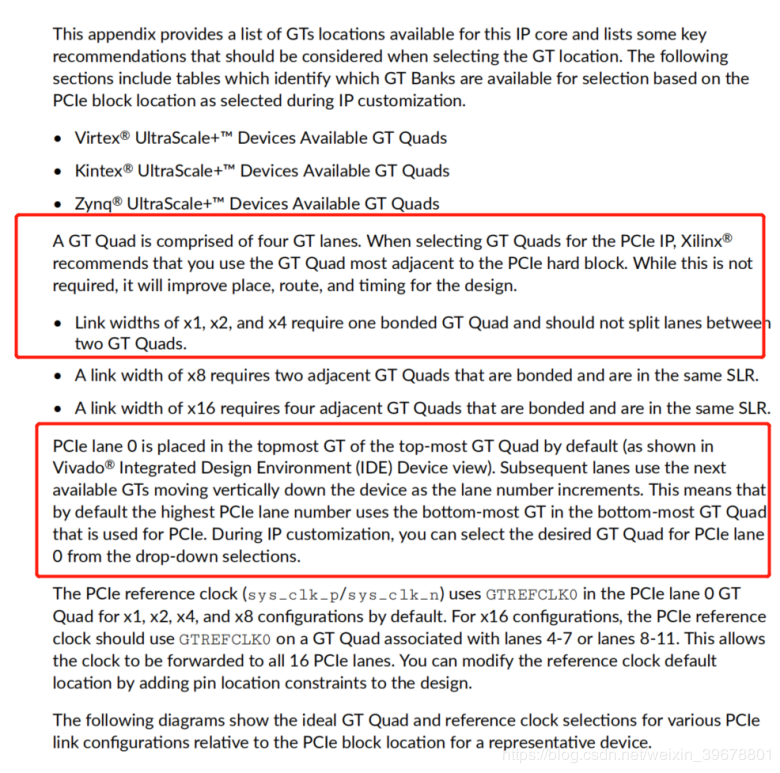

在文檔PG213上我們可以看到如下:

總結上文:在硬件設計引腳分配的時候我們需要知道:

1、一個GT Quad由四個GT車道組成。為PCIe IP選擇GT Quads時,Xilinx建議您在最靠近PCIe硬塊的地方使用GT Quad。雖然這不是必要時,它將改善設計的位置,路線和時間。

2、需要注意PCIE lane 0的位置

3.根據些表格,這些表格根據以下內容確定哪些GT庫可供選擇:IP自定義期間選擇的PCIe塊位置。

那如何驗證自己的分配結果呢?最終在實際使用的時候我們會應用到相關的IP核,最簡單也是最靠譜的方法,是采用vivado新建工程,生成PCIE的IP核進行驗證,如下圖所示,可以清楚的知道對應的那些可用。

在FPGA硬件設計中,引腳分配是最重要的一步,也是最關鍵的一步。

編輯:jq

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606037 -

PCIe

+關注

關注

15文章

1262瀏覽量

83195 -

GT

+關注

關注

0文章

15瀏覽量

24681

原文標題:基于XILINX FPGA的硬件設計總結之PCIE硬件設計避坑

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于Xilinx ZYNQ7000 FPGA嵌入式開發實戰指南

采用Xilinx FPGA的AFE79xx SPI啟動指南

基于Xilinx XCKU115的半高PCIe x8 硬件加速卡

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

XILINX FPGA的硬件設計總結之PCIE硬件設計避坑指南

XILINX FPGA的硬件設計總結之PCIE硬件設計避坑指南

評論