隨著登納德縮放定律在2005年終結以后,大規模數字集成電路的功耗問題以及由功耗問題衍生而來的散熱問題、可靠性問題逐步凸顯出來。因此如何有效降低大規模數字集成電路的功耗成為近10年來大規模數字集成電路所面臨的最重要挑戰之一。

降低功耗的前提是優化設計,而優化設計的前提又是分析到底功耗高在何處。因此,分析功耗是一切的前提。如果學習過數字集成電路與系統設計相關知識的同學應該知道功耗分為靜態功耗和動態功耗兩部分。其中,靜態功耗是由于器件中存在泄漏電流而產生的,只要上電以后就會一直存在。靜態功耗可以表征為: 也就是電源電壓乘以泄漏電流。初看這個公式,相信大家覺得這不是常識嘛。但問題是泄漏電流又是怎么知道的?泄漏電流一般可以表示為:

也就是電源電壓乘以泄漏電流。初看這個公式,相信大家覺得這不是常識嘛。但問題是泄漏電流又是怎么知道的?泄漏電流一般可以表示為: 是不是看著有點暈了?這后面這些亂七八糟的“I ”到底是什么啊……我們就說個最簡單的IDS是是亞閾值泄露電流。

是不是看著有點暈了?這后面這些亂七八糟的“I ”到底是什么啊……我們就說個最簡單的IDS是是亞閾值泄露電流。

當柵極偏置電壓很低時,溝道載流子受源端勢壘的影響,泄露電流較小。當源漏端電壓升高后,源端勢壘降低,導致溝道電流受源漏端電壓影響。看到這里,是不是覺得腦袋已經嗡嗡的了?為了避免大家看不下去而導致選手流失,就不能繼續分析下去了。我們再來看看動態功耗如何計算吧:

是不是一種看完了以后完全不想說話的感覺……如果我們依靠上面的公式來分析各種低功耗設計方案的正確性,那就太費勁了。有沒有一種簡單的分析方法能夠明確我們設計中采用的多電壓域、門控時鐘、動態電壓頻率調節、電源門控等技術是不是有效的降低了功耗,以及是否還有進一步設計優化的空間?這種方法就是不用去直接計算再回頭反饋,而是用“規則”和“狀態”來判斷方法是否有效。

以上提到的低功耗設計方法可以通過UPF(一組TCL命令,所以可以將其簡單視為TCL語言的一個特定領域的子集)語言來描述,事實上UPF可以用在IC設計流程的不同階段并能夠完整的描述功耗設計意圖。在整個低功耗設計中,電源狀態表(Power State Table, PST)可被用來描述各個供電狀態(Supply State)之間的相互關系。通過對PST的靜態分析可以有效檢查Supply State的有效性、冗余性和一致性。進而對整個電源供電網絡的狀態進行檢查優化。

而為方便更多的同學參賽,賽題設置本身降低了相關背景知識的門檻,將賽題抽象為數學算法問題,此外芯華章會提供完整的UPF parser,modeling等相關培訓,有利于參賽者能快速上手解題。

賽題要點解析

那么本題要解決的核心要點是什么呢?我們先來看一下賽題描述:

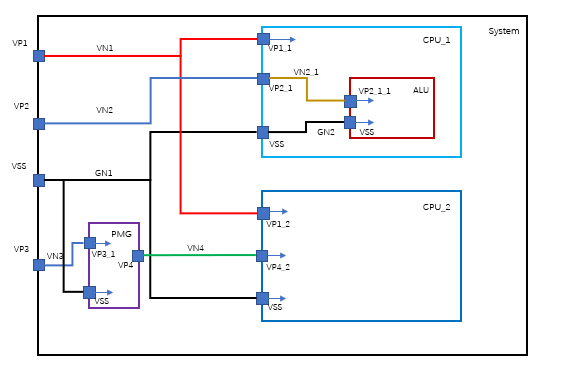

圖1一種電源網絡供電方案圖1展示了一種常見的電源供電網絡設計方案(注:僅作為參考而非實際應用電路)。低功耗設計工程師可以根據功耗設計意圖來定義電路設計中的每一個供電端口(Supply Port)上的供電狀態(Supply State)。

如為上述設計中的VP1, VP2, VSS, VP2, CPU_1/VP1_1, CPU_1/VP2_1, CPU_1/VSS, CPU_1/ALU/VP2_1_1, CPU_1/ALU/VSS, CPU_1/VP1_2, CPU_1/VP4_2, CPU_1/VSS, PMG/VP3_1, PMG/VSS等端口定義供電狀態。可以看出,這是大規模數字集成電路中的一種常見的層次化結構。從最頂層的System到最底層的ALU,劃分出來3個層次。而在每一個層次中又并列了很多模塊。

模塊之間的電源網絡存在著不同的連接方法,層次間的電源網絡又存在包含關系。層次化的方法對于大規模數字集成電路設計具有結構清晰、易于理解的優勢。但是最終電源網絡是一個整體,這種層次化的狀態需要被“展開”為一種平鋪的狀態。如果說層次化是為了便于設計,那么消除層次化就是為了能夠準確分析。因為在真實的電路中并沒有所謂的“層次”,尤其是對于電源網絡而言,連接到同一電源的所有晶體管其實都是這個電源網絡的組成部分而已。因此,進行低功耗分析的第一步自然是將不同的PST進行合并,最終形成一張完整的“大表”。我們可以看到圖1可以用五個PST來描述其供電狀態。

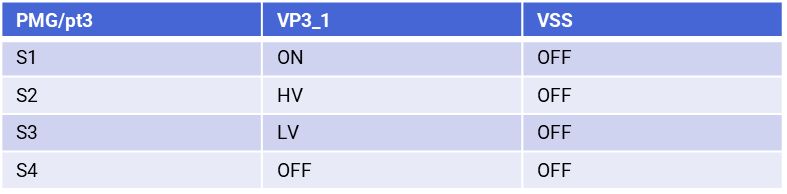

表1. PST of System/PMG

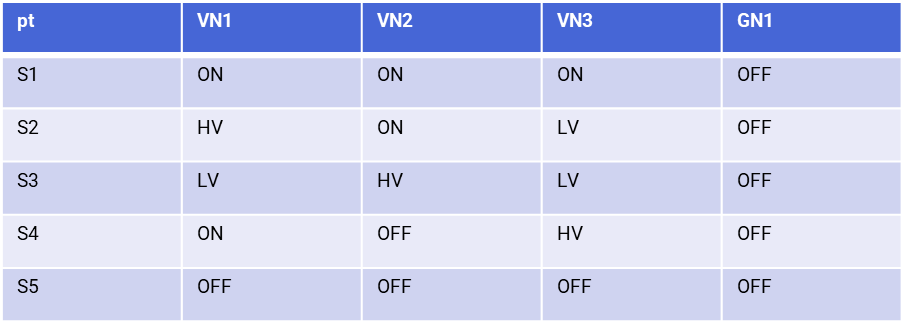

表2. PST of System

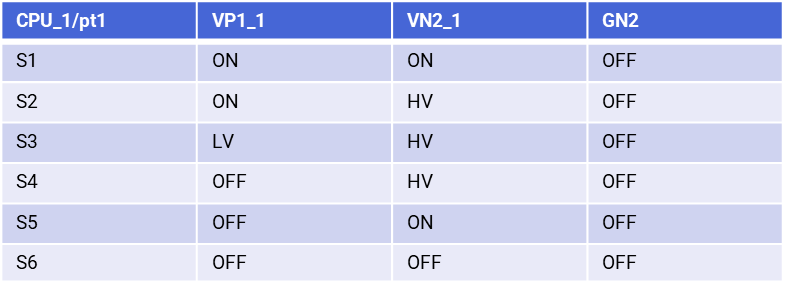

表3. PST of System/CPU_1

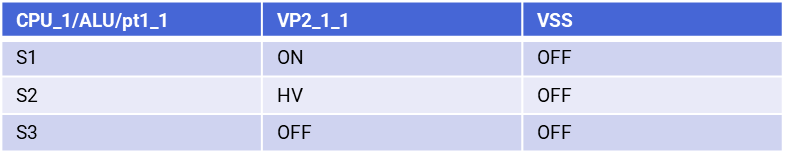

表4. PST of System/CPU_1/ALU

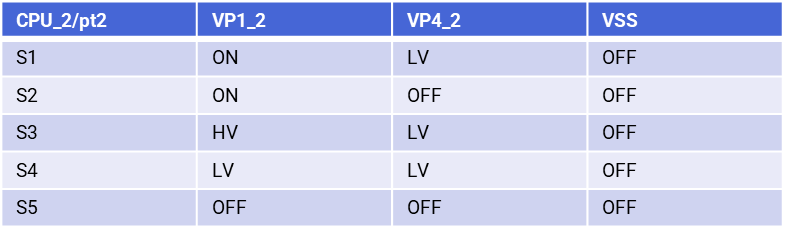

表5. PST of System/CPU_2

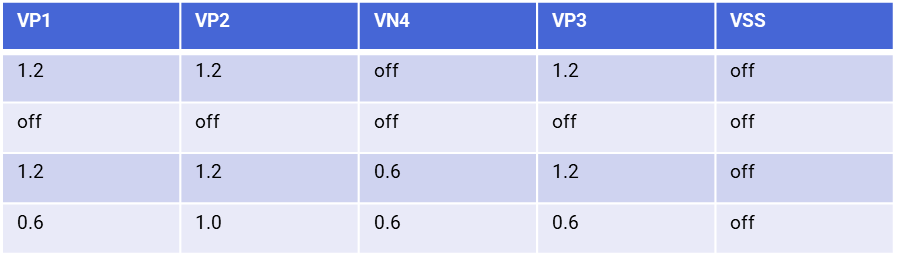

低功耗設計分析器應根據電源供電網絡關系,分析并合并不同設計模塊下的電源狀態表得到供電源(supply source)的PST。最終得到的一張描述整個設計的大表。如在本設計中,應根據表1-5可以得到表6。

表6. 合并后的PST

這樣從最終的表6中,我們可以看到不同模塊中的幾個關鍵性的電源網絡節點的連接情況和供電狀態,進而可以根據連接情況和供電狀態來做低功耗分析。所以直白一點,本次賽題二的核心點就在于不同PST的解析和合并。由于芯華章已經提供了專門的Parser(解析器),各位參賽選手可以把精力集中于“合并”這一件事情。

建議解題步驟

通過對于賽題要點的分析,我們可以發現賽題二其實只做一件事情:如何將不同的PST按照其對應的連接關系合并為單一的、完整的PST。題目按理說難度并不大。但在賽題發布以后,仍然有不少同學認為題目有相當的難度。

經過分析原因后,我們認為可能主要的難點有兩個:首先,除了少部分科研課題和低功耗設計有關的同學外,大部分同學對功耗的成因、計算方法、表針方式等并不是熟悉,對于題目背景的理解有一定的難度;其次,絕大部分同學應該沒有接觸過UPF和PST,由于對其格式不熟悉而產生了畏難情緒。因此大家在解題之前,首先需要解決的就是對于知識背景的進一步熟悉。

尤其是需要對于UPF的用法和PST的格式有足夠的了解。這一點其實并不難做到,因為題目提供了相關的附件以及后續會對這一部分內容重點加強培訓,幫助各位同學盡快熟悉UPF和PST。

在熟悉完UPF和PST以后各位同學應該以一個示范性的設計入手,盡快的走通從PST解析到PST合并的全部流程。在這個過程中必然涉及到部分的程序設計、函數調用、數據格式轉換等問題,而解決這個問題的過程本身又是對于賽題的進一步熟悉和對UPF以及PST的更進一步的熟悉。再完成以上兩步以后,參賽同學可以針對題目要求逐一核對功能是否完成。

在確保功能完備的基礎上利用芯華章提供的測試集,不斷的加強對所編寫程序的檢驗。除了檢驗一般性的bug以外,還繼續優化程序運行的速度以及占用的空間。最終達耗時更好、占用內存更少的目的。以上解題思路的本質是從簡單到復雜,從確保功能到性能優化。符合我們開發軟件的一般規律,也符合我們工程研究的一般進程。

其它注意事項

大家在解題時還需要注意以下幾點:

不要輕易放棄,題目本身難度不大,但是前期的知識準備要花點時間;

一定要積極參加培訓,很多知識其實一點就透,但是在自己沒有相關背景的情況下學習還是有一定的挑戰性;

要遵循循序漸進、從易到難的解題思路,切不可貪大求全讓自己陷入到重重迷霧之中。

最后,預祝各位同學發揮出自己的水平,取得良好的成績。

責任編輯:haq

-

集成電路

+關注

關注

5392文章

11624瀏覽量

363192 -

TCL

+關注

關注

10文章

1742瀏覽量

88879 -

分析器

+關注

關注

0文章

93瀏覽量

12557

原文標題:芯華章賽題解析:數字集成電路低功耗設計分析器

文章出處:【微信號:gh_387c27f737c1,微信公眾號:英諾達EnnoCAD】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

新思科技攜手深圳大學推動集成電路設計領域發展

東芝TC7WZ74FK的特點與應用探討

74VHC00FT CMOS數字集成電路硅單片英文手冊

音響集成電路是數字集成電路嗎

TC7WZ74FK CMOS數字集成電路硅單片規格書

ic 電子元器件類型有哪些?

如何利用低功耗設計技術實現超大規模集成電路(VLSI)的電源完整性?

數字集成電路低功耗設計分析器

數字集成電路低功耗設計分析器

評論