經(jīng)典面試題:建立時間與保持時間

我曾背過這個答案N多遍,但是依然沒有理解。

直到...

一、同步電路設(shè)計

同步電路系統(tǒng)設(shè)計將系統(tǒng)狀態(tài)的變化與時鐘信號同步,并通過這種理想化的方式降低電路設(shè)計難度。同步電路設(shè)計是FPGA設(shè)計的基礎(chǔ)。

但是伴隨著集成電路的微縮化和大規(guī)模化,同步式電路的一些問題也顯現(xiàn)出來。有研究提出了基于異步電路實現(xiàn)FPGA的思路。這個后面再談。

二、觸發(fā)器

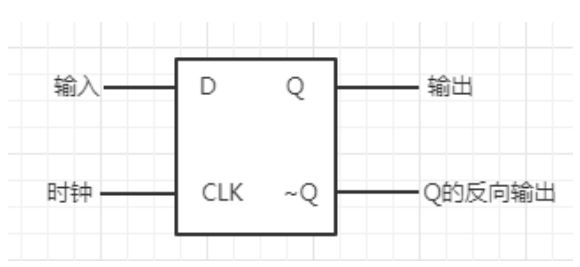

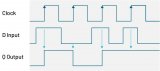

觸發(fā)器(Flip Flip,F(xiàn)F)是一種只能存儲1個二進(jìn)制位(bit)的存儲單元,可以用作時序邏輯電路的記憶元件。FPGA邏輯單元的D觸發(fā)器(DFF)就是一種在時鐘的上升沿將輸入信號的變化傳送至輸出的邊沿D觸發(fā)器。DFF的符號和真值表如下圖所示:

2.1 D觸發(fā)器結(jié)構(gòu)

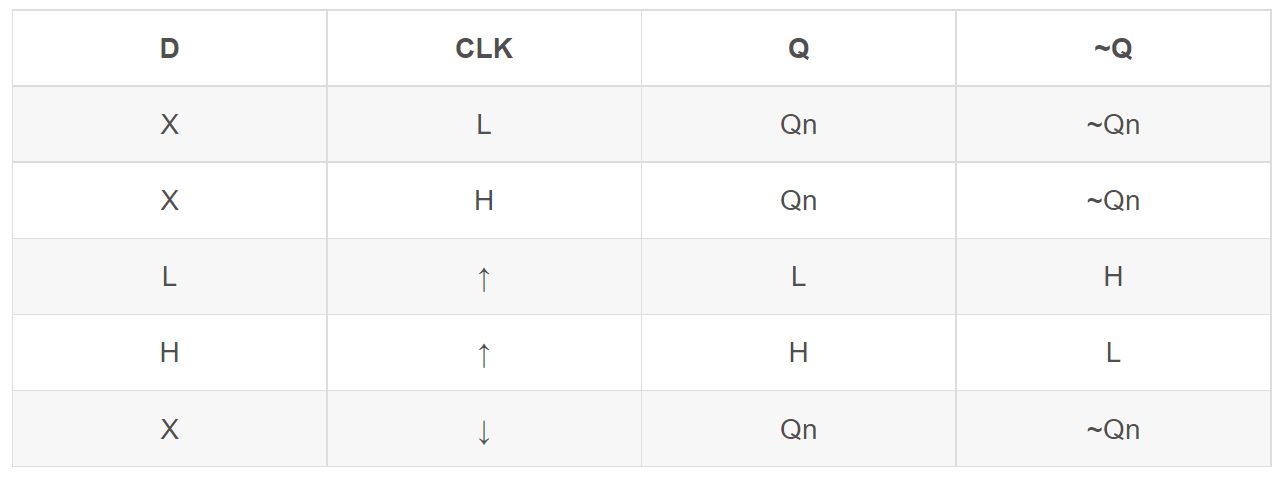

CMOS傳輸門構(gòu)成的D邊沿觸發(fā)器電路如下圖所示:

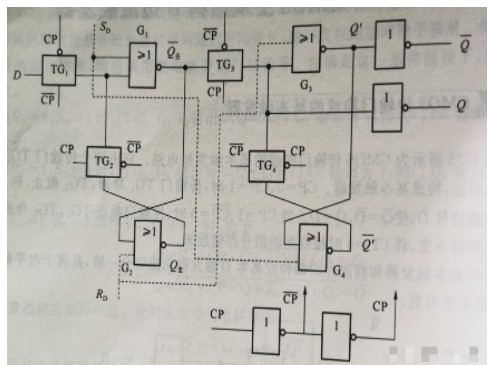

CMOS工藝下的D-FF結(jié)構(gòu)如下圖所示:

先由傳輸門和兩個反相器組成一個循環(huán)電路(鎖存器),再有前后兩級鎖存器按主從結(jié)構(gòu)連接而成。這里的傳輸門起開關(guān)作用,隨著CLK的狀態(tài)切換開關(guān)。只看輸出的話,前級鎖存器的值會隨著時鐘輸入的變化井然有序的傳入后級鎖存器。為了防止時鐘信號變化時輸入信號發(fā)生冒險,從而使輸入數(shù)據(jù)穩(wěn)定的進(jìn)入前級鎖存器,前級鎖存器的時鐘相位應(yīng)與輸入數(shù)據(jù)的電路時鐘相位相反。

2.2 D觸發(fā)器工作原理

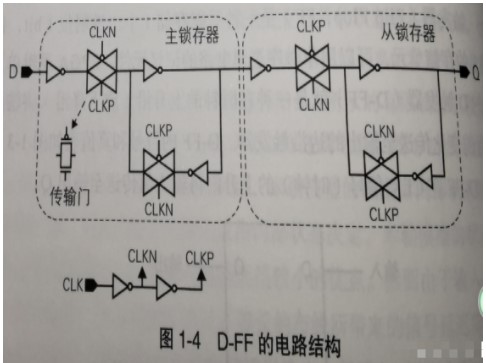

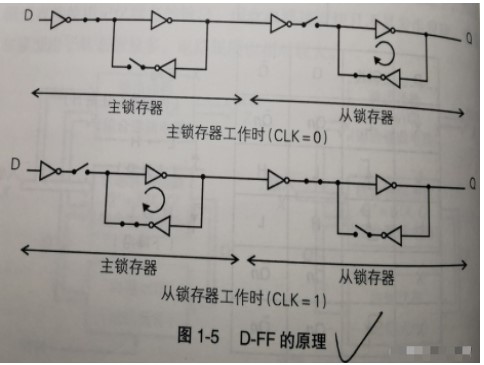

D-FF的工作原理,如下圖所示:

當(dāng)CLK=0時(主鎖存器工作),位于前級的主鎖存器將輸入D的值保存進(jìn)來,后級的從鎖存器將維持上一個時鐘周期的數(shù)據(jù)。由于此時前級與后級的反相器環(huán)路之間的傳輸門是關(guān)閉狀態(tài),所以前級的信號不會傳到后級。

當(dāng)CLK=1時(從鎖存器工作),前級主鎖存器的值將會傳到后級,同時輸入D的信號將會被隔離在外。此時如果前級反相器環(huán)路中的信號沒有循環(huán)一圈以上,就會出現(xiàn)如下圖所示的在0和1之間搖擺的中間電位,這就是所謂的亞穩(wěn)態(tài)。

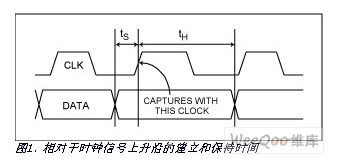

三、建立時間和保持時間

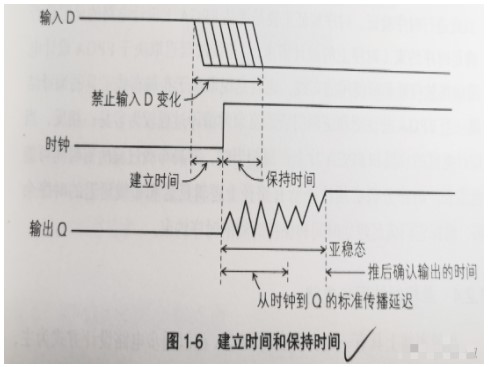

由于亞穩(wěn)態(tài)時間比延遲時間長,在該階段讀取數(shù)據(jù)可能會引起錯誤,所以我們引入建立時間(setup time)來約束在時鐘上升沿到來之前輸入D保持穩(wěn)定的時間。

當(dāng)CLK=1時,如果輸入D在傳輸門關(guān)閉之前就發(fā)生變化,那么本該在下一周期讀取的數(shù)據(jù)就會提前進(jìn)入鎖存器,從而引起反相器環(huán)路振蕩或產(chǎn)生亞穩(wěn)態(tài)。因此在CLK=1之后也需要輸入D維持一定的時間,我們稱之為保持時間(hold time)約束。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606046 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2003瀏覽量

61351 -

同步電路

+關(guān)注

關(guān)注

1文章

60瀏覽量

13350

發(fā)布評論請先 登錄

相關(guān)推薦

總結(jié)了8個常見的知識點

ADC采樣保持過程的具體時間要如何確定?

DAC81408的建立時間為12uS,如何理解數(shù)據(jù)手冊中的12uS建立時間這個參數(shù)呢?

DAC7811想要實現(xiàn)持續(xù)1us的100mA電流源,但DAC建立時間都有1us,如何解決?

請問如何確認(rèn)dac7811的電壓建立時間是否滿足0.2us?

使用NTP,該如何同步時間?一文詳解!

PGA281建立時間過長怎么解決?

求助,關(guān)于INA333波形建立時間的疑問求解

用混合信號示波器識別建立和保持時間違規(guī)

請問如何增加ESP32-S2以太網(wǎng)SPI接口的CS建立時間?

FPGA 高級設(shè)計:時序分析和收斂

STM32F302K8U6和STM32G431中內(nèi)置的運(yùn)放 建立時間是多長?

高速數(shù)模轉(zhuǎn)換器(DAC)的建立和保持時間

詳解FPGA中建立時間與保持時間

詳解FPGA中建立時間與保持時間

評論