1、前言

可能很多FPGA初學者在剛開始學習FPGA設計的時候(當然也包括我自己),經(jīng)常聽到類似于”這個信號需要打一拍、打兩拍(寄存),以防止亞穩(wěn)態(tài)問題的產(chǎn)生“這種話,但是對這個打拍和亞穩(wěn)態(tài)問題還是一知半解,接下來結(jié)合一些資料談下自己的理解。

2、觸發(fā)器的建立時間和保持時間

時序電路的基礎是觸發(fā)器(FF、Flip-Flop),觸發(fā)器正常工作需要滿足建立時間和保持時間的時序要求。

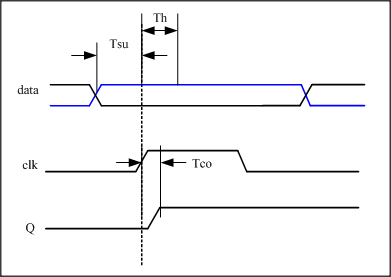

建立時間(Tsu:set up time)

是指在觸發(fā)器的時鐘信號上升沿到來以前,數(shù)據(jù)穩(wěn)定不變的時間,如果建立時間不夠,數(shù)據(jù)將不能在這個時鐘上升沿被穩(wěn)定的打入觸發(fā)器,Tsu就是指這個最小的穩(wěn)定時間

保持時間(Th:hold time)

是指在觸發(fā)器的時鐘信號上升沿到來以后,數(shù)據(jù)穩(wěn)定不變的時間,如果保持時間不夠,數(shù)據(jù)同樣不能被穩(wěn)定的打入觸發(fā)器,Th就是指這個最小的保持時間

3、亞穩(wěn)態(tài)

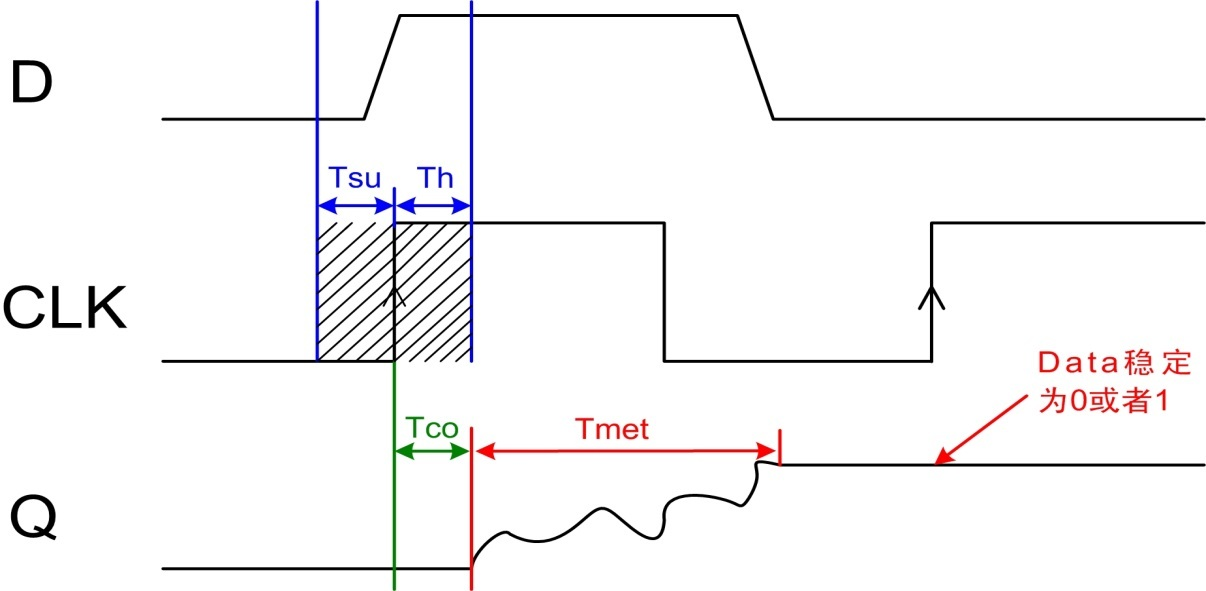

亞穩(wěn)態(tài) (Metastability):如果數(shù)據(jù)傳輸中不滿足觸發(fā)器的Tsu和Th不滿足,就可能產(chǎn)生亞穩(wěn)態(tài),此時觸發(fā)器輸出端Q在有效時鐘沿之后比較長的一段時間處于不確定的狀態(tài),在這段時間里Q端在0和1之間處于振蕩狀態(tài),而不是等于數(shù)據(jù)輸入端D的值。這段時間稱為決斷時間Tmet(resolution time)。經(jīng)過resolution time之后Q端將穩(wěn)定到0或1上,但是穩(wěn)定到0或者1,是隨機的,與輸入沒有必然的關系。

亞穩(wěn)態(tài)振蕩時間 Tmet 關系到后級寄存器的采集穩(wěn)定問題,Tmet 影響因素包括:器件 的生產(chǎn)工藝、溫度、環(huán)境以及寄存器采集到亞穩(wěn)態(tài)里穩(wěn)定態(tài)的時刻等。甚至某些特定條 件,如干擾、輻射等都會造成 Tmet 增長。

只要系統(tǒng)中有異步元件,亞穩(wěn)態(tài)就是無法避免的,亞穩(wěn)態(tài)主要發(fā)生在異步信號檢測、跨時鐘域信號傳輸以及復位電路等常用設計中。由于產(chǎn)生亞穩(wěn)態(tài)后,寄存器Q端輸出在穩(wěn)定下來之前可能是毛刺、振蕩、固定的某一電壓值。在信號傳輸中產(chǎn)生亞穩(wěn)態(tài)就會導致與其相連其他數(shù)字部件將其作出不同的判斷,有的判斷到“1”有的判斷到“0”,有的也進入了亞穩(wěn)態(tài),數(shù)字部件就會邏輯混亂。

4、如何防止亞穩(wěn)態(tài)

首先,在同步系統(tǒng)中,輸入信號總是系統(tǒng)時鐘同步,能夠達到寄存器的時序要求,所以亞穩(wěn)態(tài)肯定不會發(fā)生。在異步系統(tǒng)的信號輸出過程中,如果無法滿足建立時間和保持時間的要求則會發(fā)生亞穩(wěn)態(tài)。

預防亞穩(wěn)態(tài)的方法就是將輸入信號(單bit信號)打拍,也就是在要使用的時鐘域下,將信號寄存。

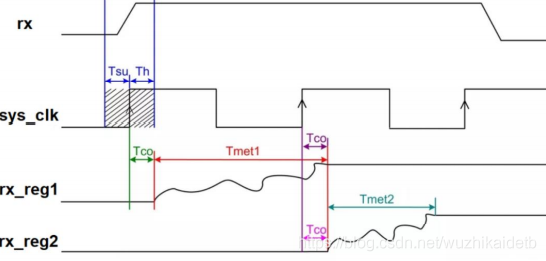

rx是相對于時鐘域sys_clk的異步信號,rx_reg1、rx_reg2分別是rx在時鐘域sys_clk打一拍(寄存一次、可以理解為延遲一個時鐘周期 )、打兩拍(寄存一兩次、可以理解為延遲兩個時鐘周期)的信號。可以看到rx_reg1可能還存在低概率的亞穩(wěn)態(tài)現(xiàn)象,當然rx_reg2雖然在示意圖里是穩(wěn)定的,不過實際過程中也仍然存在亞穩(wěn)態(tài)發(fā)生的概率。

單比特信號從慢速時鐘域同步到快速時鐘域需要使用打兩拍的方式消除亞穩(wěn)態(tài)。 第一級寄存器產(chǎn)生亞穩(wěn)態(tài)并經(jīng)過自身后可以穩(wěn)定輸出的概率為 70%~80%左右,第二級寄存 器可以穩(wěn)定輸出的概率為 99%左右,后面再多加寄存器的級數(shù)改善效果就不明顯了,所以 數(shù)據(jù)進來后一般選擇打兩拍即可。這里注意,該方法僅僅適用單比特信號從慢速時鐘域同步到快速時鐘域,單比特信號從快速時鐘域同步到慢速時鐘域還僅僅使用打兩拍的方式則會漏采數(shù)據(jù)。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21796瀏覽量

606011 -

觸發(fā)器

+關注

關注

14文章

2003瀏覽量

61347 -

亞穩(wěn)態(tài)

+關注

關注

0文章

46瀏覽量

13327

發(fā)布評論請先 登錄

相關推薦

PCM5142如何在FPGA中通過SPI配置寄存器?

FPGA Verilog HDL代碼如何debug?

FPGA Verilog HDL有什么奇技巧?

單穩(wěn)態(tài)觸發(fā)器穩(wěn)態(tài)是什么狀態(tài)的

雙穩(wěn)態(tài)觸發(fā)器是什么耦合雙穩(wěn)態(tài)電路

雙穩(wěn)態(tài)觸發(fā)器的類型有哪些

減小系統(tǒng)穩(wěn)態(tài)誤差的方法有哪些?

FPGA異步信號處理方法

憶阻器誘導的超混沌、多渦旋和極端多穩(wěn)態(tài)小數(shù)階HNN:鏡像加密和FPGA實現(xiàn)

CPU中寄存器的用途

數(shù)字電路中的亞穩(wěn)態(tài)是什么

深入理解 FPGA 的基礎結(jié)構(gòu)

如何根據(jù)自己設計中的寄存器配置總線定義來生成一套寄存器配置模版

如何理解FPGA設計中的打拍(寄存)和亞穩(wěn)態(tài)

如何理解FPGA設計中的打拍(寄存)和亞穩(wěn)態(tài)

評論