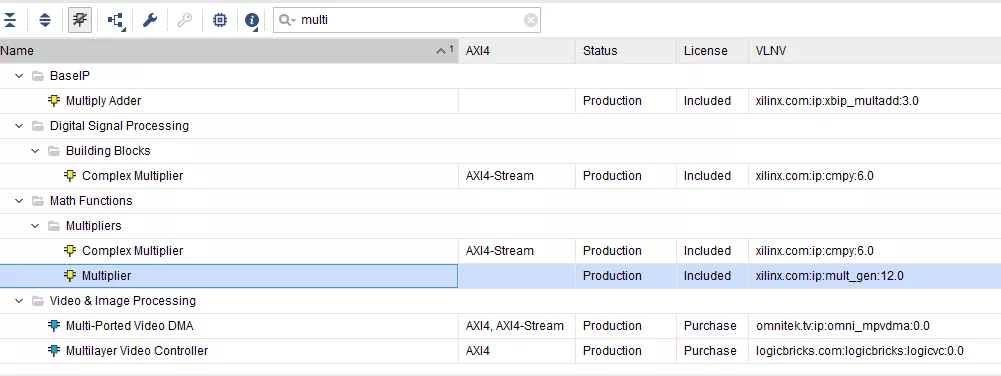

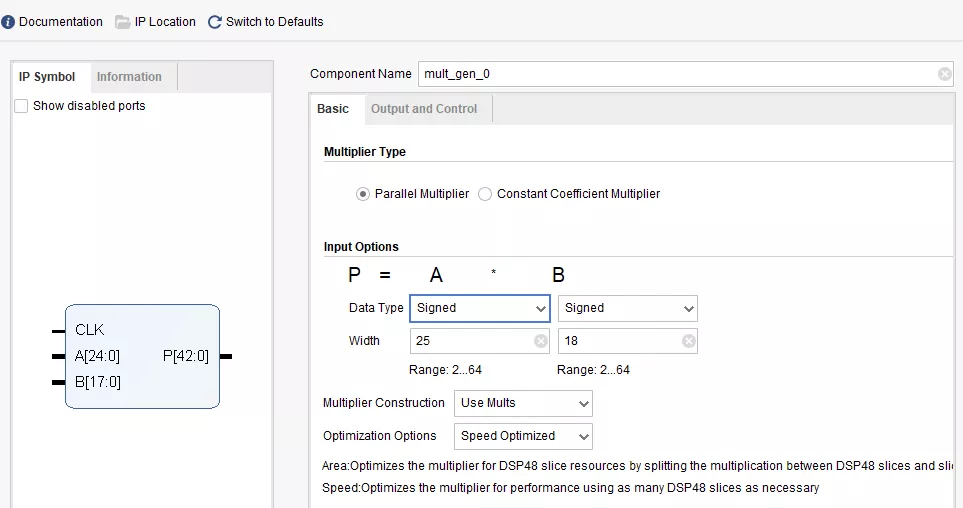

?FPGA中乘法器是很稀缺的資源,但也是我們做算法必不可少的資源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我們可以通過調IP Core的方式或者原語的方式來進行乘法操作。在里面可以設置有符號還是無符號數乘法。

當然,我們也可以直接使用*符合來進行乘法,對于無符號的乘法

reg [7:0] ubyte_a;

reg [7:0] ubyte_b;

(* *)

output reg[15:0] u_res;

always @ ( posedge clk ) begin

if(rst)

u_res else

u_res end

?有符號乘法可以在Verilog中使用signed來標注。

reg signed [7:0] byte_a;

reg signed [7:0] byte_b;

(* *)

reg signed [15:0] res;

always @ ( posedge clk ) begin

if(rst)

res else

res end

當然我們也要理解有符號數乘法的原理,其實就是擴位乘法,把高位都補充為符號位。

有符號數乘法:

reg [7:0] ubyte_a;

reg [7:0] ubyte_b;

(* *)

reg [15:0] res_manul;

always @ ( posedge clk ) begin

if(rst)

res_manul else

res_manul end

關于乘法輸出的位寬,我們知道,兩個8bits的無符號數乘法,結果的位寬是16bits,但對于兩個8bits有符號數的乘法,只要兩個數不同時為-128,即二進制0b1000_0000,那么輸出結果的高兩位都是符號位,我們只需要取低15bits即可。因此,如果我們可以保證兩個輸入的乘數不會同時為有符號數所能表示的負數最小值,那么乘法結果的高兩位都是符號位,只取其中一位即可。

審核編輯:符乾江

-

FPGA

+關注

關注

1630文章

21797瀏覽量

606019 -

乘法器

+關注

關注

8文章

206瀏覽量

37193

發布評論請先 登錄

相關推薦

ADS8688分別設置0 to 1.25 × VREF和±1.25 × VREF采樣范圍時,得到的16位數據是按照有符號數還是無符號數進行轉換?

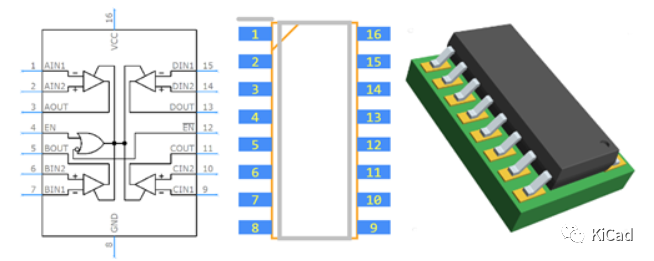

原理圖符號和PCB封裝有什么不同?

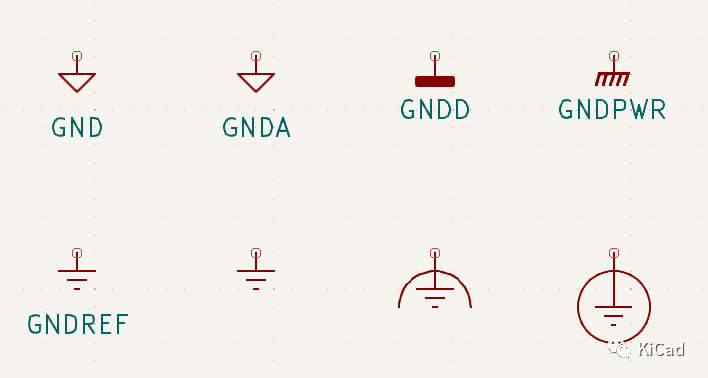

KiCad中不同GND符號的含義及應用

求助,LMX2572LP參考時鐘路徑中的乘法器MULT的輸入頻率范圍問題求解

FPGA Verilog HDL有什么奇技巧?

LM70 SPI/MICROWIRE 10位帶符號數字溫度傳感器數據表

LM12454/LM12458/LM12H458 12位符號數據采集系統數據表

FPGA中的有符號數乘法說明

FPGA中的有符號數乘法說明

評論