數字濾波器

數字濾波器從實現結構上劃分,有FIR和IIR兩種。FIR的特點是:線性相位、消耗資源多;IIR的特點是:非線性相位、消耗資源少。由于FIR系統的線性相位特點,設計中絕大多數情況都采用FIR濾波器。

線性相位系統的意義,這里的線性相位指的是在設計者關心的通帶范圍內,LTI系統滿足線性相位要求:

從延時的角度看:保證了輸入信號的相位響應是線性的,即保證了輸入信號的延時特性。

從相位的角度看:輸入的各頻率成分的信號之間,相對相位是固定的。通過線性相位系統后,相對相位關系保持不變。

對于關心相位的系統,比如調制解調系統,需要使用FIR濾波器;對于只關心頻率成分的系統,比如只是提取某一頻率分量,為了節省資源,使用IIR濾波器即可。

FIR濾波器

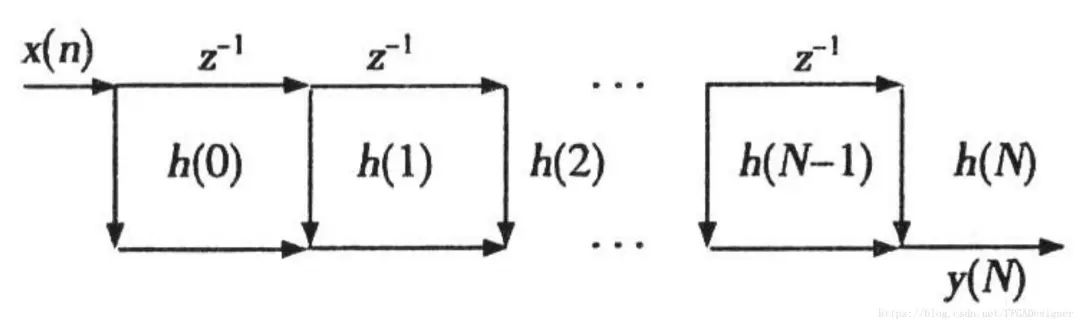

FIR的最大特點就是其系統響應 h(n)是一個N點的有限長序列,FIR的輸出y(n)本質上就是輸入信號x(n)和h(n)的卷積(根據傅里葉變換性質,時域卷積等于頻域相乘,因此卷積相當于篩選頻譜中的各頻率分量的增益倍數,某些頻率分量保留,某些頻率分量衰減,從而實現濾波效果)。FIR在實現上的本質是帶抽頭延遲的加法器和乘法器的組合,每一個乘法器對應一個系數。

由理論知識可知,只有當FIR的h(n)對稱時,FIR濾波器才具有線性相位特性。使用MATLAB等工具設計FIR時,得到的h(n)也都是具有對稱性的。

FIR濾波器的實現結構主要有直接型、級聯型、頻率取樣型、格型四種。其中最適合FPGA實現的是直接型。“直接”是指直接由卷積公式得到:

由上圖可知,n階FIR濾波器就需要n個乘法器。如果設計的是線性相位FIR,則h(n)是對稱的,利用對稱性可以節省一半的乘法器。

FIR濾波器的設計方法有窗函數法、頻率取樣法、等波紋切比雪夫逼近法(也叫最優設計法)等等。以上所有的理論知識點在任意一本數字信號處理課本中都有詳細的推論,本文節省篇幅不再贅述。

MATLAB設計

雖然Quartus和Vivado的FIR IP核中都提供了設計FIR濾波器的功能,但遠沒有MATLAB設計便捷和強大。設計中通常都是在MATLAB中設計好FIR的單位脈沖響應h(n),或者說濾波器系數,量化后應用到FPGA設計中。

MATLAB提供了基于窗函數設計法的fir1函數、設計任意響應濾波器的fir2函數、最優設計法的firpm函數,以及兩個應用程序包“Filter Builder”和“Filter Design&Analysis”,后者通常也被稱作FDATOOL。現在最受歡迎的設計方式恐怕就是使用FDATOOL工具,功能強大、界面便捷,且可以直接導出xilinx公司IP核所需的coe文件。

本系列主要是講述FPGA設計,不詳細討論上述函數及工具的使用,具體情況可以的MATLAB的help中查詢。(Ps:博主目前的幾個系列都處于開篇階段,篇幅不多,暫未成體系,目前不再開新坑,等后期應該會出一個“MATLAB數字信號處理系列”)

FPGA設計

從MATLAB到FPGA最重要的工作便是濾波器系數的量化。現在的計算機大多都是64位的,然而為了節省資源,FPGA中進行如此高位寬的運算步進浪費資源而且也沒有必要。在MATLAB中將濾波器系數量化為指定位寬,會改變濾波器的頻率特性,因此需要做好仿真,確定量化后的系數也能滿足FIR的設計需求。

由上節可知FPGA最方便實現的是直接型結構FIR,實現時可以采用并行結構、串行結構、分布式結構,也可以直接使用Quartus和Vivado提供的FIR IP核。本篇先介紹并行FIR濾波器的Verilog設計。設計參考自杜勇老師的《數字濾波器的MATLAB與FPGA實現》。本設計將在Vivado環境下進行仿真。

使用MATLAB設計一個2kHz采樣,500Hz截止的15階低通濾波器(h(n)長度為16),量化位數為12bit,輸入信號位寬也為12bit。Verilog設計代碼如下。

模塊接口:

module Xilinx_FIR_Guide_liuqi

(

input rst, //復位信號,高電平有效

input clk, //FPGA系統時鐘,頻率為2kHz

input signed [11:0] Xin, //數據輸入頻率為2khZ

output signed [28:0]Yout //濾波后的輸出數據

);

輸出信號的29bit位寬是全分辨率輸出,沒有截位。“并行”FIR指的是多個乘法器并行地進行濾波器系數與輸入數據之間的乘法計算,因此代碼中我們需要緩存16個數據:

reg signed[11:0] Xin_Reg[15:0]; //[11:0]指單數據12bit位寬;[15:0]指共有16個數據

reg [3:0] i,j;

always @(posedge clk or posedge rst)

if (rst)

//初始化寄存器值為0

begin

for (i=0; i<15; i=i+1)

Xin_Reg[i]=12'd0;

end

else

begin

for (j=0; j<15; j=j+1)? //每個時鐘移位一個數據

Xin_Reg[j+1] <= Xin_Reg[j];

Xin_Reg[0] <= Xin;

end

由FIR系數的對稱性可知,16個系數只需要8個乘法器即可,因此應該將對稱系數多對應的輸入數據相加:

reg signed [12:0] Add_Reg[7:0];

always @(posedge clk or posedge rst)

if (rst)

//初始化寄存器值為0

begin

for (i=0; i<8; i=i+1)

Add_Reg[i]=13'd0;

end

else

begin

for (i=0; i<8; i=i+1)? ?//對稱系數相加

Add_Reg[i]={Xin_Reg[i][11],Xin_Reg[i]}+{Xin_Reg[15-i][11],Xin_Reg[15-i]};

end

由于加法會增加一個bit位寬,因此相加結構擴充為13bit。由于輸入數據為二進制補碼帶符號數,因此在相加前需要先使用Verilog中的拼接運算符{}擴展符號位到最高位。接下來例化8個乘法器IP核進行乘法運算:

wire signed [11:0] coe[7:0] ; //濾波器為12比特量化數據

wire signed [24:0] Mout[7:0]; //乘法器輸出為25比特數據

assign coe[0]=12'h000;

assign coe[1]=12'hffd;

assign coe[2]=12'h00f;

assign coe[3]=12'h02e;

assign coe[4]=12'hf8b;

assign coe[5]=12'hef9;

assign coe[6]=12'h24e;

assign coe[7]=12'h7ff;

mult_gen_0Umult0 (

.CLK (clk),

.A (coe[0]),

.B (Add_Reg[0]),

.P (Mout[0]));

mult_gen_0Umult1 (

.CLK (clk),

.A (coe[1]),

.B (Add_Reg[1]),

.P (Mout[1]));

mult_gen_0Umult2 (

.CLK (clk),

.A (coe[2]),

.B (Add_Reg[2]),

.P (Mout[2]));

mult_gen_0Umult3 (

.CLK (clk),

.A (coe[3]),

.B (Add_Reg[3]),

.P (Mout[3]));

mult_gen_0Umult4 (

.CLK (clk),

.A (coe[4]),

.B (Add_Reg[4]),

.P (Mout[4]));

mult_gen_0Umult5 (

.CLK (clk),

.A (coe[5]),

.B (Add_Reg[5]),

.P (Mout[5]));

mult_gen_0Umult6 (

.CLK (clk),

.A (coe[6]),

.B (Add_Reg[6]),

.P (Mout[6]));

mult_gen_0Umult7 (

.CLK (clk),

.A (coe[7]),

.B (Add_Reg[7]),

.P (Mout[7]));

12bit的濾波器系數與13bit的輸入信號數據相乘結果為25bit。乘法結果累加即為濾波器的輸出結果:

reg signed [28:0] sum;

reg signed [28:0] yout;

reg [3:0] k;

always @(posedge clk or posedge rst)

if (rst)

begin

sum = 29'd0;

yout <= 29'd0;

end

else

begin

yout <= sum;

sum = 29'd0;

for (k=0; k<8; k=k+1)

sum = sum+Mout[k]; //相加輸出結果

end

assign Yout = yout;

8個25bit的數相加,結果可能擴展到29bit,這也是全分辨率輸出的結果。可以看到并行結構的FIR乘法、加法運算都是在一個時鐘內完成,因此每個時鐘都能獲得一個輸出。

仿真與工程下載

使用MATLAB生成一個200Hz+800Hz的混合頻率信號,寫入txt文件,再生成一個噪聲信號寫入txt文件。

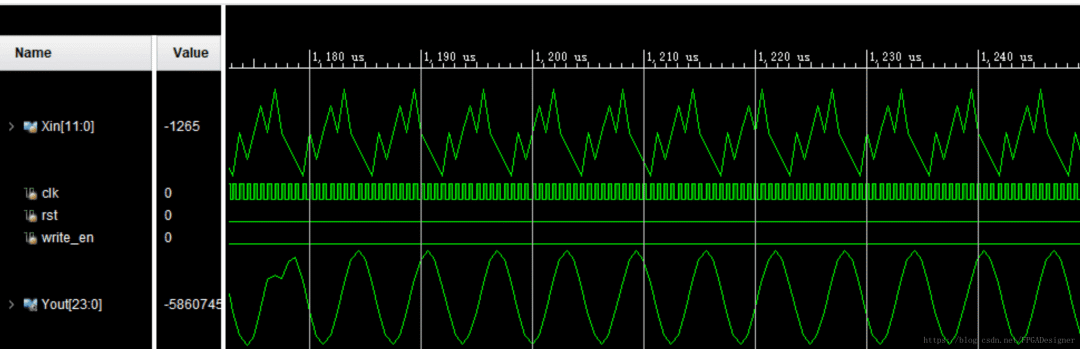

對正弦信號的濾波如下圖所示:

明顯看到經過500Hz低通濾波器濾波后,輸入的200Hz+800Hz信號只剩下200Hz的頻率分量。

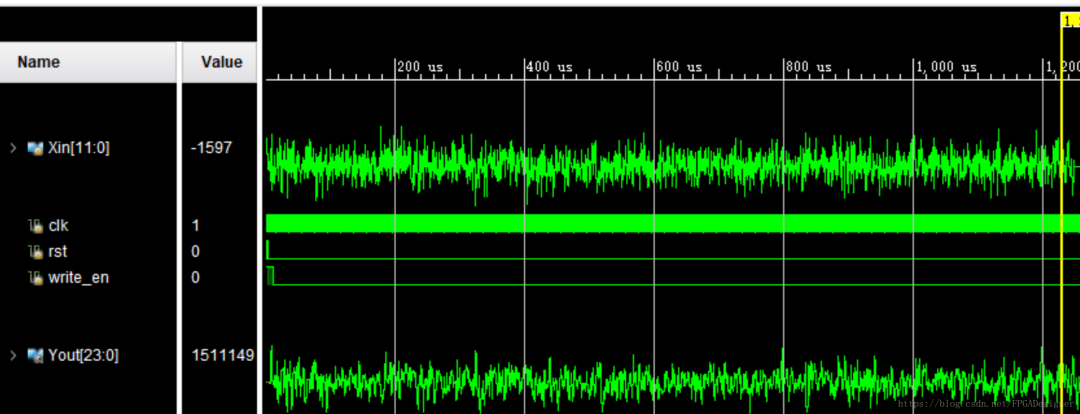

對噪聲信號的濾波如下圖所示:

可以看到噪聲經過濾波后的頻率分布情況明顯少于濾波前

原文標題:FPGA-學習并行FIR濾波器Verilog設計

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605973 -

數字濾波器

+關注

關注

4文章

270瀏覽量

47092 -

Verilog

+關注

關注

28文章

1351瀏覽量

110387 -

fir濾波器

+關注

關注

1文章

95瀏覽量

19092

原文標題:FPGA-學習并行FIR濾波器Verilog設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于MATLAB和Quartus II 的FIR濾波器設計與

基于MATLAB與QUARTUS II的FIR濾波器設計與驗

基于MATLAB與QUARTUS II的FIR濾波器設計與驗

基于MATLAB及FPGA的FIR低通濾波器的設計

基于MATLAB與FPGA的FIR濾波器設計與仿真

FIR濾波器的FPGA設計與實現

并行FIR濾波器MATLAB與FPGA實現

FIR濾波器的MATLAB與FPGA設計

FIR濾波器的MATLAB與FPGA設計

評論