幾乎所有的芯片設計、芯片驗證工程師,每天都在和VCS打交道,但是由于驗證環境的統一化管理,一般將不同的編譯仿真選項集成在一個文件里,只需要一兩個人維護即可。所以大部分人比較少有機會去深入地學習VCS的仿真flow。基于此,本文將介紹VCS仿真的兩種flow,概述這兩種flow分別做了哪些事!

VCS是一個高性能、高容量的編譯代碼仿真器,它將高級抽象的驗證技術集成到一個開放的本地平臺中。它能夠分析、編譯和編譯Verilog、VHDL、SystemVerilog和OpenVera所描述的design,并且還提供了一組仿真和調試功能來驗證design,這些特性提供了源代碼級debug和仿真結果。支持原生測試平臺、SystemVerilog、驗證規劃、覆蓋率分析和收斂。

除了標準Verilog、VHDL和混合HDL和SystemVerilog編譯和仿真功能,VCS包括以下集成的功能和工具集:

SystemC

Verdi

Unified Command-lineInterface (UCLI)

Built-In CoverageMetrics

DirectC Interface

VCS還可以與第三方工具集成,如Specman、Denali和其他加速和仿真系統。

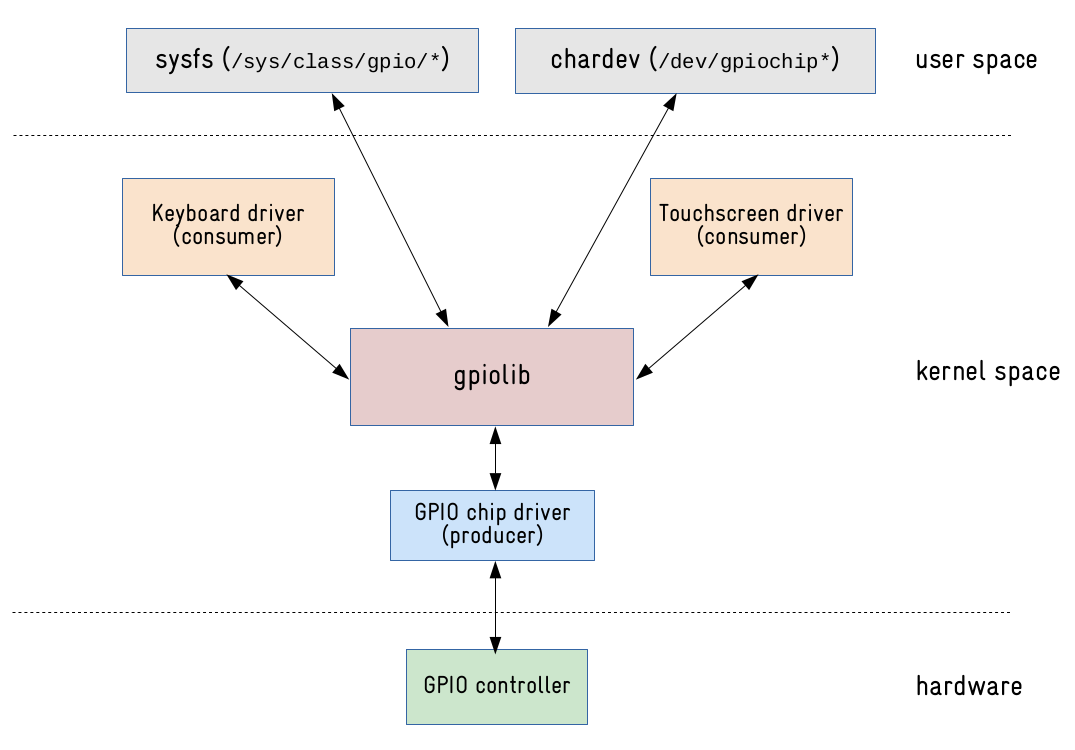

下面介紹VCS的兩種仿真flow:two-step flow和 three-step flow

- two-step flow

使用vcs,語法如下:

vcs [compileoptions] Verilog_files

常用選項如下:

-h or -help

列出最常用的VCS編譯和運行時選項的描述

-ID

返回有用的信息,如VCS版本和構建日期,VCS編譯器版本,以及工作站名稱、平臺和主機ID

-v filename

指定Verilog庫文件,VCS在這個文件中查找模塊定義和在源代碼中找到的UDP實例

-y directory

指定Verilog庫目錄,VCS在這個目錄的源文件中搜索模塊定義和UDP實例。VCS在這個目錄中搜索與實例中模塊或UDP標識符同名的文件(不是實例名)。如果找到了這個文件,VCS會在文件中搜索模塊或UDP定義來解析實例

ps:如果你在不同的庫中有多個同名的模塊,VCS會選擇用第一個-y選項指定的庫中定義的模塊

+incdir+directory+

指定VCS搜索包含文件的directory目錄,可以使用加號(+)字符指定多個目錄

+inbext+extension+

指定VCS只在庫目錄中搜索具有指定文件擴展名的文件,可以指定多個擴展名,用加號(+)分隔擴展名。例如,+libext+.v+ .V+,指定在庫中搜索擴展名為.v或.V的文件

+liborder

指定在VCS找到實例的庫的剩余部分中搜索未解析的模塊實例的模塊定義

-full64

支持64位模式下的編譯和仿真

-file filename

指定包含文件列表和編譯時選項的文件

-verdi

啟動verdi

-R

編譯后立即啟動仿真

-pvalue+parameter_hierarchical_name=value

將指定的參數更改為指定的值

-parameters filename

將文件中指定的參數更改為文件中指定的值

-notice

啟用詳細診斷消息

-q

quiet模式;抑制消息,例如關于VCS使用的C編譯器、VCS解析的源文件、頂層模塊或指定的timescale的消息

-V

verbose模式;打印消息,例如編譯器驅動程序在運行C編譯器、匯編器和鏈接器時打印它執行的命令

-lfilename

指定VCS記錄編譯消息的文件,如果還有-R選項,VCS將在同一個文件中記錄編譯和仿真的消息

+define+macro=value+

將源代碼中的文本宏定義為值或字符串,可以在Verilog源代碼中使用`ifdef編譯器指令來測試這個定義

simulation:在編譯過程中,VCS生成一個二進制可執行文件simv,使用simv來運行仿真。根據編譯的方式,可用兩種模式運行仿真:

Interactivemode

在初始階段以交互模式(調試模式)編譯design。在這個階段,可以使用GUI或通過命令行調試design問題。通過GUI進行調試可以使用Verdi,通過命令行進行調試可以使用UCLI(Unified command line interface)

batch mode

當大多數design問題解決后,可以使用批處理模式(優化模式)編譯design。在這個階段,可以以最小的debug性能來換取更好的性能來運行回歸

使用下面的命令行來仿真設計:

simv_executable [runtime_options]

缺省情況下,VCS生成可執行的二進制文件simv,但也可以在vcs命令行中使用編譯時間選項 -o 來生成具有指定名稱的二進制可執行文件

-gui

當設置了VERDI_HOME時,此選項啟動Verdi

-ucli

該選項在UCLI模式下啟動simv

- three-step flow

以上內容介紹了使用兩種仿真flow的基本步驟,其余功能需要用的時候再查VCS User Guide就行了。

END審核編輯 :李倩

-

仿真

+關注

關注

50文章

4124瀏覽量

133993 -

編譯器

+關注

關注

1文章

1642瀏覽量

49286 -

Flow

+關注

關注

0文章

10瀏覽量

8865

原文標題:淺談VCS的兩種仿真flow

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AMC1204有兩種封裝,SOIC-8和SOIC-16,功能一樣嗎?為什么要推出兩種封裝?

芯片制造過程中的兩種刻蝕方法

U50的AMD Vivado Design Tool flow設置

使用VCS兩種仿真flow的基本步驟

使用VCS兩種仿真flow的基本步驟

評論