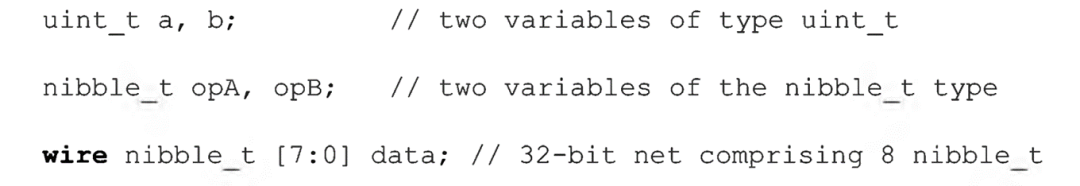

除了前面幾篇文章討論的內(nèi)置數(shù)據(jù)類型之外,SystemVerilog還為工程師定義新的數(shù)據(jù)類型提供了一種機制。用戶定義的數(shù)據(jù)類型允許從現(xiàn)有數(shù)據(jù)類型創(chuàng)建新的類型定義。

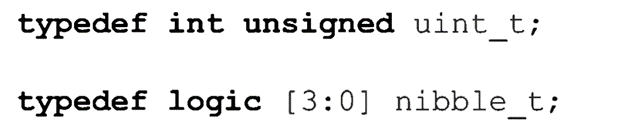

用戶自定義類型是使用typedef關(guān)鍵字創(chuàng)建的。例如:

一旦定義了新的數(shù)據(jù)類型,就可以用來定義新數(shù)據(jù)類型的變量和網(wǎng)絡(luò):

用戶自定義類型的命名約定

用戶自定義類型名可以是任何合法標(biāo)識符。在大型設(shè)計中,定義用戶自定義類型的源代碼和使用該類型的源代碼可以由多行代碼分隔,并且可以位于不同的文件中。如果用戶自定義類型的名稱與用于模塊、網(wǎng)絡(luò)或變量的名稱相似,那么typedef定義和類型用法的這種分離可能會使代碼難以讀取和維護(hù)。

為了使源代碼更易于閱讀和維護(hù),typedef名稱應(yīng)該使用一種命名約定,使名稱明顯代表用戶自定義類型。兩種常見的命名約定是在用戶自定義類型名稱中添加“_t”后綴或“t_”前綴。本文系列文章慣例使用“_t”后綴慣例。

局部typedef聲明

用戶自定義類型可以在模塊或接口中局部定義。局部typedef聲明類型只能在定義它的模塊或接口中使用。構(gòu)成總體設(shè)計的其他模塊或接口不能引用該類型的用戶自定義類型。

共享typedef定義-Shared typedef definitions

當(dāng)用戶自定義類型要在許多不同的模型中使用時,可以在包中聲明typedef定義以供其他模塊使用。

審核編輯 :李倩

-

源代碼

+關(guān)注

關(guān)注

96文章

2946瀏覽量

66960 -

數(shù)據(jù)類型

+關(guān)注

關(guān)注

0文章

236瀏覽量

13664

原文標(biāo)題:SystemVerilog(十)-用戶自定義類型

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

不同時期的硬件工程師,最怕發(fā)生的事 #電子工程師 #硬件工程師 #內(nèi)容過于真實 #YXC晶振 #揚興科技

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區(qū)別?

labview數(shù)據(jù)類型的取值范圍是多少

常見的遙感數(shù)據(jù)類型有哪些

技術(shù)干貨驛站 ▏深入理解C語言:基本數(shù)據(jù)類型和變量

ESP32-S3是否支持修改控制端點數(shù)據(jù)類型?

嵌入式軟件工程師和硬件工程師的區(qū)別?

C語言數(shù)據(jù)類型有哪些

一位硬件工程師的歷練之路:從入門學(xué)習(xí)理論到... #搞笑 #硬件工程師 #電子工程師 #揚興科技

SystemVerilog為工程師定義新的數(shù)據(jù)類型提供了一種機制

SystemVerilog為工程師定義新的數(shù)據(jù)類型提供了一種機制

評論