越來越多的技術(shù)正在使用前所未有的帶寬水平。盡管捕獲的數(shù)據(jù)有所增加,但通常最好收集盡可能多的頻譜。這給現(xiàn)代頻譜監(jiān)測(cè)解決方案帶來了重大問題;近乎實(shí)時(shí)地分析大量頻譜的計(jì)算量很大。為了滿足頻譜監(jiān)測(cè)的動(dòng)態(tài)捕獲和處理要求,軟件定義無線電 (SDR) 和外部數(shù)據(jù)處理系統(tǒng)已成為事實(shí)上的標(biāo)準(zhǔn)。高性能頻譜監(jiān)控將需要仔細(xì)考慮系統(tǒng)架構(gòu),以防止系統(tǒng)瓶頸并實(shí)現(xiàn)有效的數(shù)據(jù)分析。在高層次上,無線電需要通過高速數(shù)據(jù)鏈路連接到數(shù)據(jù)處理系統(tǒng);

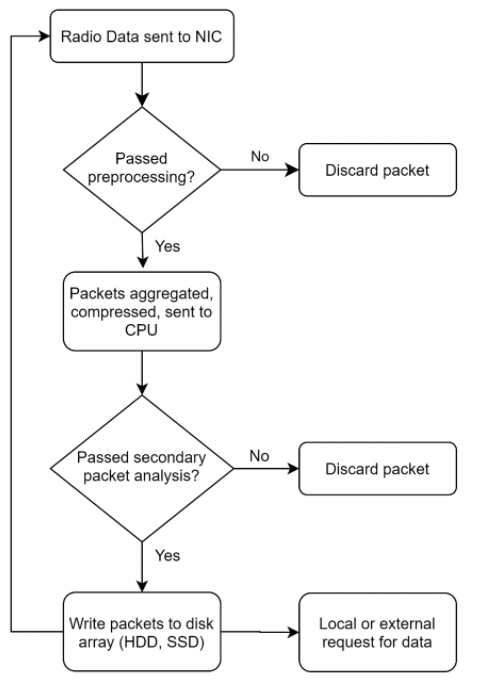

一旦數(shù)據(jù)從無線電傳輸?shù)教幚硐到y(tǒng),就會(huì)出現(xiàn)各種瓶頸。通過網(wǎng)絡(luò)接口卡 (NIC) 獲取數(shù)據(jù)可能會(huì)導(dǎo)致各種問題,首先是丟包。并非所有 NIC 都能夠處理多個(gè) Gbps,即使它們通過 PCI 總線連接也是如此。一旦 NIC 過載,數(shù)據(jù)包將開始被丟棄,從而導(dǎo)致捕獲的數(shù)據(jù)丟失,這在頻譜監(jiān)控應(yīng)用中是不可接受的。已經(jīng)開發(fā)了基于 FPGA 的 NIC 來解決這個(gè)問題,因?yàn)樗鼈兛梢灾С指叩耐掏铝俊鹘y(tǒng)的 NIC 將通過總線以一對(duì)一的方式將數(shù)據(jù)包傳輸?shù)街鳈C(jī)控制器,這可能導(dǎo)致高吞吐量實(shí)例中的擁塞。如果使用傳統(tǒng) NIC 攝取大量數(shù)據(jù),由于無法預(yù)處理和聚合數(shù)據(jù)包,數(shù)據(jù)包可能會(huì)被丟棄。基于 FPGA 的 NIC 可以利用預(yù)處理和壓縮來減少下游處理單元(例如 CPU 和其他 FPGA)的攝取工作量。

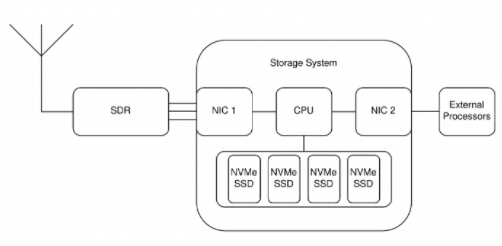

圖 1:典型的攝取硬件解決方案

數(shù)據(jù)被計(jì)算系統(tǒng)攝取后,需要進(jìn)行存儲(chǔ)和處理。系統(tǒng)的架構(gòu)應(yīng)該經(jīng)過精心設(shè)計(jì),以最大限度地提高攝取率,同時(shí)最大限度地降低硬件成本。典型的硬件配置如圖 1 所示。實(shí)施扇出存儲(chǔ)架構(gòu)是高吞吐量頻譜監(jiān)控解決方案的理想選擇,因?yàn)樗梢越档蛦蝹€(gè)系統(tǒng)組件的性能要求。讓存儲(chǔ)系統(tǒng)利用環(huán)形緩沖區(qū)來提供最大的收集歷史記錄,同時(shí)自動(dòng)丟棄最舊的數(shù)據(jù)也是謹(jǐn)慎的做法。為頻譜監(jiān)測(cè)存儲(chǔ)硬件選擇 HDD 還是 SSD 取決于應(yīng)用和成本。HDD 的價(jià)格較低,寫入速度約為 150 MBps,而 PCI 4。

具有較低數(shù)據(jù)捕獲和存儲(chǔ)要求的頻譜監(jiān)控解決方案可以利用 RAID 陣列中的 HDD。RAID 中的兩個(gè) HDD 將支持大約 2.4 Gbps 的攝取速率。這可能看起來很重要,但僅支持連續(xù)捕獲大約 100 MHz 的帶寬,前提是不存儲(chǔ)測(cè)量元數(shù)據(jù)。捕獲 GHz 的帶寬將需要存儲(chǔ)寫入速度提高幾個(gè)數(shù)量級(jí),因?yàn)樵S多頻譜監(jiān)控應(yīng)用程序目前利用多個(gè)獨(dú)立的無線電接收器來提高性能和捕獲帶寬。為了滿足這一日益增長的需求,NVMe SSD 是高性能頻譜監(jiān)控存儲(chǔ)的最佳解決方案。單個(gè)高性能 NVMe SSD 可以取代 17 個(gè) HDD RAID,這意味著單個(gè)設(shè)備可以攝取超過 1600 MHz 的捕獲頻譜。雖然 SSD 與機(jī)械對(duì)應(yīng)物相比提供了顯著的性能改進(jìn),但許多頻譜監(jiān)控解決方案仍需要 RAID 配置。要從最先進(jìn)的 4x40 Gbps NIC 攝取數(shù)據(jù),需要一個(gè)由四個(gè)高性能 SDD 組成的條帶陣列。

除了傳輸速度要求外,系統(tǒng)的計(jì)算能力還必須能夠滿足攝取和處理的要求。隨著捕獲的頻譜數(shù)量的增加,CPU 和處理卡的功能也會(huì)增加。高捕獲帶寬將需要分配多個(gè) CPU 內(nèi)核。存儲(chǔ) 160 Gbps 的數(shù)據(jù)需要大約 25 個(gè) CPU 內(nèi)核專門用于攝取過程 [ ntop]。建議使用分布式計(jì)算架構(gòu)、板載 FPGA 和 GPU 或某種組合來處理此數(shù)據(jù)的分析。除了 CPU 內(nèi)核之外,還應(yīng)分配數(shù) GB 的 RAM 來緩沖數(shù)據(jù),然后再將其寫入 RAID 陣列。對(duì)于 HDD 陣列,緩沖區(qū)大小應(yīng)該更大以補(bǔ)償寫入延遲,但對(duì)于基于 SSD 的存儲(chǔ)解決方案,可以減小大小。

圖 2:數(shù)據(jù)包捕獲和處理數(shù)據(jù)流

基于 SDR 的頻譜監(jiān)測(cè)解決方案的一個(gè)顯著優(yōu)勢(shì)是它們提供的高度可重構(gòu)性。由于硬件配置的可變性,捕獲的元數(shù)據(jù)在分析過程中至關(guān)重要。捕獲帶寬、載波頻率和溫度等參數(shù)可能會(huì)有很大差異,相關(guān)元數(shù)據(jù)必須與頻譜數(shù)據(jù)一起存儲(chǔ)。眾多 SDR 供應(yīng)商的存在及其獨(dú)特的數(shù)據(jù)包協(xié)議會(huì)使捕獲數(shù)據(jù)的分析變得復(fù)雜。使用符合 VITA49 標(biāo)準(zhǔn)的 SDR 將提高 SDR 平臺(tái)數(shù)據(jù)之間的性能和一致性。符合 VITA49 的 SDR 數(shù)據(jù)將捕獲的樣本與元數(shù)據(jù)隔離。元數(shù)據(jù)的分離減少了數(shù)據(jù)傳輸,因?yàn)榉?VITA49 的 SDR 僅在 SDR 看到更改時(shí)才發(fā)送元數(shù)據(jù)數(shù)據(jù)包,從而為頻譜捕獲數(shù)據(jù)留出更多空間。除了出色的元數(shù)據(jù)處理之外,VITA49 還支持對(duì)數(shù)據(jù)包進(jìn)行高精度時(shí)間戳,并通過定時(shí)校正來補(bǔ)償 RF 前端延遲,從而產(chǎn)生更準(zhǔn)確的元數(shù)據(jù) [IEEE ]。

盡管在許多應(yīng)用中變得越來越普遍,但目前可用的大多數(shù) SDR 都無法滿足高性能寬帶頻譜監(jiān)測(cè)應(yīng)用的要求。除了高信道帶寬之外,許多頻譜監(jiān)測(cè)應(yīng)用還需要多個(gè)獨(dú)立的接收鏈來實(shí)現(xiàn)空間信息提取。為了實(shí)現(xiàn)高帶寬捕獲和處理,無線電和早期處理系統(tǒng)需要通過高速數(shù)字回程緊密集成。嚴(yán)格的集成要求導(dǎo)致交鑰匙 SDR 解決方案提供最佳性能,同時(shí)縮短硬件開發(fā)時(shí)間。由于數(shù)據(jù)攝取和處理要求可能非常嚴(yán)格,一些交鑰匙解決方案會(huì)將記錄、存儲(chǔ)和回放直接集成到解決方案中,以確保最佳性能。

審核編輯:郭婷

-

cpu

+關(guān)注

關(guān)注

68文章

10904瀏覽量

213027 -

SSD

+關(guān)注

關(guān)注

21文章

2889瀏覽量

117861 -

無線電

+關(guān)注

關(guān)注

60文章

2149瀏覽量

116815

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

快速輸入轉(zhuǎn)換速率應(yīng)用中DC-DC轉(zhuǎn)換器的設(shè)計(jì)注意事項(xiàng)

脈沖式充電器的使用注意事項(xiàng)

繞線電感定制的注意事項(xiàng)

請(qǐng)問opa637設(shè)計(jì)注意事項(xiàng)是什么?

使用環(huán)形接線片熱敏電阻進(jìn)行散熱器監(jiān)測(cè)的設(shè)計(jì)注意事項(xiàng)

共模電感定制的注意事項(xiàng)

具有邊沿速率加速器的TXB和TXS電壓電平轉(zhuǎn)換器的注意事項(xiàng)

LiFePO4設(shè)計(jì)注意事項(xiàng)

采用高側(cè)N-MOSFET的堆疊式BQ769x2設(shè)計(jì)注意事項(xiàng)

頻譜監(jiān)測(cè)和記錄中SDR的高數(shù)據(jù)速率注意事項(xiàng)

頻譜監(jiān)測(cè)和記錄中SDR的高數(shù)據(jù)速率注意事項(xiàng)

評(píng)論