在本文中,我們將討論多核處理的各個方面,包括了解不同類型的多核處理器以及為什么這些設備在今天變得普遍和流行。然后,我們將研究在芯片上擁有多個內核所帶來的一些挑戰,以及現代多核感知調試器如何幫助使這些復雜任務更易于管理。

系統性能

有許多方法可以提高嵌入式計算系統的性能,從巧妙的編譯器算法到高效的硬件解決方案。編譯器優化對于從易于閱讀和理解的高級語言代碼中獲得最有效的指令調度非常重要。除此之外,系統可以利用項目中可用的并行性來一次處理多個事情。當然,縮放時鐘頻率可能是從計算系統中獲得更高性能的有效方法。

不幸的是,可以假設時鐘速度呈幾何級數增長的時代已經過去。而代碼優化只能給你帶來這么多的改進,尤其是現在,經過多代編譯器技術的發展。這讓我們將并行性視為隨著時間的推移繼續擴展我們的系統性能的最佳機會。

并行性

挖井是一項難以并行化的任務。其他人可以幫忙,把泥土鏟走,但實際挖洞通常是一個人的工作。結果,增加更多的人不會更快地完成工作。事實上,其他人可能只是妨礙并減慢進程。有些任務不適合并行化。

其他任務很容易并行化。挖溝是一項適合并行化的任務。許多人可以并肩工作。

這張圖片顯示了一種稱為 MIMD(多指令多數據)的并行形式。每個挖掘機都是一個獨立的單元,可以執行不同的任務。在這種情況下,您可以想象四臺挖掘機完成工作的時間大約是一臺挖掘機的1/4 。

使用 SIMD(單指令多數據),單個挖掘機可能會使用像這樣的鏟子。

SIMD 單元一次只能執行一種類型的計算,但它可以并行執行多條數據。這些類型的指令在許多處理器的向量處理單元中很常見。如果您的數據非常規則,并且您需要對大型數據集(例如在圖像處理中)反復執行相同的操作,這將非常有用。然而,對于更一般的計算任務,該模型缺乏靈活性并且不會產生性能提升。

這導致我們選擇將多個完整的 CPU 子系統放在一個芯片上,從而創建多核處理器。一個芯片上的多個內核可以擴展性能。每個內核都是一個完整的 CPU,可以獨立工作或與其他內核協同工作。

不同類型的多核處理

處理器芯片上可能有不同類型的內核組合,以及工作在它們之間的分配方式。

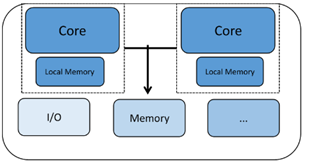

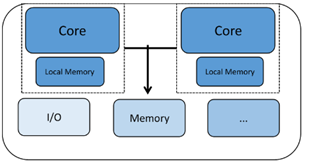

同構多核處理器具有相同處理器內核的兩個或多個副本。每個核心都自主運行,并且可以通過共享內存或郵箱系統等多種機制與其他核心進行通信和同步。每個處理器都有自己的寄存器和功能單元,并且可能有自己的本地內存或緩存。然而,使這種同質化的原因在于我們正在查看的所有內核都是同一類型的。

另一種類型的多核芯片稱為異構多核,具有兩種或多種不同類型的 CPU 內核。這里的內核可能具有非常不同的特性,這使得它們非常適合系統處理需求的不同部分。一個例子可能是藍牙通信芯片,其中一個內核專用于管理藍牙協議棧,而另一個內核可能管理外部通信、應用程序處理、人機界面等。這種多核芯片可用于需要兩者的應用程序一個核心的實時專用性能和另一個核心的系統管理功能。

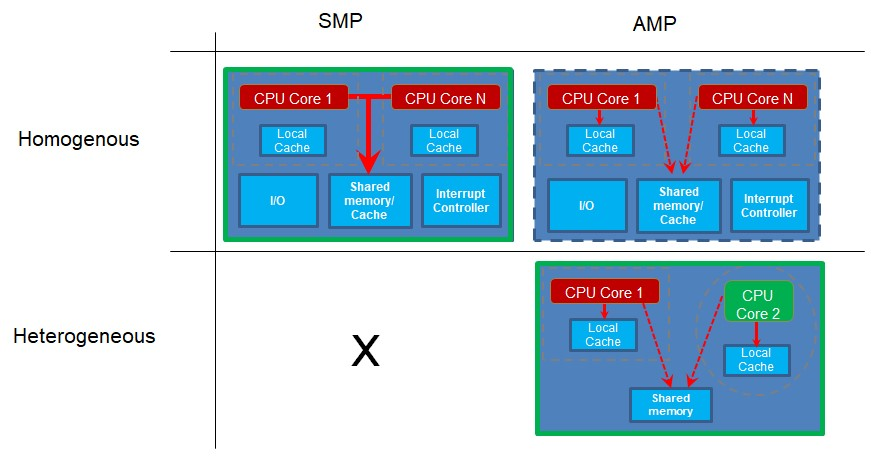

現在我們來看看核心是如何使用的。當您擁有多個內核并且這些內核運行相同的項目代碼庫時,就會發生對稱多處理 (SMP)。不同的內核可能同時運行代碼的不同部分,但代碼是作為單個項目構建的,并由一些控制程序(如實時操作系統 (RTOS))分派到不同的內核。必要時,以這種方式工作的內核必須屬于同一類型,因為它們都使用為一種類型的處理器編譯的相同項目代碼。

當您擁有多個內核或處理器并且每個處理器都運行自己的項目應用程序時,就會發生非對稱多處理 (AMP)。獨立的核心可能會不時同步或通信,但它們每個都有自己執行的代碼庫。由于他們每個人都在運行自己的項目,因此這些內核可以是不同類型的,也可以是異構內核。但是,這不是必需的。如果兩個或多個相同類型的內核運行不同的項目代碼,則它們是同質內核,運行 AMP。

請注意,對于 SMP 操作,您必須擁有多個同質內核,因為它們都運行來自同一個項目代碼庫的代碼。但是,如果您有多個項目具有不同的代碼庫以運行不同的內核,則這些項目可能是不同的內核,例如在異構系統中。但是,如果內核相同,那也可以。

使用多核的原因

在過去的幾年里,在 1960 年代中期創造的摩爾定律似乎終于失去了動力,或者至少正在放緩。處理器時鐘頻率不再每 2-3 年翻一番,事實上,最高速度的 CPU 多年來一直在低個位數 GHz 范圍內達到上限。

繼續推動性能極限的一種方法是讓更多 CPU 內核協同工作,前提是您可以有效地使用它們。

雖然速度已經趨于穩定,但晶體管尺寸卻在繼續縮小。雖然速度比過去慢,但小型晶體管可以在單個芯片上封裝更多邏輯。因此,使用這些晶體管將多個 CPU 內核放在一個芯片上可以利用多個 CPU 和內存子系統之間更快、更寬的總線互連。

異構非對稱多處理在應用程序具有兩個或多個具有非常不同的特征和要求的工作負載時非常有用。一種可能依賴于實時和中斷延遲,而另一種可能更依賴于吞吐量而不是響應時間。該模型運行良好:例如,設備可能專用一個內核來管理藍牙或 Zigbee 等通信協議棧,而另一個內核則充當運行人類交互和整體系統管理操作的應用處理器。隔離的通信處理器可以提供協議棧所需的出色實時響應。此外,通信軟件可以通過標準認證,通過將功能修改與系統的這一部分分開,使整個產品易于認證。

使用多核的挑戰

當您在一個芯片上放置多個 CPU 內核時會帶來哪些挑戰?好吧,讓我們深入研究一下。

單一應用程序或軟件可能無法有效地使用可用的計算資源。您需要將應用程序組織成可以同時運行的并行任務,以使用多個內核的資源。這可能需要軟件工程師以一種不熟悉的方式來考慮嵌入式設計。遷移現有的單循環代碼可能不是很容易。線程太少甚至線程太多都可能成為性能障礙。

在多個線程或進程之間共享數據結構或 I/O 設備的應用程序可能存在串行瓶頸。為了維護數據完整性,對這些共享資源的訪問可能必須使用鎖定技術進行序列化,例如,讀鎖、讀寫鎖、寫鎖、自旋鎖、互斥鎖等。由于多個線程或試圖獲取鎖以使用共享資源的進程之間的高鎖爭用,設計低效的鎖可能會造成瓶頸。這可能會降低應用程序或軟件的性能。如果某些內核停止等待其他內核等待公共鎖導致兩個內核的性能比一個差,則應用程序的性能甚至會隨著內核或處理器數量的增加而降低。

不均勻分布的工作負載在利用計算資源方面可能效率低下。您可能必須將大型任務分解為可以并行運行的較小任務。您可能必須將串行算法更改為并行算法以提高性能和可擴展性。但是,如果一些任務運行得非常快,而另一些任務需要大量時間,則快速任務可能會花費大量時間等待長任務完成。這會導致寶貴的計算資源閑置和性能擴展不佳。

RTOS 可能會幫助您,但可能無法解決所有問題。在 SMP 系統中,這實際上是在多個類似內核上調度任務的必要條件。要做的工作可以按數據或按功能劃分。如果您按數據塊劃分事物,則每個線程可能會執行處理管道中的所有步驟。或者,您可能讓一個線程在函數中執行一個步驟,而另一個線程執行下一步,等等。一種技術相對于另一種技術的優勢將取決于要完成的工作的特征。

在多核環境中調試

調試多核系統時有用的第一件事是所有內核的可見性。理想情況下,我們應該能夠同時或單獨啟動和停止核心——也就是說,在其他核心運行或停止時單步執行一個核心。多核斷點對于根據另一個核的狀態來控制一個核的操作非常有用。

多核跟蹤可能很難實現。管理來自多個內核的高帶寬跟蹤信息,以及處理來自不同類型內核的潛在不同類型的跟蹤數據是一個真正的挑戰。

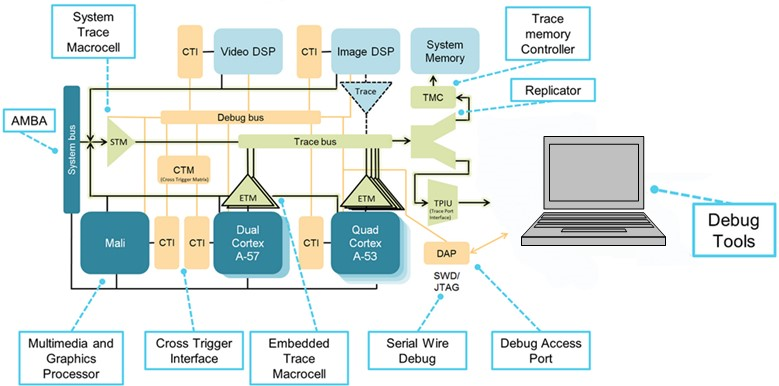

(來源:IAR Systems,圖表由 Arm Ltd. 提供)

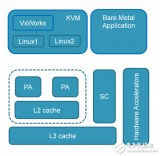

Here is an example of a processor with both heterogeneous and homogeneous multicore implementations. There are two homogeneous core groups, one based on a dual Arm Cortex-A57 and the other on a quad Cortex-A53. These groups are homogeneous within themselves but heterogeneous among the two groups.

CoreSight 調試架構提供了與所有內核上的調試資源進行通信的協議和機制,調試器負責管理所有這些信息并解析來自不同內核的消息。交叉觸發接口和矩陣(CTI、CTM)允許同時停止兩個內核、觸發跟蹤等。跟蹤基礎設施包括用于平滑跟蹤流的串行 (SWD) 和并行 (TPIU) 跟蹤端口,以及將來自每個源的跟蹤合并為單個流的跟蹤漏斗。與雙核部分相比,圖中所示的芯片控制起來要復雜得多。

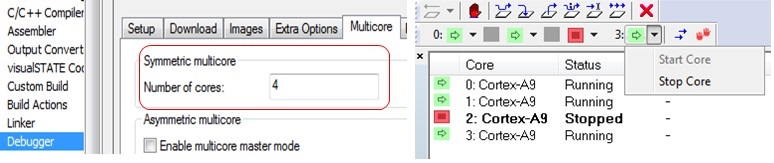

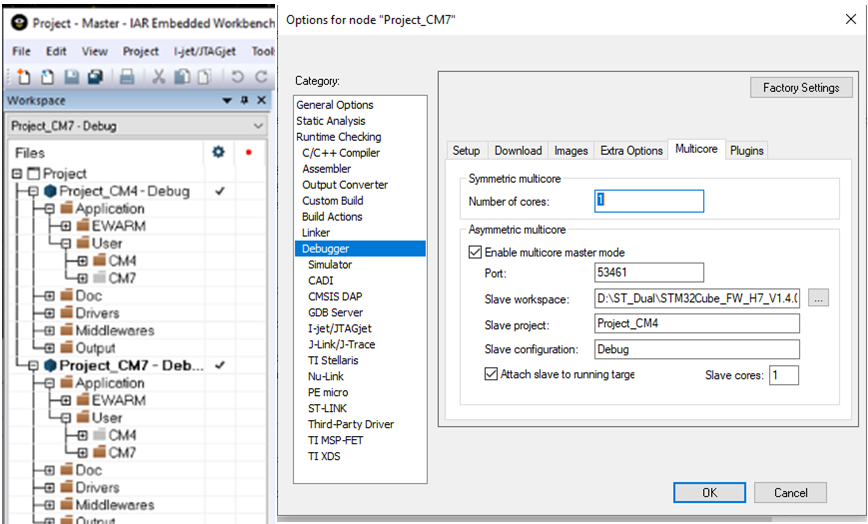

IAR Embedded Workbench 中的 C-SPY 調試器支持對稱和非對稱多核調試。這是通過多核選項卡上的調試器選項啟用的。要啟用對稱多核調試,只需要輸入內核數量,讓調試器知道要與多少個不同的處理器通信。其他 IDE 可能有類似的可用選項。

在右側(上圖),您可以在調試器中看到一個視圖,其中 4 核 Cortex-A9 SMP 集群顯示其內核狀態,其中 2 號內核停止,而其他三個內核正在執行。

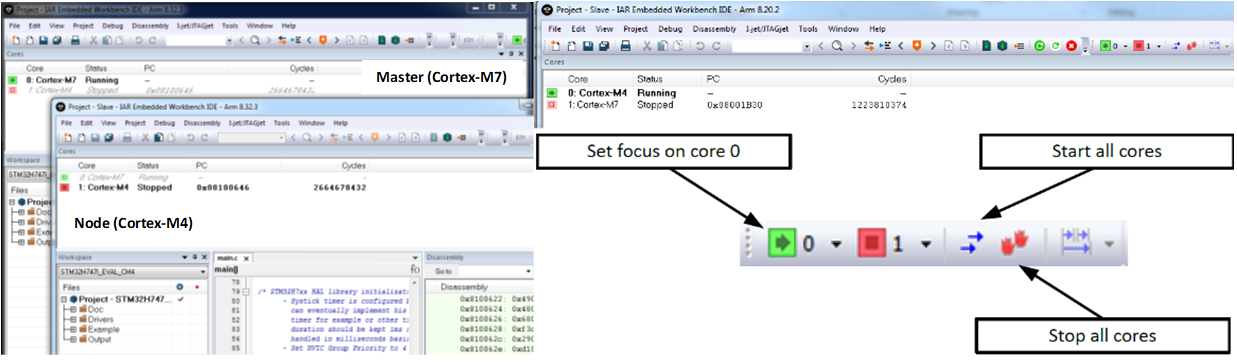

非對稱多核系統可能使用異構多核部分,例如 ST STM32H745/755,它具有一個 Cortex-M7 內核和一個單獨的 Cortex-M4。在這種情況下,當調試器運行時,它會使用 IDE 的兩個實例(Master 和 Node)。每個核心一個,因為兩個核心運行不同的項目代碼。

在 IDE 的每個實例中,都有關于正在控制的核心以及在另一個窗口中控制的另一個核心的狀態信息。可以選擇一些選項來控制調試器的行為,以便一起或單獨啟動和停止內核在開發人員的控制之下。

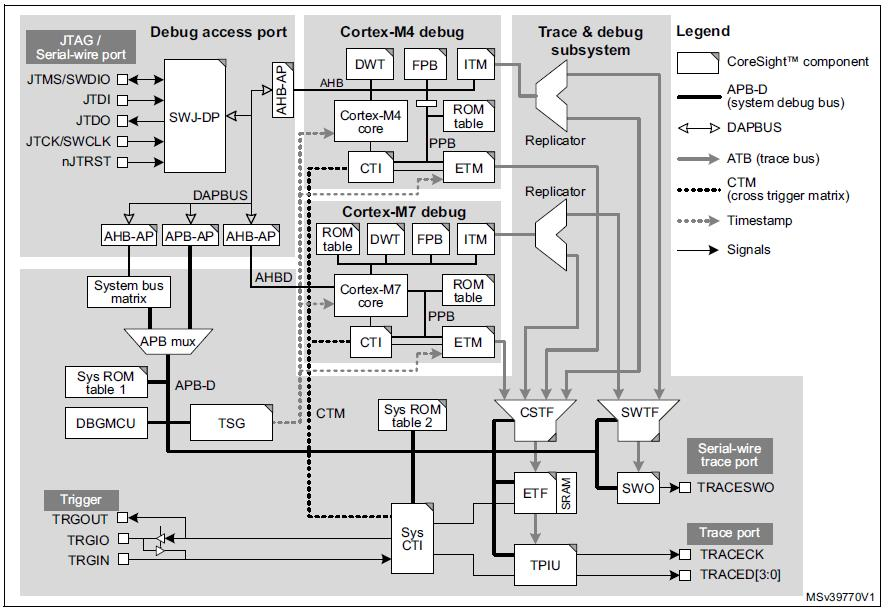

由于交叉觸發接口 (CTI) 和交叉觸發矩陣 (CTM) 共同構成了 Arm 嵌入式交叉觸發功能,因此這種完全控制成為可能。共有三個 CTI 組件,一個在系統級,一個專用于 Cortex-M7,一個專用于 Cortex-M4。三個 CTI 通過 CTM 相互連接,如下圖所示。調試器可以通過系統訪問端口和相關的 APB-D 訪問系統級和 Cortex-M4 CTI。Cortex-M7 CTI 物理集成在 Cortex-M7 內核中,可通過 Cortex-M7 訪問端口訪問。

(來源:IAR Systems,圖表由 STMicroelectronics 提供,來自 M0399 參考手冊)

CTI 允許來自各種來源的事件觸發調試和跟蹤活動。例如,在一個處理器內核中達到的斷點可以停止另一個處理器,或者可以將在外部觸發輸入上檢測到的轉換設置為開始代碼跟蹤。

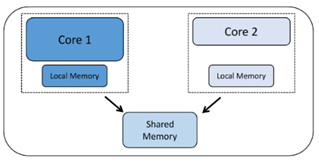

在此示例中,異構多核處理器在單個芯片上具有 Cortex-M7 內核和 Cortex-M4 內核,使用了兩個獨立的程序:一個在 Cortex-M4 上運行,另一個在 Cortex-M7 上運行。每個項目都使用 FreeRTOS 來管理處理器上運行的軟件。兩個內核通過共享內存接口進行通信。但是,應用程序都使用 FreeRTOS 消息傳遞機制與其他處理器進行通信,并隱藏了底層機制的復雜性。因此,從一個 CPU 的角度來看,它只是通過另一個任務發送或接收消息。另一個任務恰好在另一個 CPU 內核上運行是透明的。

下圖是 IDE 中的 Workspace explorer 寡婦。此處顯示了兩個項目的概述,因此您可以查看 Cortex-M7 和 Cortex-M4 項目的內容。

通過選擇窗口底部的其他選項卡之一,您可以將焦點切換到 M4 項目或 M7 項目。

Cortex-M7 項目有一個任務,它向 Cortex-M4 上運行的任務發送消息。Cortex-M4 有兩個正在運行的接收任務實例。Cortex-M7 有一個“檢查”任務,它會定期運行以查看事情是否仍在正常運行。

最后,調試器加載這兩個項目。這意味著為第二個調試器啟動了一個額外的 Embedded Workbench 實例。

要為非對稱多處理支持設置調試器,我們需要將一個項目指定為“主”項目,將另一個項目指定為“節點”項目。事實上,選擇是任意的,只決定了哪個項目有能力在啟動時啟動另一個。

“節點”項目沒有特殊設置,并且不知道它正在作為另一個項目的“節點”運行。

這樣,當“主”項目啟動其調試器時,它會自動啟動 IDE 的另一個實例以適應第二個調試器會話,第二個項目將在其中運行。

概括

當摩爾定律用完時,多核可以提高性能。然而,多核帶來了調試挑戰,并且需要特定的開發方法,以便應用程序可以最大限度地利用多核架構。

配置調試設置后,多核調試從未如此簡單。如果您以前使用過調試單核的工具,您將認識到其中包含的所有內容,并且您可能永遠不會理解其他人談論多核調試對他們來說有多困難。

現代硬件和軟件工具將幫助您克服多核調試挑戰。

注意:除非另有說明,否則圖片均由 IAR Systems 提供。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19407瀏覽量

231182 -

芯片

+關注

關注

456文章

51170瀏覽量

427244 -

嵌入式

+關注

關注

5092文章

19177瀏覽量

307663

發布評論請先 登錄

相關推薦

【中級】labview每日一教【11.14】labview多核編程篇

NI LabVIEW的多核編程技術指南

基于RealView的多核調試

多核架構及編程技術

多核專家系列:多核軟件遷移與開發:挑戰與解決方案

多核軟件調試方法與困難

多核軟件調試的難點和新方法分析

KeyStone多核SoC工具套件

基于NI LabVIEW圖形化編程對多核處理器和其他并行硬件進行編程

多核處理器的基本架構是什么?有哪些調試方法?

多核JTAG調試方法的特點及應用挑戰

掌握多核編程和調試的挑戰

掌握多核編程和調試的挑戰

評論