在上一篇文章《等價性比對驗證之combinational?equivalence》中,我們說過Combinational equivalence比對最嚴格,但是在很多場景下有限制(不適應于時序單元變化的場景)。

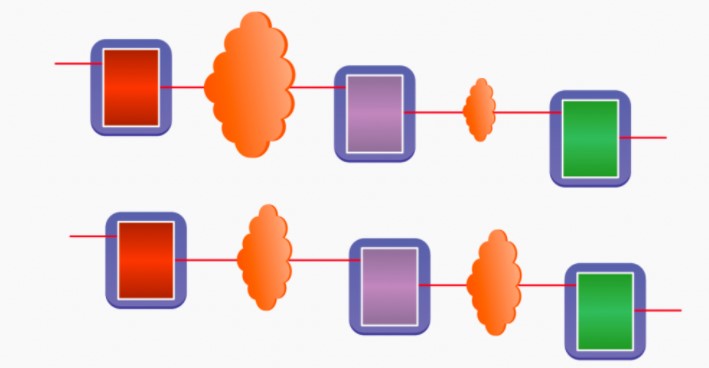

本章我們在時序單元數(shù)量或者位置發(fā)生變化,但是整體功能不變的場景下對于Combinational equivalence進行一定程度的放松。

SEQUENTIAL EQUIVALENCE

Sequential equivalence被某些EDA工具稱之為周期精確等價(cycle-accurate equivalence),名字不重要,關鍵的是理解它和combinational?equivalence的區(qū)別。

Sequential equivalence是使用EDA工具形式化地確認是否SPEC模型和IMP模型能否在相同的激勵下產(chǎn)生相同的輸出(這是最基本的要求)。另外不同于combinational?equivalence,它不要求電路中每個時序單元都能夠精確地比對,最終只要輸出的時序一致即可。

如此,就可能在綜合工具進行一些特殊優(yōu)化使得時序單元數(shù)量、位置和流水線深度發(fā)生變化時依然能夠比對通過。

其實伴隨著對于combinational?equivalence的要求的放松,

sequential?equivalence以及后面即將介紹的transaction-based equivalence.

越來越貼近FPV。

審核編輯:劉清

-

EDA工具

+關注

關注

4文章

268瀏覽量

31936 -

SPEC

+關注

關注

0文章

31瀏覽量

15844 -

IMP

+關注

關注

0文章

11瀏覽量

8435

原文標題:等價性比對驗證之sequential?equivalence

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

一文解析最嚴格的等價性比對驗證combinational equivalence

FPGA時序約束之衍生時鐘約束和時鐘分組約束

allegro布局完成后修改線寬約束后如何更新到PCB中

線寬約束規(guī)則失效?

分享一個FEC RTLvs Netlist等價性比對的示例

時序邏輯設計原則 (Sequential Logic Des

時序邏輯設計實踐 (Sequential Logic Des

帶黑盒組合電路的等價性驗證

嵌入式操作系統(tǒng)實時性比對與分析

動態(tài)矩陣/Field Sequential 是什么意思

什么是軟件與硬件的邏輯等價性

支持Baseline和Extended Sequential

FPGA約束的詳細介紹

介紹3個時序優(yōu)化的RTL改動及其中Formal SEC的角色

介紹放寬約束的等價性比對sequential equivalence

介紹放寬約束的等價性比對sequential equivalence

評論