靜態時序分析包括建立時間分析和保持時間分析。建立時間設置不正確可以通過降低芯片工作頻率解決,保持時間設置不正確芯片無法正常工作。

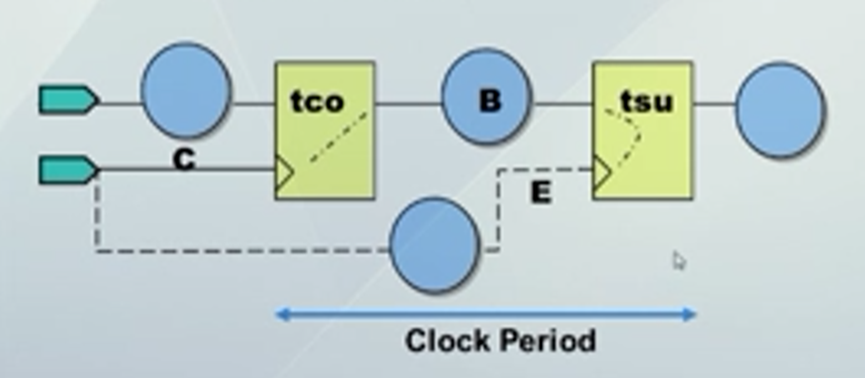

保持時間分析與建立時間分析的電路結構相同。需要分析的變量與建立時間分析的變量相似,包括:C(時鐘信號傳遞到源觸發器的延時)、E(時鐘信號傳遞到目標觸發器的延時)、B(從源觸發器到目標觸發器所經過的組合邏輯電路的延時)、tco(源觸發器延時)。

圖一,圖片來源:學堂在線《IC設計與方法》

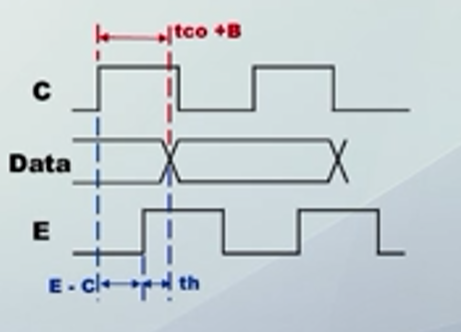

結合圖一和圖二說明建立時間和保持時間。

建立時間的設置需保證時鐘信號到達目標觸發器前,數據信號已在目標觸發器穩定建立,在圖二波形圖中顯示為Data數據的替換的時間點先于E的第二個時鐘上升沿。

保持時間的設置需保證數據信號在目標觸發器穩定建立前,數據信號可以一直保持,源觸發器的下一個數據信號未替換當前信號,在圖二的波形圖中顯示為Data數據替換的時間點滯后于E的第一個時鐘上升沿。即滿足如下公式:

tco+B>E-C+th

其中th為保持時間。

圖二,圖片來源:學堂在線《IC設計與方法》

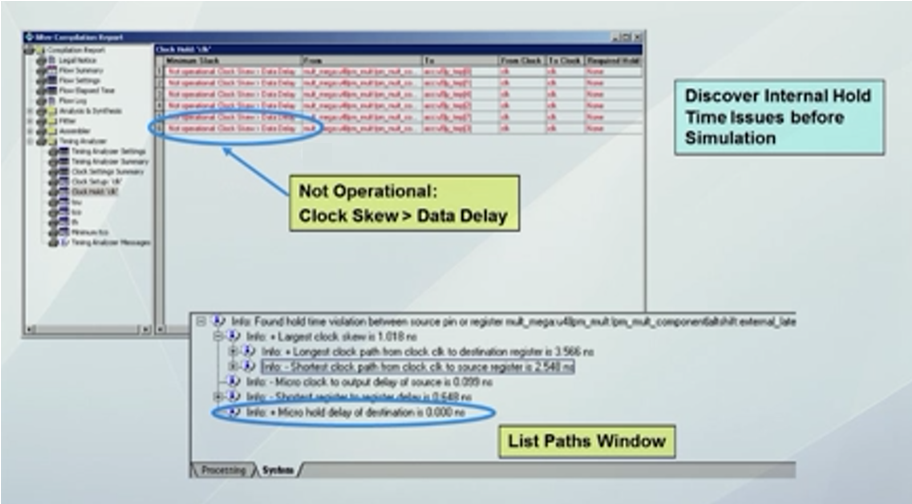

圖三是Quartus Ⅱ工具關于保持時間的分析結果,圖中紅色字部分顯示保持時間設置錯誤,原因是Clock Skew>Data Delay,其中ClockSkew=E-C,Data Delay=tco+B。設計人員可以通過Quarus Ⅱ工具觀測保持時間分析結果的具體值,如ClockSkew的值為1.018ns等。

圖三,圖片來源:學堂在線《IC設計與方法》

設計人員除了進行電路內部的時序分析,還需進行電路輸入路徑和輸出路徑的時序分析。

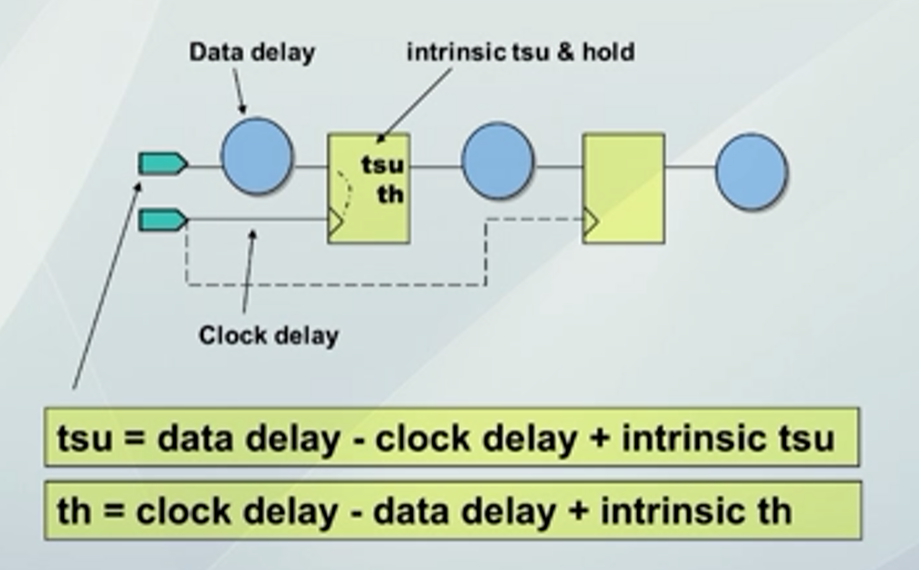

輸入路徑的建立時間和保持時間計算:基于內部建立時間(intrinsic tsu)和保持時間(intrinsic th),結合輸入數據延時(data delay)和時鐘延時(clock delay),得出如圖四所示的兩個公式(tsu為建立時間、th為保持時間)。

圖四,圖片來源:學堂在線《IC設計與方法》

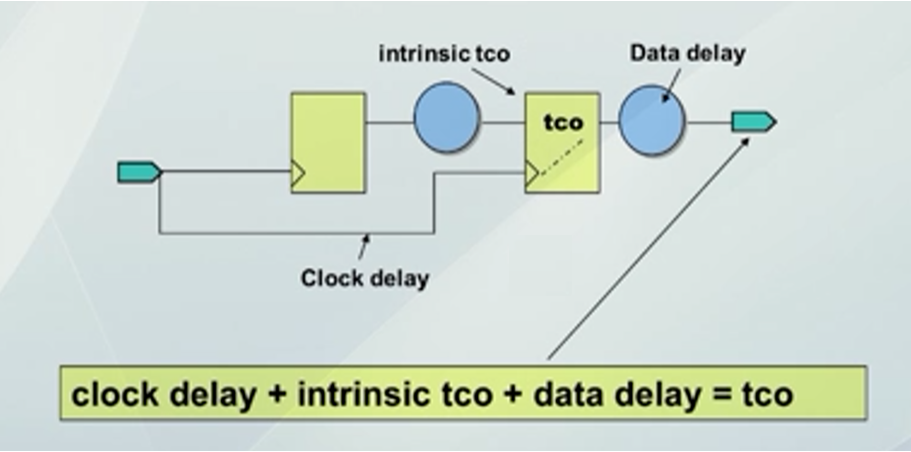

輸出路徑的延時計算公式如圖五所示,將內部延時、數據延時、時鐘延時相加得出輸出路徑延時。

圖五,圖片來源:學堂在線《IC設計與方法》

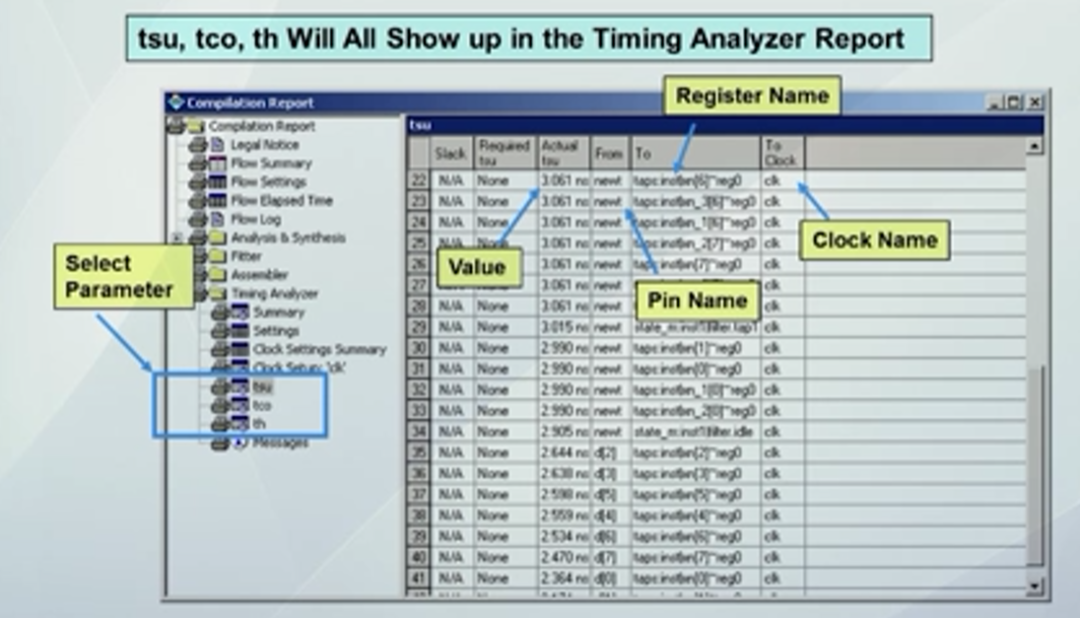

圖六展示了Quartus Ⅱ工具關于輸入路徑、輸出路徑時序分析結果。Quartus Ⅱ工具會分析所有路徑,并將延時最長路徑放置在最靠上的位置。每條路徑的信息包括延時時長、輸入引腳、輸出到的寄存器、時鐘信號。

由圖六可以發現,輸入路徑(虛擬D觸發器)最長的建立時間為3ns,大于內部D觸發器建立時間(內部D觸發器的建立時間為0.1ns-0.3ns)。

因此,如果設計人員需要設計高性能電路,需要盡可能將數據傳遞路徑(包括內核運算邏輯和數據保存)設計在芯片內部。如果芯片設計的數據路徑經過芯片外部器件如SRAM(一種寄存器),芯片性能會大幅下降。

圖六,圖片來源:學堂在線《IC設計與方法》

總結芯片時序分析過程,包括芯片內部保持時間分析和建立時間分析、輸入路徑保持時間分析和建立時間分析、輸出延時分析。時序分析在芯片設計中具有重要作用,如果時序分析結果不能滿足要求,一般需要修改芯片設計代碼。

審核編輯:劉清

-

觸發器

+關注

關注

14文章

2003瀏覽量

61347 -

組合邏輯電路

+關注

關注

6文章

70瀏覽量

14701 -

時鐘信號

+關注

關注

4文章

453瀏覽量

28665

原文標題:芯片設計相關介紹(33)——保持時間和建立時間

文章出處:【微信號:行業學習與研究,微信公眾號:行業學習與研究】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯片設計進階之路—從CMOS到建立時間和保持時間

FPGA時序分析-建立時間和保持時間裕量都是inf怎么解決呢?

建立時間和保持時間討論

FPGA實戰演練邏輯篇57:VGA驅動接口時序設計之4建立和保持時間分析

保持時間與建立時間

建立時間和保持時間(setup time 和 hold time)

PCB傳輸線建立時間、保持時間、建立時間裕量和保持時間裕量

關于建立時間和保持時間的測量方法

靜態時序之建立時間和保持時間分析

靜態時序之建立時間和保持時間分析

評論