時鐘對芯片功能準確性、性能高低和功耗高低有著至關重要的影響。芯片的時鐘來源一般有三種:

第一,通過外部引腳直接輸入時鐘信號,常用于接口芯片、傳感器芯片,SOC系統中少見;

第三,內部時鐘發生器+內部PLL +內部分頻器產生時鐘,常見于對安全、功耗有特殊要求的芯片;

第四,外部晶振+內部時鐘震蕩器+內部PLL +內部分頻器產生時鐘,性能高一點的MCU基本都采用這種方案。

以第四時鐘方案為例,其采用外部晶振是因為外部晶振精度高,采用內部時鐘振蕩器是利用其安全、靈活、低功耗的優勢,配置PLL可將外部晶振和內部振蕩器的時鐘倍頻,再通過分頻器分頻供給到各個模塊。且為了節省功耗該SOC系統往往工作頻率可變,性能要求高時使用高頻率、任務簡單時使用低頻率,不工作的時候可關掉時鐘。這就是廣泛應用的多時鐘模式系統,實現該系統需要采用時鐘切換、clock gating甚至power gating技術。

本文首先探討時鐘切換的實現,對于clock gating和power gating問題后續探討。

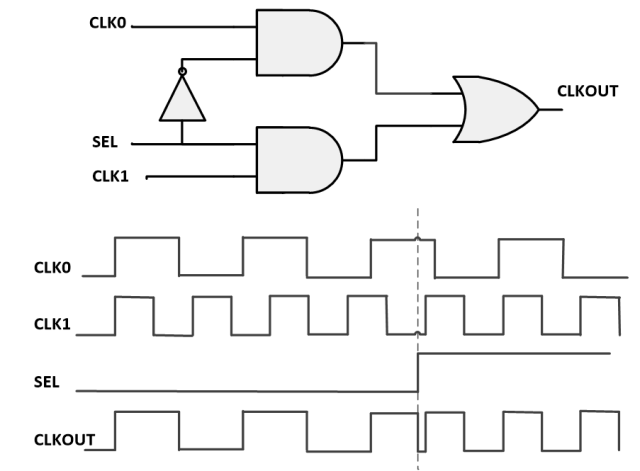

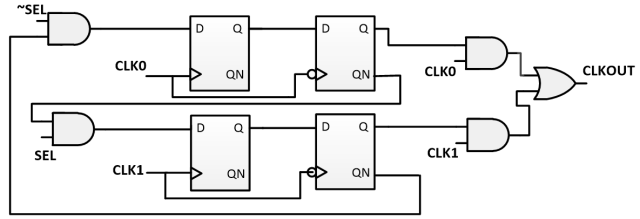

圖1

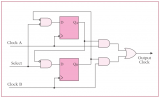

首先討論兩個時鐘間的切換問題,這兩個時鐘可能是具有倍頻關系的同步時鐘,也能是不相關的異步時鐘。很容易想到采用二選一選擇器就可以實現這一功能,不幸的是無論這兩個時鐘關系如何,都可能在時鐘線上引入毛刺,如圖1所示。

二選一選擇器采用與或門的形式實現,SEL是選擇信號,選擇CLK0或CLK1到輸出端口CLKOUT,也就是說CLKOUT是CLK0和CLK1拼接的結果。

圖1中,SEL信號由低到高變化,CLK0為高電平、CLK1為低電平,此時CLKOUT就會出現向下的毛刺;如果此時CLK0的頻率高于CLK1,那么CLKOUT的毛刺就是向上的脈沖。既然毛刺的出現是選擇信號SEL變化時,兩個輸入時鐘CLK0和CLK1高低交錯,高低電平拼接造成的。

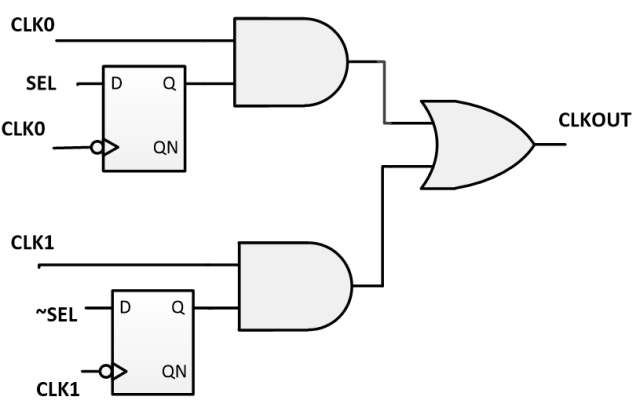

那么,如果讓選擇信號在兩個時鐘的下降沿處分別將時鐘截斷,再拼接成輸出時鐘,是不是就可以避免毛刺出現了呢?為此,我們在選擇路徑中插入下降沿觸發器對SELECT信號進行下降沿采樣,如圖2(a)所示。

圖 2(a)

圖 2(b)

但這樣仍存在問題,存在著CLK0沒有被SELECT關斷,CLK1已經開始輸出的情況,這仍有可能產生輸出毛刺,如圖2(b)所示。

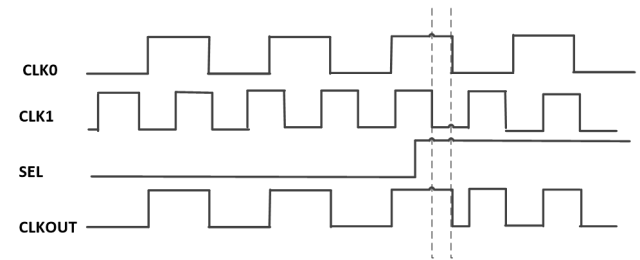

為了保證一個時鐘選擇信號關斷后另一個時鐘再輸出,再在觸發器前插入與門,連接成交叉反饋結構,如圖3(a)所示,這就是經典的時鐘轉換電路。但這還是不夠,如果CLK1和CLK0是異步的,那還需要對其進行同步,采用傳統同步方式,插入上升沿觸發器即可,如圖3(b)所示。

圖 3(a)

圖 3(b)

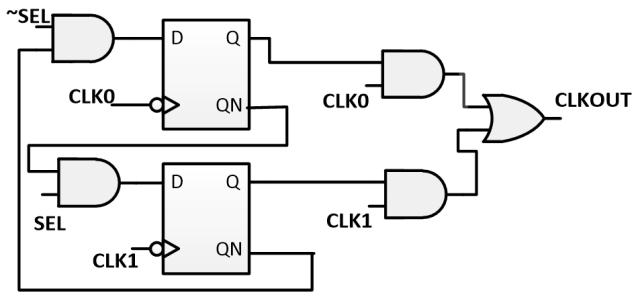

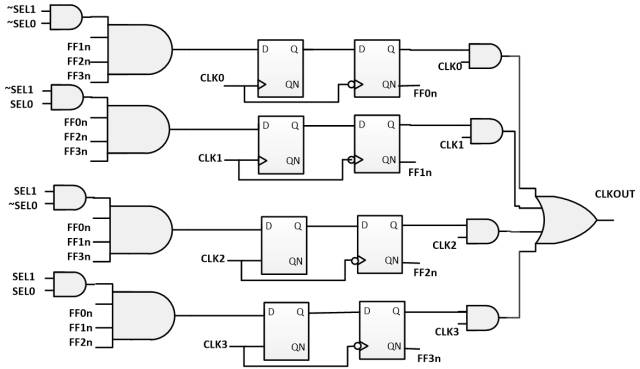

到這里我們已經掌握了實現兩個時鐘切換的電路設計的基本思路,那如果有三個甚至更多時鐘相切換又該怎么辦?沿襲以上設計思路,將該電路結構進行擴展,每一路雙鎖存輸出都相互交叉反饋即可,圖4以四個時鐘切換為例,給出了電路結構圖。

圖 4

以上就完成了時鐘切換基礎設計,總結一下大家需要知道,多時鐘系統已經廣泛應用,在進行時鐘轉換設計時, 1、單純采用MUX對時鐘做選擇是不行的; 2、圖3所示的時鐘切換電路能夠以較小的消耗而消除時鐘切換時的毛刺; 3、該時鐘切換電路結構可擴展,可按照這樣的設計思路設計多選一時鐘切換電路; 4、如果是異步時鐘還要插入雙鎖存結構消除亞穩態。

審核編輯:劉清

-

分頻器

+關注

關注

43文章

447瀏覽量

50074 -

時鐘發生器

+關注

關注

1文章

202瀏覽量

67404 -

時鐘芯片

+關注

關注

2文章

253瀏覽量

39972

原文標題:你不可不知的——時鐘切換電路

文章出處:【微信號:芯司機,微信公眾號:芯司機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

LMK04828-EP參考時鐘自動切換的問題求解答

kvm切換器怎么實現鍵盤熱鍵切換

如何處理時鐘電路的常見故障

時鐘抖動和時鐘偏移的區別

電源切換開關芯片怎么接

電源切換芯片怎么設置

繼電器的基本電路詳解

如何在PSoC? 4000S上使用外部時鐘而不是內部時鐘?

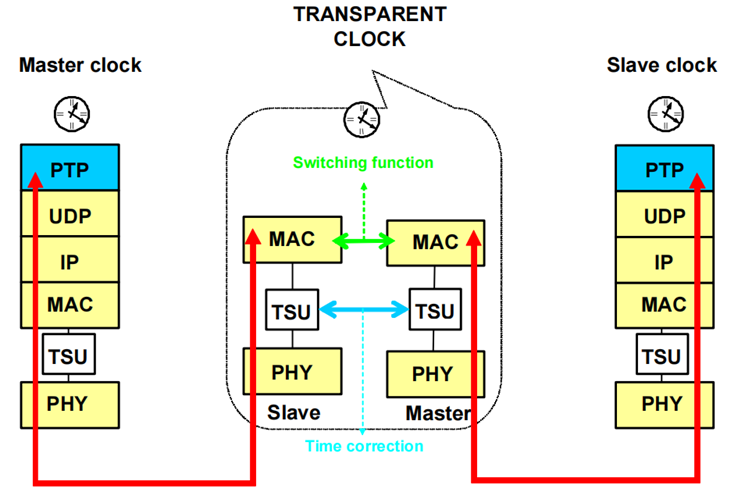

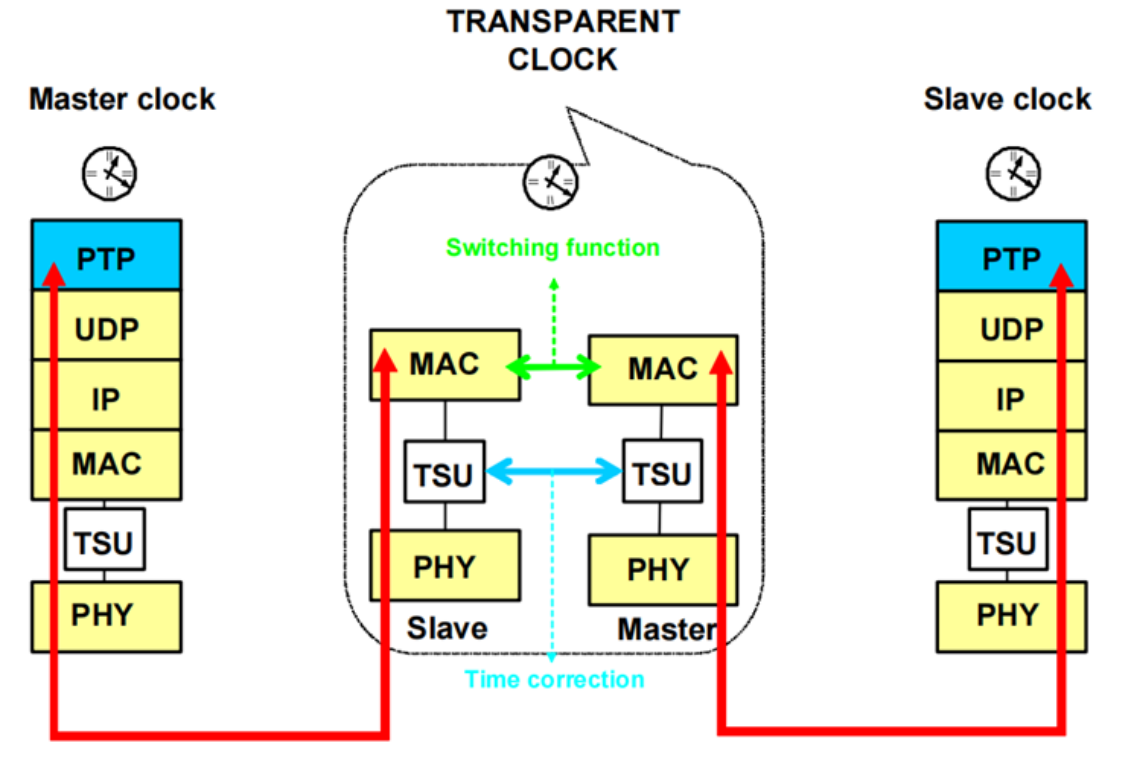

虹科技術|PTP時鐘源設備全攻略:從普通時鐘到透明時鐘的進階之路

虹科技術丨PTP時鐘源設備全攻略:從普通時鐘到透明時鐘的進階之路

PTP時鐘源設備全攻略:從普通時鐘到透明時鐘的進階之路

探討時鐘切換電路的實現

探討時鐘切換電路的實現

評論