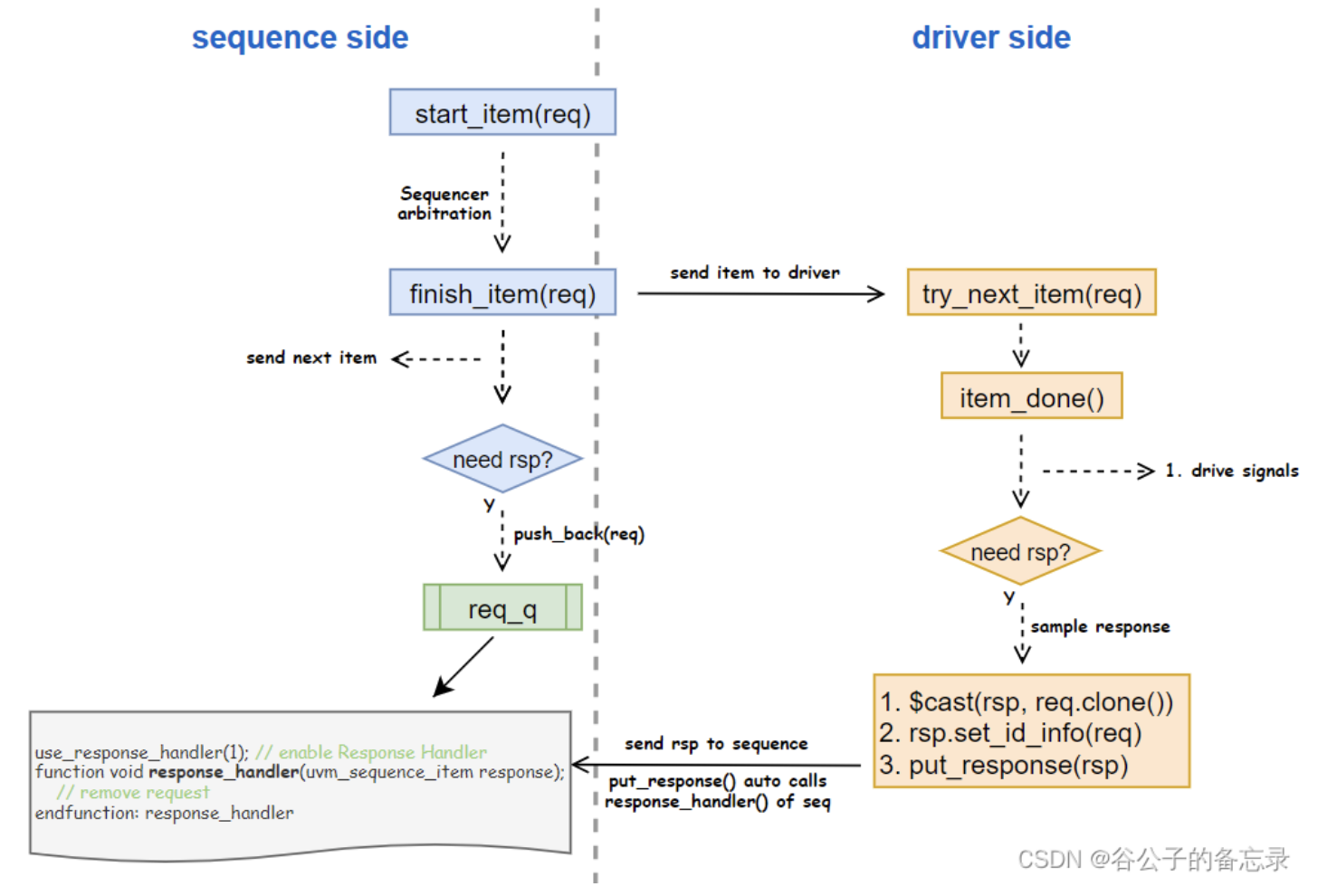

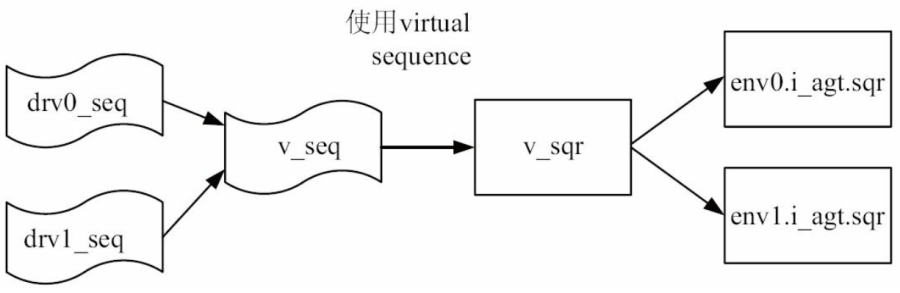

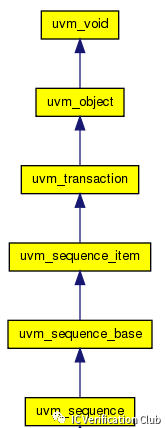

sequence作為UVM幾個核心機制之一,它有效地將transaction的產(chǎn)生從driver中剝離出來,并且通過和sequencer相互配合,成功地將driver的負擔降低至僅聚焦于根據(jù)協(xié)議將transaction發(fā)送到接口上,而具體發(fā)送什么數(shù)據(jù)、數(shù)據(jù)有多少,則通通交給了sequence和sequencer解決。

對于發(fā)送數(shù)據(jù),建立起了 sequence → sequencer → driver → interface → DUT 的單向數(shù)據(jù)傳輸通路。

但有時,sequence并不能著急產(chǎn)生數(shù)據(jù),而需要根據(jù)driver對transaction的反應(yīng),或者說sequence需要接收到driver發(fā)出的”我準備好了,你可以根據(jù)我目前的情況決定下一筆發(fā)送什么數(shù)據(jù)了“的信號,再產(chǎn)生transaction發(fā)送給driver。此時就需要建立起 driver → sequencer → sequence的通路,通路中傳輸?shù)?a target="_blank">信息即”rsp”。這是通過在driver中調(diào)用put_response( ),在sequencer中調(diào)用get_response( )實現(xiàn)的。同時,為了保證sequencer上有多個sequence時,rsp不會認錯sequence,最好給rsp設(shè)置好id等信息。

下面是小杜今天遇到的場景:

通過SMBus轉(zhuǎn)APB總線向DUT中發(fā)送read請求和address信息發(fā)送給DUT,DUT隨后將目標地址的寄存器中的數(shù)據(jù)反向發(fā)送出來,并且當監(jiān)測到rsp中某個關(guān)鍵信息滿足特定條件時,即可停止仿真。

停止仿真可以通過調(diào)用系統(tǒng)函數(shù)$finish( )實現(xiàn),但如何監(jiān)測rsp中具體某一位數(shù)據(jù)呢?

首先我們需要確定rsp 的數(shù)據(jù)類型,可以通過systemverilog的系統(tǒng)函數(shù)$typename( )來查看:

task body;...get_response(rsp, req.get_transaction_id());$display($typename(this.rsp));...endtask

打印結(jié)果:

class xxx.xxx_master_transaction

可以看到,返回的rsp是一個類,并且和我們發(fā)送的req是同一個類型。想一下也合理,req、rsp是建立在同一條數(shù)據(jù)通路上的,只是數(shù)據(jù)傳輸方向相反。即sequence sequencer driver interface DUT 是一條完整的雙向數(shù)據(jù)通路。(這是小杜目前的理解,如有錯誤,還請批評指正)

下面是整個body( )代碼:

task body;//發(fā)送數(shù)據(jù)`uvm_create_on(req, sequencer)...//對req進行處理`uvm_send(req)//獲取返回值并打印get_response(rsp, req.get_transaction_id());$display("rsp = ", rsp);//監(jiān)控并判斷rsp的具體位,滿足條件就停止仿真if(rsp.data[x] == 'hxx) begin$finish();endendtask: body

-

芯片

+關(guān)注

關(guān)注

456文章

51170瀏覽量

427245 -

Response

+關(guān)注

關(guān)注

0文章

5瀏覽量

7980 -

UVM

+關(guān)注

關(guān)注

0文章

182瀏覽量

19227 -

sequence

+關(guān)注

關(guān)注

0文章

23瀏覽量

2862

原文標題:日常 - UVM sequence機制中response的簡單使用

文章出處:【微信號:小杜的芯片驗證日記,微信公眾號:小杜的芯片驗證日記】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

UVM中的field automation機制有哪些用途

IC驗證“UVM驗證平臺加入objection機制和virtual interface機制“(七)

數(shù)字IC驗證之“搭建一個可以運行的uvm測試平臺”(5)連載中...

UVM sequence分層有哪幾種方式呢

請問一下在UVM中的UVMsequences是什么意思啊

UVM sequence分層的幾種體現(xiàn)

如何配置sequence的仲裁算法和優(yōu)先級及中斷sequence的執(zhí)行

介紹兩種交互方法來完成Sequencer和Driver的握手機制

sequence item實際應(yīng)用中應(yīng)該包含哪些東西

UVM中seq.start()和default_sequence執(zhí)行順序

淺談UVM之sequence/item見解(上)

UVM response_handler和get_response機制

UVM中sequence的那些事兒

UVM sequence機制中response的簡單使用

UVM sequence機制中response的簡單使用

評論