關于增量編譯

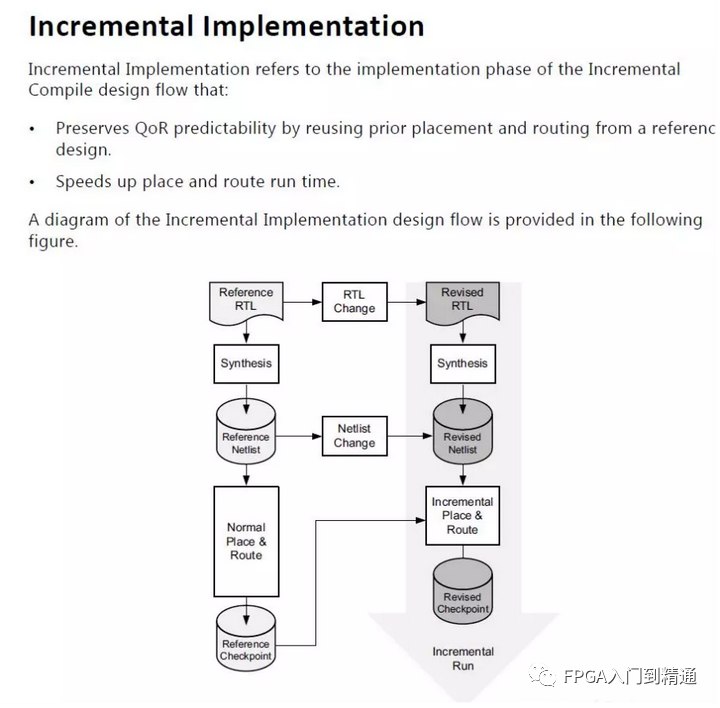

所謂增量實現,更嚴格地講是增量布局和增量布線。它是在設計改動較小的情形下參考原始設計的布局、布線結果,將其中未改動的模塊、引腳和網線等直接復用,而對發生改變的部分重新布局、布線。

這樣做的好處是顯而易見的,即節省運行時間,能提高再次布局、布線結果的可預測性,并有助于時序收斂。

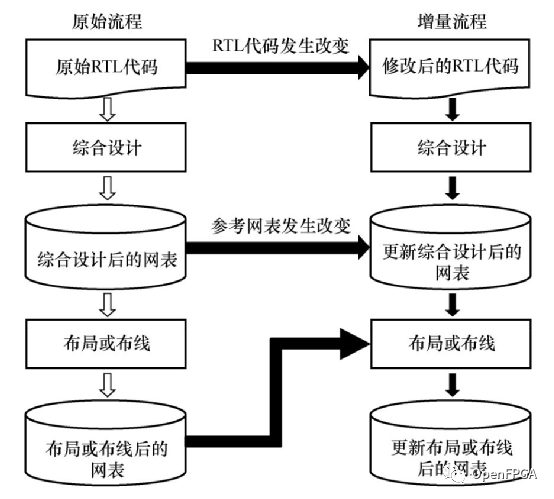

增量實現由兩個流程構成:原始流程和增量流程,如圖所示。其中,原始流程提供網表。這里的網表可以是布局后的DCP文件,也可以是布線后的DCP文件。

增量實現流程有兩種模式:高復用模式和低復用模式。在高復用模式下,布局、布線會盡可能地復用已有布局、布線的結果。

在這種情形下,place_design和route_design都只有三種directive可用,分別為Default、Explore和Quick。 以下兩種情形適合于高復用模式。

情形1:很小的設計改動。

情形2:與原始設計相比,更新后的設計只是添加了調試模塊,如ILA等。 由此可見,高復用模式在網表時序收斂且多達95%的邏輯單元被復用時最為有效。

與高復用模式相比,低復用模式則適用于更新后的設計與參考設計相比有較大的改動,或者用戶通過read_checkpoint的選項?reuse_objects指定復用邏輯單元的情況。此時,place_design和route_design的所有?directive均可用。

當布局、布線在某些區域面臨挑戰時,低復用模式更為有效。例如,從網表中獲得較好的Block RAM和DSP的布局,或者時序難以收斂的邏輯單元。這些都可通過Tcl命令獲得。

一般來說,增量編譯都是與設計鎖定聯合使用的。

設計鎖定與增量編譯方法

為了實現對模塊的布局(place)、布線(route)的鎖定,僅適用增量編譯是不夠的,因為增量編譯的本質目的是為了實現編譯時間的縮短,還需要引入設計鎖定,設計鎖定的TCL命令是:lock_design –level routing

下面例說操作方法。

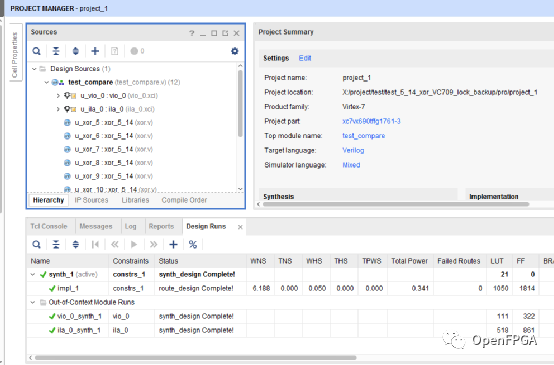

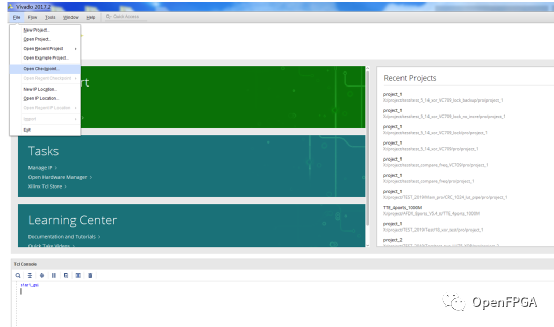

(1)建立工程:建立一個工程,走完綜合實現的流程,如圖1所示,該工程將作為樣例工程(工程名:incre_compile_demo),將該工程備份一份(工程名:initial_project,后面對比要用到這個工程);

圖1 建好的工程

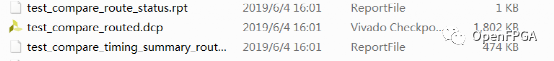

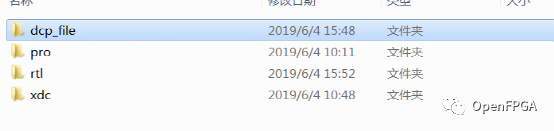

(2)找到dcp文件:增量編譯需要有一個參考文件,這個參考文件是“參考設計”實現之后生成的,后綴是“.dcp”,該文件的路徑一般在“.. project_1project_1.runsimpl_1”路徑下,如圖2所示,新建一個文件夾(名字是dcp_file),將該文件復制到其中,如圖3所示;

圖2 dcp文件

圖3新建文件夾,復制dcp文件

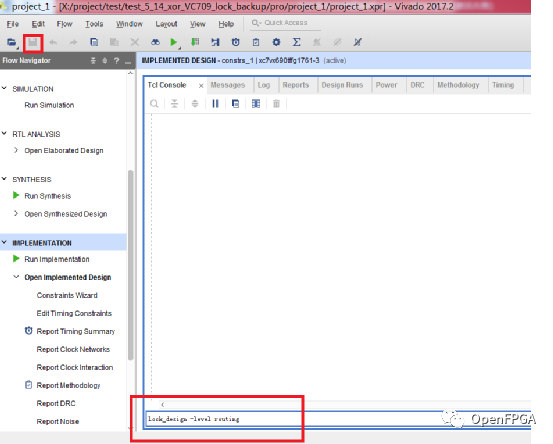

(3)鎖定設計:前面說道,簡單的增量編譯是不能保證模塊固定在某個位置的,為了實現這一點,需要對設計進行鎖定,方法是,打開一個新的Vivado界面,然后打開dcp_file文件夾下的dcp文件(注意選擇“open checkpoint”),如圖4所示;打開后,在TCL Console中輸入命令:“lock_design –level routing”,點擊左上角保存,如圖5所示,做完這一步后,設計就鎖定好了,dcp文件就可以用了;

圖4 vivado打開dcp界面

圖5 鎖定設計并保存

(4)增量編譯:

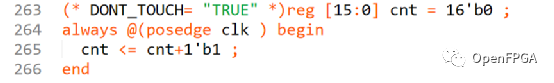

1)修改代碼,將頂層模塊(test_compare.v)line263-line266注釋取消,保存,如圖6所示;

2)在主界面菜單欄處,點:Flow > Create Runs;

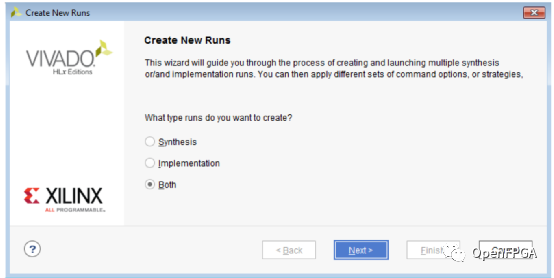

3)選both,點next,如圖7所示;

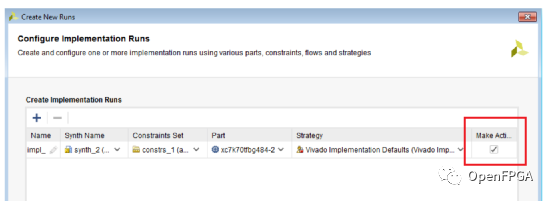

4)勾選make active,點next,如圖8所示;

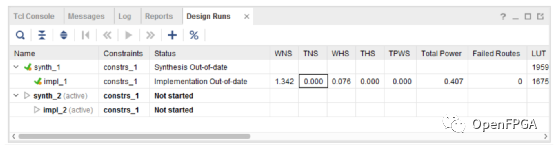

5)選Do not launch now,點next,如圖9所示; 6)完成后如圖10所示;

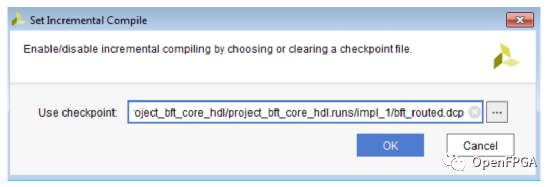

7)在impl_2右鍵,選擇“Set Incremental Compile”,選擇步驟(3)中準備好的dcp文件,示意圖如圖11所示(注意這只是一個示意圖,圖中選的文件不是步驟(3)準備好的那個文件)

8)開始綜合、實現,完成增量編譯過程。

圖6 改代碼

圖7 選both

圖8 make active

圖9 Do not launch now

圖10 新的run已建好

圖11 選擇參考dcp文件

3、正確性驗證

怎么證明增量編譯后,原始設計成功鎖定了呢?我們來做一個對照實驗。

樣本1:原始工程,名稱是: initial_project;

樣本2:增量編譯工程,名稱是: incre_compile_demo;

樣本3:原始工程復制一份出來,不進行增量編譯,直接修改代碼(見圖6),重新綜合實現,名稱是:modify_project。

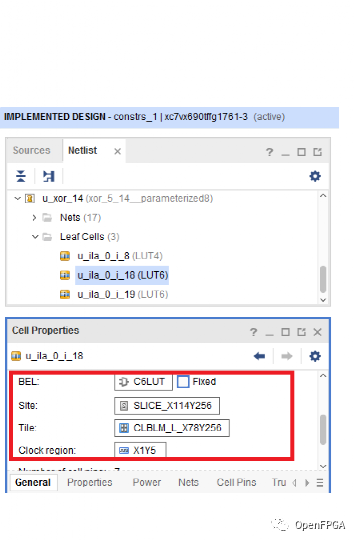

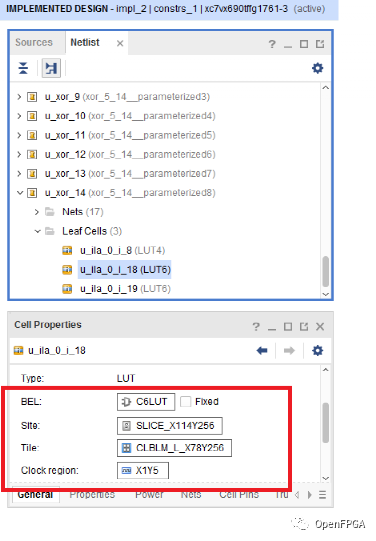

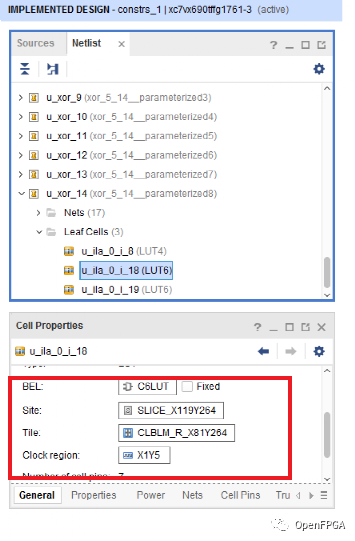

打開三個工程,之后open implemented design,選取幾個模塊,觀察其在FPGA上的位置,發現樣本1和樣本2位置完全一樣,而樣本3和前兩個樣本不一樣,說明設計鎖定是成功的,如圖12、13、14所示。

圖12 樣本1位置觀察

圖13 樣本2位置觀察

圖14 樣本3位置觀察

Vivado下如何鎖定設計的模塊的布局布線

Xilinx官方論壇上也有相關問題的回答。

Vivado下如何鎖定設計模塊的布局布線 問題: 我現在設計了一個延時模塊,應用后需要把該模塊的布局和布線全部鎖定,然后在別的項目中直接調用。現在布局沒有問題。可以通過約束文件來鎖定,就是布線不能大范圍鎖定,否則應用時會失敗。

我已經嘗試過增量編譯(調用DCP文件)的功能,發現在增量編譯中布局布線并不是全部不變的,個別走線也是會變的。

請問有辦法把布線也固定下來嗎?(Tool: Vivado17.3 Device: K7)

回答1:如果你用的是Ultrascale/Ultrascale+ , 我覺得PR是個不錯的選擇,你的目標模塊可以放在靜態部分,只占據很小的一塊面積,剩下大塊的動態部分.但是7系列有很多primitive不能放在動態,靜態的部分包含的邏輯過多,剩下供你修改的邏輯偏少,不太適合目前的應用場景.

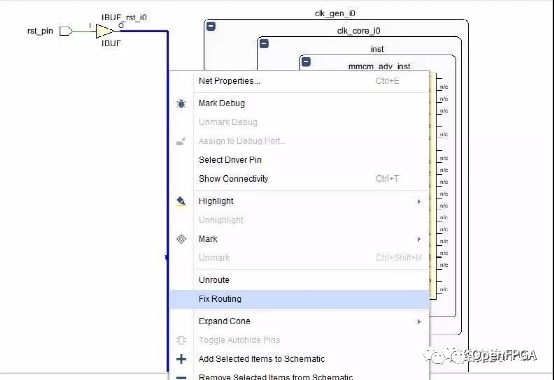

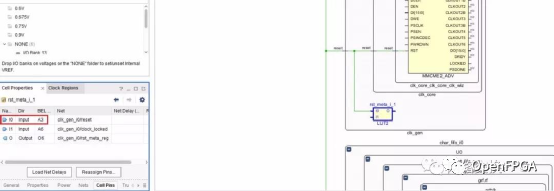

回答2:關于鎖定某一個net的布線路徑,請參考以下步驟:

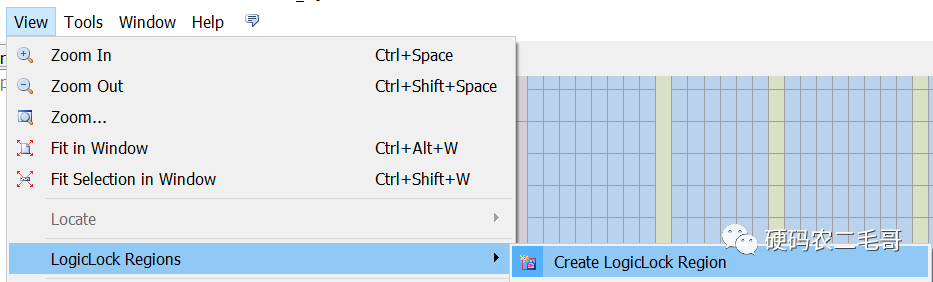

1.打開跑完布局布線的工程,Open Implemented Design

2.找到你要鎖定布線的net,選中,右鍵菜單點擊Fixed Routing,如下圖所示:

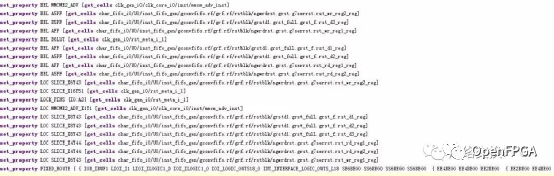

3. Tcl Console里面會打印出一些命令,然后在Tcl Console里面敲命令:write_xdc/dirt.xdc

4. 打開導出的xdc,在最下面的部分會有所有元件的位置鎖定以及FIXED_ROUTE,示例如下:

5. 另外還需注意的是,負載中有LUT的話需要將LUT的輸入pin也鎖住。以下圖的LUT2為例,在其property窗口中找到Cell pins,信號是連到LUT2的I0端,映射到BEL pin是A3。

因此上述導出的位置鎖定約束中還有一個LOCK_PINS的設置:

set_property LOCK_PINS {I0:A3} [get_cells clk_gen_i0/rst_meta_i_1] 6. 將這部分有關鎖定的約束拷貝到你工程的約束文件中,重新跑implementation,這條線會按照原先的結果布。

溫馨提示: 我們并不建議完全鎖死某個模塊的所有布線,當合入的工程比較復雜,用到的布線資源較密集時,工具沒有靈活性去調整和優化,有很大的概率會布線失敗。

劃分靜態區和動態區

除了上述的邏輯鎖定方法之外,Xilinx 的FPGA還提供了靜態區和動態區的劃分也可以實現邏輯的鎖定。只不過靜態區占據了大多數的空間,動態區是可以隨意修改的小部分空間。

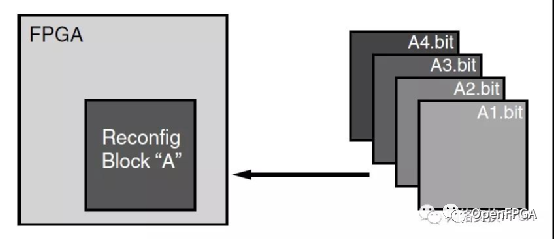

FPGA提供了現場編程和重新編程的靈活性,無需通過改進的設計進行重新制造。部分重配置(PR)進一步提高了這種靈活性,允許通過加載部分配置文件(通常是部分BIT文件)來修改操作FPGA設計。

在完整的BIT文件配置FPGA之后,可以下載部分BIT文件以修改FPGA中的可重配置區域,而不會影響在未重新配置的設備部分上運行的應用程序的完整性。

部分可重構的基本前提

如圖所示,通過下載幾個部分BIT文件A1.bit,A2.bit,A3.bit或A4.bit中的一個來修改在重新配置塊A中實現的功能。

FPGA設計中的邏輯分為兩種不同的類型,可重構邏輯和靜態邏輯。FPGA塊的灰色區域表示靜態邏輯,標記為Reconfig Block“A”的塊部分表示可重配置邏輯。靜態邏輯仍然有效,并且不受加載部分BIT文件的影響。可重配置邏輯由部分BIT文件的內容替換。

為什么在單個FPGA器件上動態地對多個硬件進行時間復用的能力是有利的。

這些包括:

?減小實現給定功能所需的FPGA器件尺寸,從而降低成本和功耗

?為應用可用的算法或協議選擇提供靈活性

?實現設計安全性的新技術

?提高FPGA容錯能力

?加速可配置計算 除了減小尺寸,重量,功耗和成本之外,部分重配置還可以實現沒有它的新型FPGA設計。

審核編輯:劉清

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26628 -

RAM

+關注

關注

8文章

1369瀏覽量

115002 -

DCP

+關注

關注

0文章

30瀏覽量

17287 -

Vivado

+關注

關注

19文章

815瀏覽量

66887

原文標題:Vivado中增量編譯與設計鎖定

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Vivado中的Incremental Compile增量編譯技術詳解

Vivado Design Suite 2015.3的新功能介紹

Vivado Design Suite 2015.3新增量編譯功能介紹

淺析Vivado中增量編譯與設計鎖定方法與驗證

Vivadoz中增量編譯與設計鎖定

Vivado增量編譯的基本概念、優點、使用方法以及注意事項

Vivado中設計鎖定與增量編譯方法簡析

Vivado中設計鎖定與增量編譯方法簡析

評論