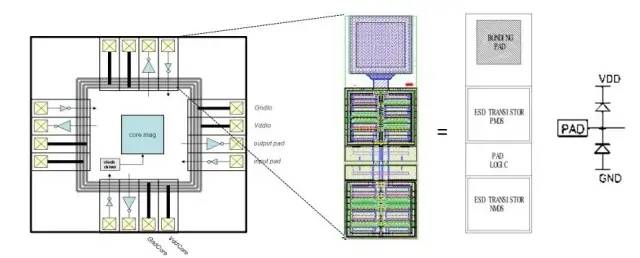

每當我們做好了core的電路和版圖,下一步就是設計pad ring了。對于第一次接觸pad ring的同學來說,這個概念可能會有點陌生。

IO總的來說由兩部分組成,一個是PAD,一個是電路。電路又分為pre 和 post。

PAD的作用是為了封裝的時候連接金線。因此,為了防止金線短路,要求PAD之間要有最小距離,具體數(shù)值要看你的封裝形式。

電路的作用有幾方面:ESD保護,level shifter,施密特觸發(fā)器等等。還有提供電源環(huán)路。

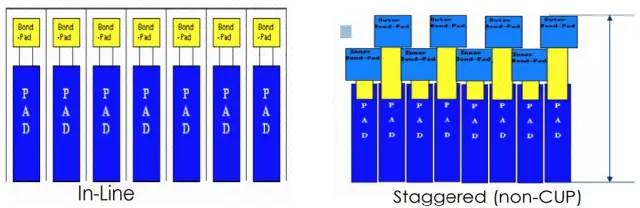

二者合在一起構(gòu)一個IO(也就是I/O pad),有的時候PAD和電路是分開,stagger就是這種情況,在IO limiter的情況下,為了節(jié)省面積,將PAD分成兩排甚至三排交錯的排列,但是電路必須是在一條直線上的(因為電源環(huán)路的需求)。

Bonding pad是連接芯片和封裝線的地方,ESD保護電路一般包括一對很大的反偏的PMOS,NMOS

作者君的珍藏,之前用電子顯微鏡查看引腳是否有短接,每個打孔的地方就是上圖里面bonding pad

一個基本的pad library,應該可以提供如下幾種pad:

給pad供電的pad,例如:PAD_VDD, PAD_VSS;

給core供電的pad,例如:VDD, VSS; (如果存在多個VDD domain, 還有AVDD, AVSS,之類的pad)

模擬信號的pad,例如ANIN (analog的pad一般就是一塊鐵片,有的vendor推薦用戶可以自己基于要求自己再加上一定的ESD保護電路)

數(shù)字信號的pad,一般有input和output的區(qū)別,里面還有包括level shifter,buffers之類的數(shù)字電路(作者君用的不多,這里不展開說明了)。

建議設計pad ring之前,先去讀一下vendor的文檔,文檔一般會說明各種類型的pad的用法,還有各種注意事項。不同的vendor提供的pad library不一樣,所以有時候還是謹慎一點。

比如作者君最近用的一個pad library,里面有一種特定的提供PAD_VDD的pad,這個pad起到了類似POR的作用,它自己稱之為POC(power on control)。這個pad會監(jiān)控各個VDD的上升情況,只有當PAD_VDD, VDD之類的電源都基本上穩(wěn)定了,它才會讓core被最終供電。同時,文檔里面還寫了VDD的上升速度不可以太快(小于2us)之類的要求。(其實寫到這里,作者君想到core的transient仿真里面,也需要模擬這個VDD的上升過程)

一般來說,pad ring會設計成一個方形或者矩形,這樣給pad 供電的PAD_VDD, PAD_VSS可以比較均勻的分布在pad ring里面。當然,有時候遇到電路里面有高壓的模塊,可能不能share整個pad ring,那么pad ring就可能只有方形的三面,也是合理的。

相鄰的pad之間需要隔開還是可以緊密挨著,主要是取決于最后封裝時候的要求。舉個例子,比如每個pad 的寬度是50um,但是封裝引腳的最小距離是80um,那么相鄰的pad之間就需要加filler(一種特定的cell,里面的PAD_VDD, PAD_VSS是連續(xù)的)同時,每個轉(zhuǎn)角處還有專門的Corner cell,也是保證了pad ring里面ESD相關的信號的連續(xù)性。

首先需要確定的是關鍵的信號pad的位置,比如“盡量縮短走線長度”,讓pad靠近layout core里面的信號pin的位置。(舉個例子,如果做的test chip的core不大,可以選擇core的位置靠近pad,不一定要正好在pad ring的正中間)。獨立的敏感信號比如clock或者bidirectional pin與其他的switching pad之間,可以加入power或者ground的pads隔開,原理類似layout里面的signal shielding。

幾個相鄰的pad其實可以共享一個封裝引腳pin(比如幾根金線從幾個pad上連到同一個封裝pin上面),因為封裝pin可以承受的電流一般大于pad的電流(比如一個pad電流最大是30mA)。同時,bonding wire有寄生電感,而電源上的變化電流可能會很大,并聯(lián)很多條boding wire等于減小了寄生電感。

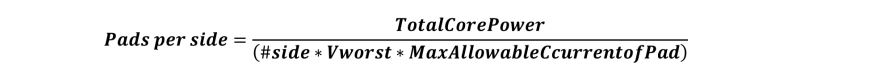

在可能的前提下,盡量多放power pad(可以減小bonding wire的彈跳效應),并讓power pad均勻分布。然后是確定所需的電源pad的數(shù)量。用下面的公式粗略估計一下,比如總的電流是120mA,然后pad ring的四條邊都加上VDD和VSS的pad,每個vdd pad的最大電流是30mA,如果Vworst和core power里面的電源電壓一樣大,那么每邊一個pad就足夠了。如果這兩個電壓值不一樣,則應該增加vdd pad的數(shù)量。

VDD/VSS pad的數(shù)量計算

當然,如果面積有限,單層的inline pad ring放不下,還可以使用staggered的方式,也就是下面右圖里面那種交叉擺放的方式。

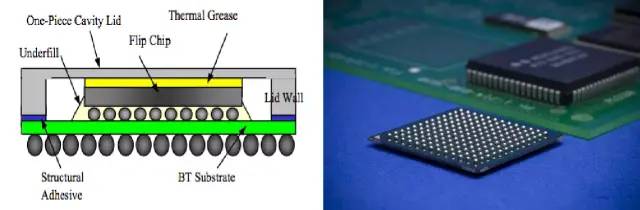

最后,多說幾句package的基礎知識,除了常見的dual-flat no-leads (DFN),dual in-line package (DIP)這些封裝,現(xiàn)在還有Flip Chip with RDL,其中用到了一層Redistribution Layer (RDL),也就沒有上面那些封裝里面的金線了。對于超大規(guī)模的電路,F(xiàn)lip Chip現(xiàn)在已經(jīng)很常見了。

傳統(tǒng)封裝方式

flip chip封裝

審核編輯:劉清

-

ESD

+關注

關注

49文章

2064瀏覽量

173371 -

保護電路

+關注

關注

46文章

899瀏覽量

101779 -

PAD

+關注

關注

1文章

100瀏覽量

30769 -

觸發(fā)器

+關注

關注

14文章

2003瀏覽量

61346

原文標題:一點的關于pad的基礎知識分享

文章出處:【微信號:analogIC_gossip,微信公眾號:通向模擬集成電路設計師之路】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

創(chuàng)建一個PLC設計方案

【資料分享】STM32設計方案與示例分享 第一波

STM32設計方案與示例分享

希望提供一個信號源的設計方案或推薦一款DDS芯片?

買一個免驅(qū)USB攝像頭的pcb設計方案,包含具體的電路

求一個基于DDC芯片的接口設計方案

一個全自動洗衣機的設計方案

大聯(lián)大世平集團推出基于NXP產(chǎn)品的無死角消毒觸碰界面設計方案

一個基本的pad library設計方案

一個基本的pad library設計方案

評論