JTAG是1980年代開發的用于解決電子板制造問題的IEEE標準(1149.1)。如今,它可以用作編程,調試和探測端口。但是首先,讓我們看看JTAG的最初用途,邊界測試。

邊界測試

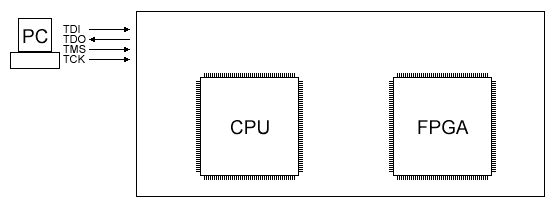

這是一個簡單的電子板(也稱為“印刷電路板”的“ PCB”),帶有兩個IC(“集成電路”),一個CPU和一個FPGA。典型的電路板可能具有更多的IC。

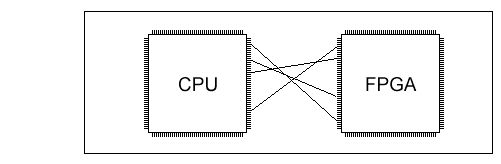

IC可以有很多引腳。因此,當然,IC通過大量連接(PCB traces)連接在一起。這里只顯示四個。但是可以輕松地在PCB上放置幾千個。

現在,如果您構建一千個板,每個板具有數千個連接,則不可避免地會有一些不良板。如何測試所有這些板?必須確保所有這些連接都正確。不能只手動測試所有這些連接。這樣就創建了JTAG。

JTAG可以控制(or hijack)所有IC的引腳。在圖片上,也許JTAG將使所有CPU引腳輸出,以及所有FPGA引腳輸入。然后,通過從CPU引腳發送一些數據,并從FPGA引腳讀取值,JTAG可以確保電路板連接良好。

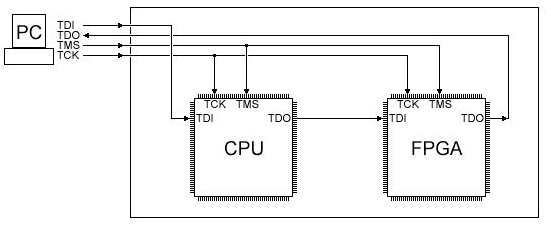

現在,JTAG實際上包含四個邏輯信號,分別為TDI,TDO,TMS和TCK。從PC的角度來看,這是三個輸出和一個輸入。

◇TCK:時鐘信號,為TAP的操作提供了一個獨立的、基本的時鐘信號。

◇TMS:模式選擇信號,用于控制TAP狀態機的轉換。

◇TDI:數據輸入信號。

◇TDO:數據輸出信號。

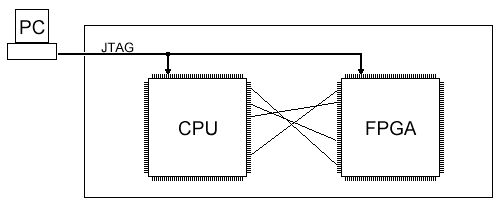

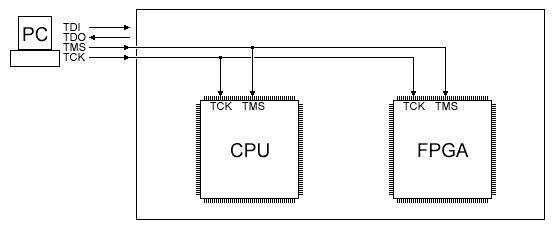

這四個信號需要以特定方式進行布線。首先,TMS和TCK與所有JTAG IC并聯。

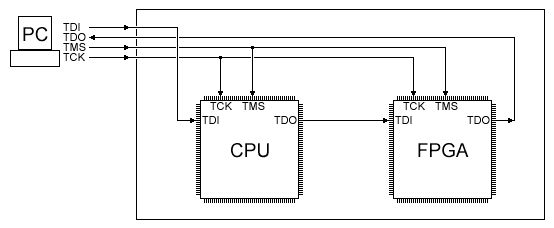

然后將TDI和TDO并連接起來,形成一條鏈。用JTAG術語,您經常會聽到“ JTAG-chain”一詞的來歷。

如您所見,每個符合JTAG的IC都有四個用于JTAG的引腳(三個輸入和一個輸出)。名為TRST的第五個引腳是可選的(JTAG復位)。JTAG引腳通常是專用的(不共享用于其他目的)。

所有大型IC都使用通過JTAG進行的邊界測試-邊界測試是創建JTAG的最初原因。如今,JTAG的使用已得到擴展,以允許進行諸如配置FPGA之類的操作,然后在FPGA內核內部使用JTAG進行調試。

審核編輯:郭婷

-

集成電路

+關注

關注

5392文章

11622瀏覽量

363177 -

pcb

+關注

關注

4326文章

23160瀏覽量

399949 -

JTAG

+關注

關注

6文章

401瀏覽量

71841

原文標題:什么是JTAG?

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

JacintoTM 7家族HS芯片中的JTAG加解鎖控制

Samtec小課堂 | 兩分鐘了解JTAG連接器

如何使用JTAG來調試ESP-12模塊?

windows下無法進行jtag的驅動設置,是需要將jtag相關的IO接到jtag調試器后再到PC進行設置嗎?

RISCV soft JTAG調試_v1.2

易靈思Jtag_bridge_loader生成-v2

stm32 JTAG和普通IO復用,當軟件設置為普通IO時,還能用JTAG下載軟件嗎?

RISCV soft JTAG調試_v1.1

什么是JTAG?用途是什么

什么是JTAG?用途是什么

評論