首先看下下面的這個示例:

module PU;

int A[2:0][3:0][4:0], B[2:0][3:0][4:0], C[5:0][4:0];

initial

begin

A[0][2][4] = 1024; //row 0, column 2, element #4

//display index #4 (i.e., 5th element)

$display("A[0][2][4]=",A[0][2][4]);

//display 5 elements of row 0, column 2

$display("A[0][2]=",A[0][2]);

//display row 0 (4 columns; 5 elements each)

$display("A[0]=",A[0]);

//display 3 rows * 4 columns of 5 elements each

$display("A=",A);

$display("

");

B[1][1][1]=512; //row 1; column 1; element #1

// assign a subarray composed of fve ints

A[2][3] = B[1][1];

//display 5 elements of row 2, column 3

$display("A[2][3]=",A[2][3]);

B[0][0][0]=128; //Assign only to the last unpacked element

A[1] = B[0];

$display("

");

$display("A[1]=",A[1]); //display row 1 (4 columns; 5

elements each)

C[5][4]=64;

A[0][1] = C[5];

$display("

");

$display("C[5]=",C[5]);

$display("A[0][1]=",A[0][1]);

end

endmodule

仿真log:

A[0][2][4]= 1024 //index #4 (i.e., 5th element)

A[0][2]='{1024, 0, 0, 0, 0} //5 elements of row 0, column 2

A[0]='{'{0, 0, 0, 0, 0}, '{1024, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}

//4 columns of row 0 with value assigned to column 2, element #4 (5th position)

A='{'{'{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}, '{'{0, 0, 0, 0,

0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}, '{'{0, 0, 0, 0, 0}, '{1024, 0, 0,

0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}}}

//Entire 3 rows*4 columns (12 entries – 5 elements each with value assigned to

column 2, element #5)

A[2][3]='{0, 0, 0, 512, 0} // display 5 elements of row 2, column 3

A[1]='{'{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 0}, '{0, 0, 0, 0, 128}}

// display row 1 (4 columns; 5 elements each)

C[5]='{64, 0, 0, 0, 0} //Row 5, 5 elements with index 4 assigned

A[0][1]='{64, 0, 0, 0, 0} //Row 0, column 1 of 5 elements

V C S S i m u l a t i o n R e p o r t

Packed和Unpacked數組作為子程序的參數

數組可以作為參數傳遞給子程序,當數組作為值傳遞給子程序時,會將這個數組復制一份傳遞給子程序。

task trial (int a[3:1][3:1]); //’a’ is a two-dimensional array

//(2-D unpacked)

上面是一個SystemVerilog task聲明的示例,該task會將一個2維unpacked數組作為參數值傳遞。

int b[3:1][3:1]; // OK: same type, dimension, and size

int b[1:3][0:2]; // OK: same type, dimension, & size

// (different ranges)

logic b[3:1][3:1]; // ERROR: incompatible element type

// (logic vs. int)

event b[3:1][3:1]; // ERROR: incompatible type (event

vs. int)

int b[3:1]; // ERROR: incompatible number of dimensions

int b[3:1][4:1]; // ERROR: incompatible size (3 vs. 4)

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Verilog

+關注

關注

28文章

1351瀏覽量

110390 -

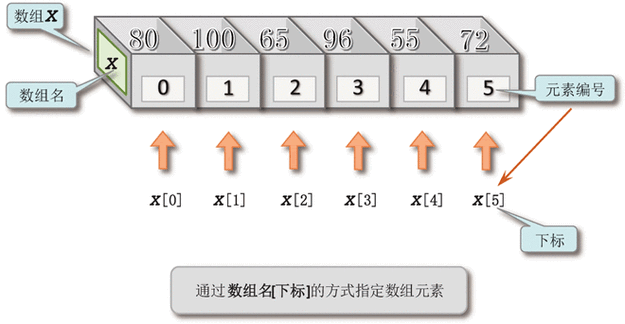

數組

+關注

關注

1文章

417瀏覽量

26027

原文標題:SystemVerilog中數組的賦值、索引和切片

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

創建唯一索引的SQL命令和技巧

在創建唯一索引時,以下是一些SQL命令和技巧,可以幫助優化性能: 使用合適的索引類型:對于需要保證唯一性的列,使用UNIQUE索引來避免重復數據的插入。 這可以確保列中的值是唯一的,同

Labivew 實現鼠標在數組中選中元素時,精準的顯示所在位置的行、列值方法

在項目開發中,遇到一個布爾的二維數組輸入控件,選中數組元素并索引出行列的操作,試過其他大佬的方法,不是特別精準,,嘗試一下還可以,分享給需要的朋友

*附件:選中二維

發表于 12-21 18:07

數組名之間可以直接賦值嗎

數組之間的賦值能不能直接使用等于號?比如這樣的代碼。 int main(){ int a[5] = {1, 2, 3, 4, 5}; int b[5] = {0}; b = a

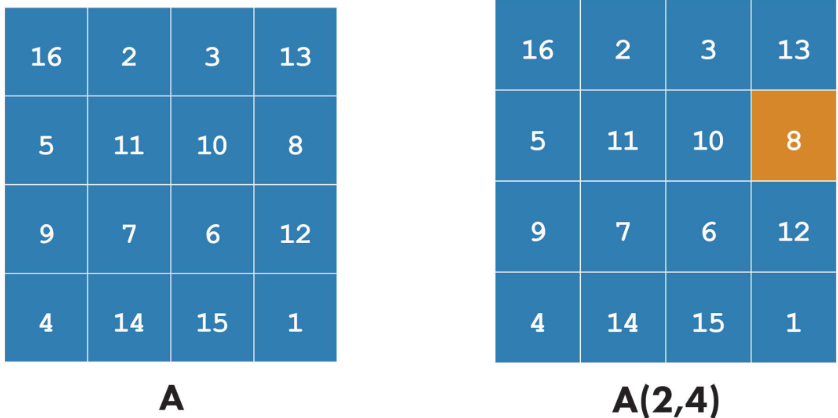

MATLAB中的矩陣索引

對矩陣進行索引是從矩陣中選擇或修改部分元素的一種方式。MATLAB 有幾種索引樣式,它們不僅功能強大、靈活,而且可讀性強、表現力強。矩陣是 MATLAB 用來組織和分析數據的一個核心組件,索引是以可理解的方式有效操作矩陣的關鍵。

labview字符串數組轉化為數值數組

在LabVIEW中,將字符串數組轉換為數值數組是一項常見的任務,尤其是在處理數據采集、信號處理或用戶輸入時。 1. 理解LabVIEW的數據類型 在開始之前,了解LabVIEW中的數據

一文了解MySQL索引機制

的呢?一起靜下心來,耐心看完這篇文章吧,干貨不啰嗦,相信你一定會有所收獲。 一、索引模型 模型也就是數據結構,常見的三種模型分別是哈希表、有序數組和搜索樹。 了解MySQL的朋友已經知道,現在MySQL默認使用的是InnoDB存儲引擎,使用的是

嵌入式中零長度數組基本操作方法

C語言零長度數組,聽起來可能有點奇怪,因為它沒有分配內存空間,無法存儲數據。但實際上,零長度數組在Linux內核中隨處可見。 零長度數組的定義 首先,我們要明白什么是零長度

在Vivado Synthesis中怎么使用SystemVerilog接口連接邏輯呢?

SystemVerilog 接口的開發旨在讓設計中層級之間的連接變得更加輕松容易。 您可以把這類接口看作是多個模塊共有的引腳集合。

mapgis如何給區屬性賦值

地進行數據分析和可視化。 在MapGIS中給區屬性賦值有多種方法,下面將詳細介紹其中的幾種常用方法。 1.手動賦值 手動賦值是最直接和簡單的方法。首先,在MapGIS

proteus屬性賦值工具怎么用

賦值工具的詳細使用方法。 一、打開Proteus軟件并建立電路圖 首先,打開Proteus軟件,并在工具欄上選擇“新建”。然后,在彈出的對話框中選擇電路圖的類型,例如“Schematic Capture”。 二、選擇元件添加到電路圖中 在Proteus軟件中,可以從庫中選

verilog同步和異步的區別 verilog阻塞賦值和非阻塞賦值的區別

Verilog是一種硬件描述語言,用于設計和模擬數字電路。在Verilog中,同步和異步是用來描述數據傳輸和信號處理的兩種不同方式,而阻塞賦值和非阻塞賦值是兩種不同的賦值方式。本文將詳

數組和鏈表在內存中的區別 數組和鏈表的優缺點

數組和鏈表在內存中的區別 數組和鏈表的優缺點? 數組和鏈表是常見的數據結構,用于組織和存儲數據。它們在內存中的存儲方式以及優缺點方面存在一些

SystemVerilog中數組的賦值、索引和切片

SystemVerilog中數組的賦值、索引和切片

評論