新技術(shù)和應(yīng)用,加上更緊密的封裝和更高的連接要求,推動(dòng)了當(dāng)前處理器及其電源系統(tǒng)的極限。這些處理器必須支持越來越多的音頻、視頻、高清 (HD) 圖形、流媒體、游戲以及介于兩者之間的所有內(nèi)容的計(jì)算。隨著內(nèi)容數(shù)量和質(zhì)量的提高,在更小空間內(nèi)提供更好性能的愿望也隨之提高。這種用戶驅(qū)動(dòng)的方法將集成推到了最前沿,使其成為技術(shù)發(fā)展的限制因素。

在降低成本的同時(shí)實(shí)現(xiàn)高性能的挑戰(zhàn)促使工程師開發(fā)片上系統(tǒng) (SoC) 集成電路 (IC)。這些解決方案將許多系統(tǒng)功能集成到 IC 中,從而降低功耗、成本和工作量以及技術(shù)知識(shí)實(shí)現(xiàn)需要深度領(lǐng)域?qū)I(yè)知識(shí)(如視頻和圖形處理)的功能。以合理的成本實(shí)現(xiàn)高性能要求制造商采用深亞微米(互補(bǔ)金屬氧化物半導(dǎo)體 (CMOS),≤ 16/14 納米)工藝開發(fā) SoC。

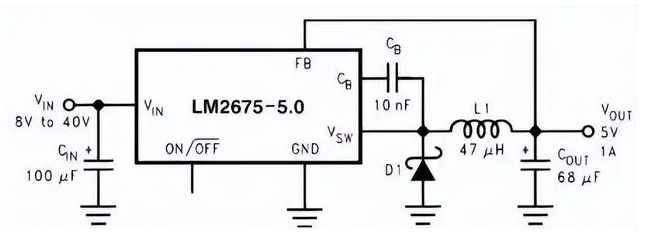

此類 SoC 需要電源提供高電流,這在先進(jìn)的亞微米 CMOS 工藝中可能是一個(gè)挑戰(zhàn)。電源電路需要大晶體管來處理高電流和承受高電壓(相對于數(shù)字核心電壓)。這些屬性與數(shù)字電路中使用的晶體管相關(guān)的屬性截然相反。因此,在與數(shù)字電路相同的裸片上實(shí)現(xiàn)電源在技術(shù)上具有挑戰(zhàn)性(或不可能),而且這樣做可能不經(jīng)濟(jì)。總的來說,這些不兼容性一直存在于 IC 設(shè)計(jì)中,但隨著現(xiàn)代處理器在不斷縮小的 CMOS 工藝中實(shí)現(xiàn),它們被放大了。

在這里,我們將通過 NXP i.MX 8M 系列處理器( Mini和Nano)和 ROHM BD71847 / BD71850 來說明 SoC-電源管理集成電路 (PMIC) 協(xié)同設(shè)計(jì)注意事項(xiàng)的管理和優(yōu)化。之所以選擇這些解決方案,是因?yàn)樗鼈兊墓δ芙M合、低物料清單 (BOM) 成本和緊湊的占地面積使 OEM 能夠快速開發(fā)和生產(chǎn)智能連接設(shè)備。

權(quán)衡和解決方案

增加 SoC 上的系統(tǒng)級電源集成會(huì)帶來多項(xiàng)成本:

設(shè)計(jì)靈活性降低

次優(yōu)系統(tǒng)效率

更高的開發(fā)和 BOM 成本

更長的上市時(shí)間

這些權(quán)衡為構(gòu)建現(xiàn)代處理器及其電源子系統(tǒng)的系統(tǒng)級創(chuàng)新創(chuàng)造了機(jī)會(huì)。

提高設(shè)計(jì)靈活性的方法

NXP i.MX 8M/8Mini/Nano 沒有集成 DC/DC 轉(zhuǎn)換器或低壓差穩(wěn)壓器 (LDO)。類似的 SoC 也不集成 DC/DC 轉(zhuǎn)換器,但許多使用片上 LDO 將外部電源軌轉(zhuǎn)換為處理器內(nèi)核的較低電壓——對內(nèi)核應(yīng)用動(dòng)態(tài)電壓和頻率調(diào)節(jié) (DVFS)。通過將 DC/DC 和 LDO 置于片外,SoC 設(shè)計(jì)人員充分利用了昂貴的 14 納米硅片空間,這些硅片空間針對處理器內(nèi)核、緩存和音頻/視頻硬件加速器等數(shù)字功能進(jìn)行了優(yōu)化。不受片上電源管理要求的束縛,他們可以自由地制定一個(gè)(外部)電源架構(gòu),以促進(jìn)而不是限制處理器的開發(fā)。i.MX 8M 所需的相當(dāng)多的電源軌(8 個(gè) buck 和 7 個(gè) LDO)表明了這種自由度。同時(shí),ROHM PMIC 設(shè)計(jì)人員在 ROHM 的 130nm 雙極-CMOS-DMOS (BCD) 工藝中實(shí)現(xiàn)了他們的電源電路,該工藝針對電源管理功能進(jìn)行了優(yōu)化。每個(gè)團(tuán)隊(duì)都可以自由地使用最合適的工藝和 IP 來完成手頭的任務(wù)。

提高系統(tǒng)效率的方法

在 130nm BCD 工藝中實(shí)現(xiàn)電源電路允許BD71847AMWV / BD71850MWV的bucks 在 0.7V-3.3V 輸出電壓下實(shí)現(xiàn)高達(dá) 95% 的效率。在系統(tǒng)層面,當(dāng)使用外部DC/DC直接將DVFS應(yīng)用到處理器內(nèi)核時(shí),效率進(jìn)一步提升。畢竟,使用帶有片上 LDO 的外部 DC/DC 進(jìn)行 DVFS 相當(dāng)于 2 級轉(zhuǎn)換,會(huì)在第 2 級產(chǎn)生額外損耗。

一個(gè)經(jīng)常被忽視的特性是輸出電壓的精度 (+/-1.5%)。隨著輸出電壓調(diào)整步長(10mV 步長)的更高分辨率,電源管理器軟件可以精確地將電源軌的輸出電壓設(shè)置在最低水平,以最大限度地降低功耗,同時(shí)仍允許由該電源軌供電的子系統(tǒng)以所需的頻率。

降低開發(fā)和 BOM 成本的方法

隨著增加額外功能和/或減小產(chǎn)品尺寸和重量的持續(xù)市場壓力,工程師們不斷嘗試尋找將更多功能集成到 IC 中并提高可靠性的方法。然而,更高的集成度也可能帶來更高的開發(fā)和模具成本。將 SoC 開發(fā)與電源管理的開發(fā)分離開來,可以讓每個(gè)開發(fā)都以自己的最佳速度進(jìn)行。流程中的每一步——從設(shè)計(jì)、驗(yàn)證、IC 布局到 IC 制造——都變得更簡單、更快速,并大大提高了一次成功的硅的機(jī)會(huì)。較低的(總)芯片成本來自在更便宜的 (BCD) 工藝上實(shí)現(xiàn)功率函數(shù)。

縮短上市時(shí)間的方法

與許多技術(shù)企業(yè)一樣,上市時(shí)間至關(guān)重要。對于應(yīng)用處理器等高度復(fù)雜的組件,將基本不兼容的技術(shù)(如數(shù)字處理元件(CPU、硬件加速器)和電源管理)的開發(fā)分開可以降低開發(fā)工作量和風(fēng)險(xiǎn),從而加快上市時(shí)間。

結(jié)論

為 SoC 設(shè)計(jì)可編程 PMIC 的考慮因素提供了用戶體驗(yàn)和產(chǎn)品開發(fā)之間的權(quán)衡。NXP 的 8M/8MM/Nano 和 ROHM Semiconductor 的 847/850 是高度工程化的產(chǎn)品,可在產(chǎn)品生命周期的兩端取得成功。從流媒體盒和加密狗到 AV 接收器和無線條形音箱再到工業(yè) HMI、SBC、IPC 和平板計(jì)算機(jī)等應(yīng)用都使用這些組件來實(shí)現(xiàn)其強(qiáng)大的性能。這些半導(dǎo)體優(yōu)化了用戶關(guān)鍵特性(性能和價(jià)格)以及對制造商友好的資產(chǎn),例如設(shè)計(jì)靈活性和上市時(shí)間。它們是可上市的產(chǎn)品,展示了非集成組件的靈活性與高度集成的 PMIC-SoC 之間的關(guān)鍵平衡。

審核編輯:湯梓紅

-

電源

+關(guān)注

關(guān)注

184文章

17841瀏覽量

251816 -

soc

+關(guān)注

關(guān)注

38文章

4204瀏覽量

219106 -

PMIC

+關(guān)注

關(guān)注

15文章

342瀏覽量

109595

發(fā)布評論請先 登錄

相關(guān)推薦

羅姆PMIC被Telechips新一代座艙SoC參考設(shè)計(jì)采用

羅姆SOC用PMIC被Telechips新一代座艙電源參考設(shè)計(jì)采用

芯片設(shè)計(jì)進(jìn)階之SOC電源管理系統(tǒng)介紹

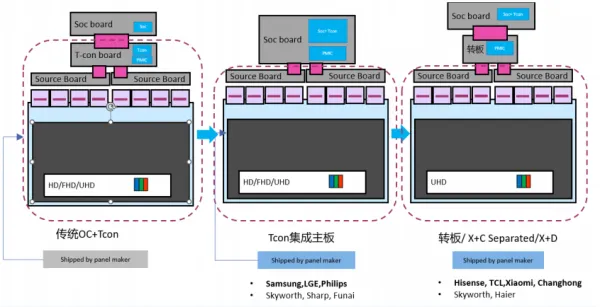

PMIC電源管理芯片-TCON顯示面板電源解決方案

NORDIC nPM1100 是一款集成式電源管理

TPS6521815工業(yè)應(yīng)用電源管理集成電路(PMIC)

TPS6521905電源管理IC(PMIC)數(shù)據(jù)表

電源管理芯片怎么測好壞

電源管理 IC (PMIC) TPS65070x 數(shù)據(jù)表

用于SoC和多軌子系統(tǒng)的TPS650250電源管理 IC (PMIC)數(shù)據(jù)表

電源管理IC (PMIC) TPS65070x數(shù)據(jù)表

TPS6572x 電源管理 IC (PMIC)數(shù)據(jù)表

適用于汽車安全相關(guān)應(yīng)用的電源管理 IC (PMIC)TPS6593-Q1數(shù)據(jù)表

博世PMIC CS600電源管理芯片技術(shù)分析

使用PMIC管理SoC的電源

使用PMIC管理SoC的電源

評論