隨著對全球連通性需求的增加,許多衛(wèi)星通信(衛(wèi)星通信)系統(tǒng)正在朝著更高的數(shù)據(jù)速率邁進(jìn),并在Ka波段頻譜中增加存在。由于高性能信號鏈現(xiàn)在能夠支持?jǐn)?shù)GHz的瞬時(shí)帶寬,并且系統(tǒng)中可能有數(shù)百個(gè)收發(fā)器,因此實(shí)現(xiàn)極高吞吐量數(shù)據(jù)速率的潛力現(xiàn)已成為現(xiàn)實(shí)。

此外,許多系統(tǒng)的趨勢是從靜態(tài)機(jī)械轉(zhuǎn)向拋物面天線轉(zhuǎn)向有源相控陣天線。這是由增強(qiáng)的技術(shù)和更高的集成度驅(qū)動的,可用于將元件間距降低到Ka波段所需的間距。相控陣技術(shù)還可以通過在干擾信號方向的天線方向上產(chǎn)生零點(diǎn)來改善干擾抑制。

以下概述描述了可用收發(fā)器架構(gòu)中存在的一些權(quán)衡,以及哪些類型的架構(gòu)可能適用于不同類型的系統(tǒng)。本分析包括衛(wèi)星系統(tǒng)的一些關(guān)鍵規(guī)格的細(xì)分,以及這些系統(tǒng)級規(guī)格如何轉(zhuǎn)化為收發(fā)器信號鏈級組件。

從系統(tǒng)級分析中向動規(guī)格

衛(wèi)星通信系統(tǒng)在高層次上關(guān)注的是保持一定的載噪比(CNR),這是鏈路預(yù)算計(jì)算的結(jié)果。保持此 CNR 可確保一定的誤碼率 (BER)。所需的 CNR 取決于許多因素,例如糾錯(cuò)、信息編碼、帶寬和調(diào)制類型。一旦建立了所需的CNR,單個(gè)接收器和發(fā)射器的規(guī)格就可以從高級系統(tǒng)要求中向動。通常,它們首先以接收器所需的系統(tǒng)噪聲溫度增益(G/T)品質(zhì)因數(shù)和發(fā)射器的有效各向同性輻射功率(EIRP)的形式向動。

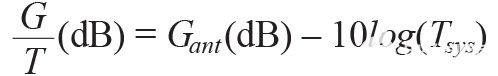

對于接收器,從G/T轉(zhuǎn)換為較低電平的接收器信號鏈規(guī)格,系統(tǒng)設(shè)計(jì)人員需要知道天線增益和系統(tǒng)噪聲溫度,這是天線指向的位置和接收器噪聲溫度的函數(shù),如公式1所示。從這里,接收器溫度可以在公式2中找到。

接收器信號鏈所需的噪聲系數(shù)可以從公式3中找到:

一旦知道接收器噪聲系數(shù),就可以計(jì)算級聯(lián)分析,以確定信號鏈?zhǔn)欠駶M足這些要求的規(guī)格,以及是否可以根據(jù)需要進(jìn)行調(diào)整。

對于發(fā)射器,所需的EIRP首先根據(jù)接收器的距離(地對衛(wèi)星或衛(wèi)星對地)以及接收器的靈敏度來確定。一旦知道了EIRP要求,就會在發(fā)射信號鏈的輸出功率和天線的增益之間進(jìn)行權(quán)衡。使用更高增益的天線,發(fā)射器的功耗和尺寸可以下降,但代價(jià)是天線更大。EIRP 由公式 4 給出。

通過在信號鏈中仔細(xì)選擇元件,可以保持所需的輸出功率,而不會導(dǎo)致其他重要參數(shù)的下降,例如輸出噪聲頻譜密度和帶外RF能量,這些參數(shù)可能會對其他系統(tǒng)造成干擾。

發(fā)射器和接收器的其他關(guān)鍵規(guī)格包括:

瞬時(shí)帶寬:信號鏈在任何時(shí)間點(diǎn)可以數(shù)字化多少頻譜

功率處理:信號鏈在不降低性能的情況下可以處理多大的信號

通道之間的相位相干性:對于新興波束成形系統(tǒng),確保通道之間的相位可預(yù)測,從而簡化波束成形信號處理和校準(zhǔn)

雜散性能:確保接收器和發(fā)射器不會在不需要的頻率下產(chǎn)生可能影響系統(tǒng)或其他系統(tǒng)性能的射頻能量

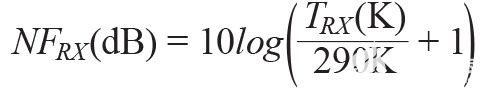

圖1.架構(gòu)比較,(a) 集成 TRx 的高中頻,(b) 采用 GSPS ADC 的雙變頻超外差,(c) 采用 GSPS ADC 的單變頻超外差,(d) 帶 I/Q 混頻器的直接變頻。

在信號鏈設(shè)計(jì)過程中牢記這些和其他規(guī)格對于保證高性能系統(tǒng)滿足任何給定應(yīng)用至關(guān)重要,無論是寬帶多載波聚合集線器還是單個(gè)窄帶手持式衛(wèi)星通信終端。

一般架構(gòu)比較

一旦確定了高電平規(guī)格,就可以決定信號鏈架構(gòu)。前面列出的可能對架構(gòu)產(chǎn)生重大影響的關(guān)鍵規(guī)格之一是瞬時(shí)帶寬。這會影響接收器的模數(shù)轉(zhuǎn)換器(ADC)和發(fā)射器的數(shù)模轉(zhuǎn)換器(DAC)。為了達(dá)到更高的瞬時(shí)帶寬,必須以更高的速率對數(shù)字化儀進(jìn)行采樣,這通常會推高整個(gè)信號鏈的功耗,但如果根據(jù)W/GHz進(jìn)行判斷,則會降低功耗。

對于帶寬小于100 MHz的系統(tǒng),類似于圖1a所示的基本架構(gòu)在許多情況下是最佳的。該架構(gòu)使用標(biāo)準(zhǔn)下變頻級與集成直接變頻收發(fā)器芯片的混合。集成收發(fā)器提供高集成度,大幅減小尺寸和功耗。

為了達(dá)到高達(dá)1.5 GHz的帶寬,可以利用經(jīng)典的雙變頻超外差架構(gòu),結(jié)合最新的ADC技術(shù);如圖 1b 所示。這是一種成熟的高性能架構(gòu),其轉(zhuǎn)換級用于濾除不需要的雜散信號。根據(jù)接收到的頻段,有一個(gè)下變頻級到中頻(IF),然后還有一個(gè)額外的下變頻級,使最終IF達(dá)到ADC可以數(shù)字化的低頻。最終IF越低,ADC性能就越高,但代價(jià)是濾波要求增加。通常,由于元件數(shù)量增加,這種架構(gòu)是所提出的四個(gè)選項(xiàng)中最大和最高的功率。

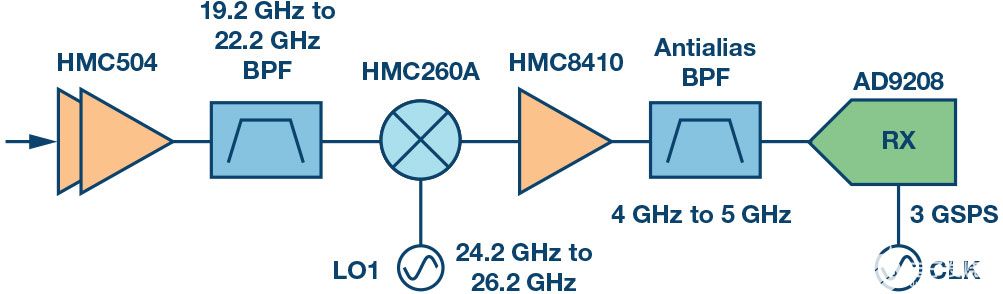

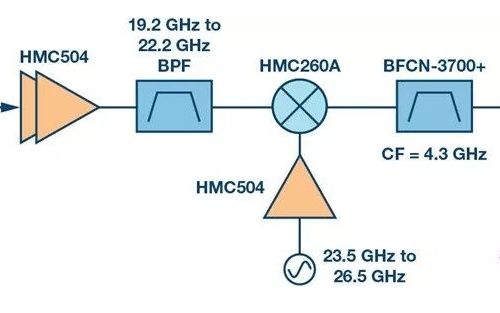

圖1c顯示了類似的選項(xiàng),這是一個(gè)由GSPS ADC采樣的更高IF的單變頻級。這種架構(gòu)利用了ADC能夠數(shù)字化的不斷增加的RF帶寬,而性能下降很小。市場上最新的GSPS ADC允許對高達(dá)9 GHz的RF頻率進(jìn)行直接采樣。在此選項(xiàng)中,IF的中心范圍為4 GHz至5 GHz,以便在信號鏈濾波要求和ADC要求之間取得最佳平衡。

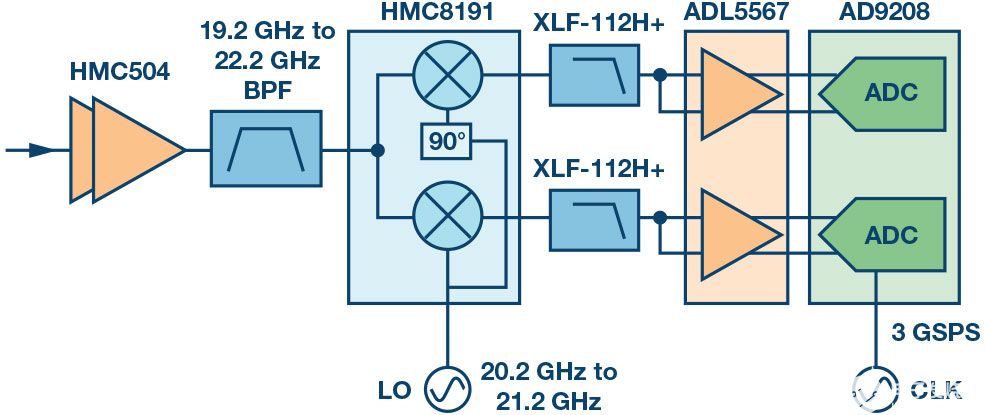

最后一個(gè)選項(xiàng)如圖 1d 所示。這種架構(gòu)提供了更大的瞬時(shí)帶寬增加,但代價(jià)是復(fù)雜性和潛在的性能下降。這是一種使用無源I/Q混頻器的直接變頻架構(gòu),可以在基帶上輸出兩個(gè)彼此偏移90°的中頻。然后,使用雙通道GSPS ADC對每個(gè)I和Q支路進(jìn)行數(shù)字化。在這種情況下,可以獲得高達(dá)3 GHz的瞬時(shí)帶寬。此選項(xiàng)的主要挑戰(zhàn)是保持I和Q路徑之間的正交平衡,因?yàn)檎`差會通過混頻器、低通濾波器和ADC驅(qū)動器傳播。根據(jù) CNR 的要求,這可能是一個(gè)可以接受的權(quán)衡。

這里給出了一個(gè)總體概述,從高層次上描述了這些接收器架構(gòu)的操作。顯示的列表無論如何都不是包羅萬象的,使用每個(gè)選項(xiàng)元素的混合體也是可能的。雖然比較中未涵蓋發(fā)射信號鏈,但圖1中的每個(gè)選項(xiàng)都有一個(gè)相應(yīng)的發(fā)射信號鏈,并且權(quán)衡相似。

Ka波段衛(wèi)星通信接收器示例

通過前面對每種架構(gòu)的優(yōu)缺點(diǎn)的討論,我們現(xiàn)在可以將這些理解應(yīng)用于實(shí)際的信號鏈?zhǔn)纠TS多衛(wèi)星通信系統(tǒng)現(xiàn)在都在Ka波段運(yùn)行,以減小天線尺寸并提高數(shù)據(jù)速率。這在高通量衛(wèi)星系統(tǒng)中尤其重要。以下是使用不同體系結(jié)構(gòu)的示例以及更詳細(xì)的比較。

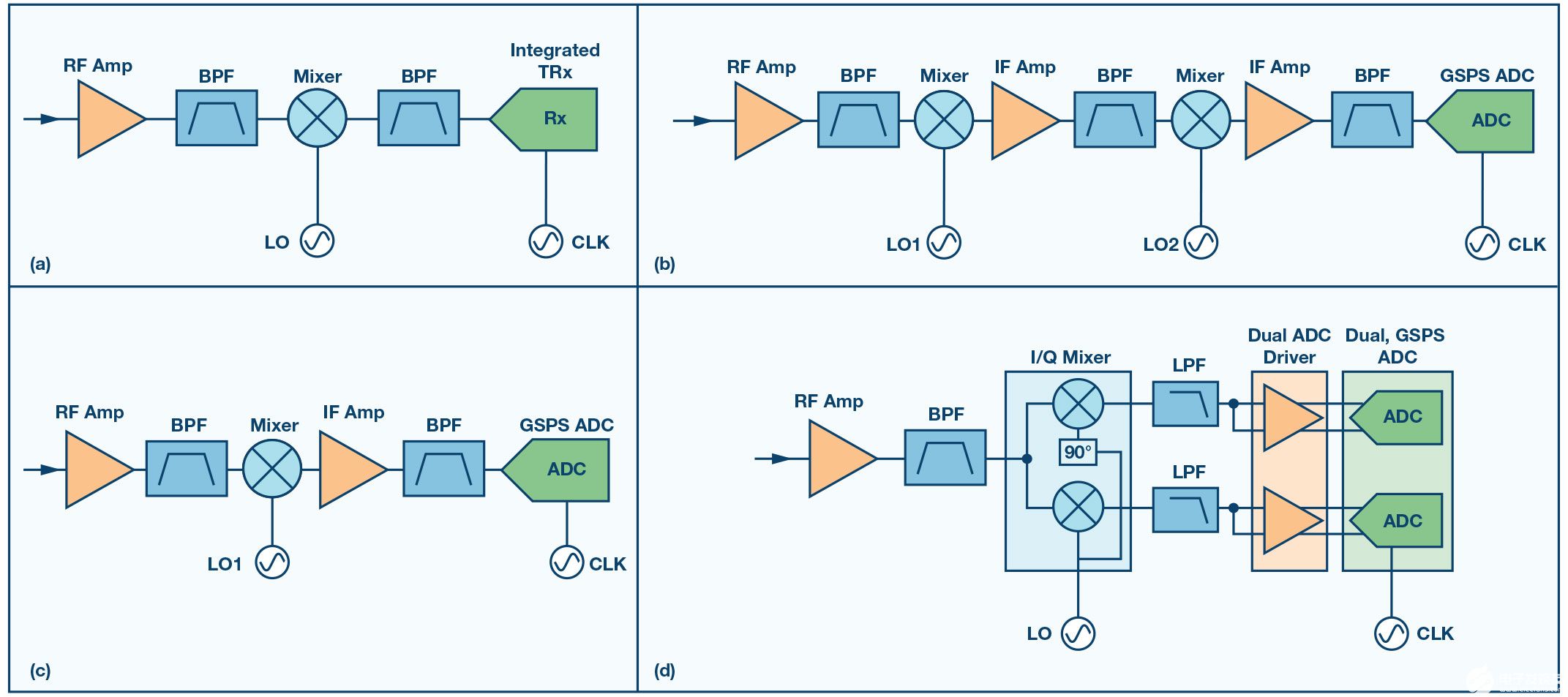

對于需要低于100 MHz瞬時(shí)帶寬的系統(tǒng),例如使用甚小孔徑終端(VSAT),可以使用集成收發(fā)器芯片(AD9371)的高中頻架構(gòu),如圖2所示。這種設(shè)計(jì)可以實(shí)現(xiàn)低噪聲系數(shù),并且由于它具有如此高的集成度,因此它提供了最小的設(shè)計(jì)尺寸。其性能摘要見表1。

圖2.集成 TRx 的高中頻,高達(dá) 100 MHz 帶寬

如果某些系統(tǒng)充當(dāng)衛(wèi)星通信系統(tǒng)中多個(gè)用戶的集線器,則它們可能一次處理許多載波信號。在這種情況下,每個(gè)接收器的帶寬或帶寬/功率成為重要因素。圖3所示信號鏈?zhǔn)褂酶咚貯DC,即最近發(fā)布的高采樣速率ADCAD9208,可數(shù)字化高達(dá)1.5 GHz的瞬時(shí)帶寬。在本例中,IF置于4.5 GHz,以實(shí)現(xiàn)1 GHz的瞬時(shí)帶寬。此處可實(shí)現(xiàn)的帶寬取決于ADC之前抗混疊濾波器的濾波要求,但通常限制為奈奎斯特區(qū)的~75%(采樣速率的一半)。

圖3.采用GSPS ADC的單次下變頻至高中頻

在需要最高瞬時(shí)帶寬且可能以CNR形式放棄性能的系統(tǒng)中,可能需要使用圖4所示的信號鏈。該信號鏈采用I/Q混頻器HMC8191,其鏡像抑制性能為~25 dBc。在這種情況下,鏡像抑制受到I和Q輸出通道之間的幅度和相位平衡的限制。這是該信號鏈在沒有更先進(jìn)的正交糾錯(cuò)技術(shù)(QEC)的情況下的限制因素。信號鏈性能匯總?cè)绫?所示。值得注意的是,NF 和 IP3 性能與其他選項(xiàng)相似,但功率/GHz 指標(biāo)是三者中最低的,并且大小對于任何時(shí)刻可以使用的帶寬量同樣是最佳的。

圖4.通過I/Q混頻器和GSPS ADC直接轉(zhuǎn)換。

下表顯示了此處給出的三個(gè)接收選項(xiàng),但應(yīng)該注意的是,此列表并不意味著所有可能選項(xiàng)的全面細(xì)分。給出此摘要概述是為了顯示各種信號鏈選項(xiàng)之間的差異。在任何給定系統(tǒng)中,最終的最佳信號鏈可以是所示的三種方法之一,也可以是其中任何一種的混合方法。

| 高中頻,帶國際 TRx | 采用 GSPS ADC 的高中頻 | 直接轉(zhuǎn)換 | |

| 數(shù)字化 | AD9371 | AD9208 | AD9208 (雙通道) |

| 瞬時(shí)帶寬 | 100兆赫 | 1千兆赫 | 2千兆赫 |

| 凈值 (分貝) | 2.5 | 2.3 | 2.3 |

| IIP3 (分貝) | –19 | –20 | –20 |

| 最大引腳 (dBm) | –38 | –40 | –41 |

| 其他雜散(HD2、HD3、MxN) | 65分貝 | 73分貝 | 45分貝 |

| 鏡像抑制 (dBc) | 75 | 80 | 25 |

| 過濾難度 | 低 | 中等 | 低 |

| 功率 (W) | 2.9 | 4.1 | 6.1 |

| 功率/千兆赫 (瓦/千兆赫) | 29 | 4.1 | 3.05 |

| 包裝尺寸(毫米2) | 300 | 510 | 580 |

此外,即使只顯示了接收器側(cè)的故障,發(fā)射器信號鏈也存在許多類似的權(quán)衡。通常,當(dāng)系統(tǒng)從超外差風(fēng)格架構(gòu)轉(zhuǎn)向直接轉(zhuǎn)換風(fēng)格架構(gòu)時(shí),需要在帶寬和性能之間進(jìn)行權(quán)衡。

數(shù)據(jù)接口

一旦數(shù)據(jù)被ADC或收發(fā)器數(shù)字化,就必須通過數(shù)字接口傳遞,由系統(tǒng)進(jìn)行處理。上述所有數(shù)字化儀均采用高速JESD204b標(biāo)準(zhǔn),該標(biāo)準(zhǔn)從數(shù)據(jù)轉(zhuǎn)換器獲取位并將其打包成幀,以便在少量走線上傳輸。來自芯片的數(shù)據(jù)速率將根據(jù)系統(tǒng)要求而變化,但所有上述器件都具有數(shù)字抽取和頻移功能,以適應(yīng)各種數(shù)據(jù)速率,以適應(yīng)不同的系統(tǒng)要求。該規(guī)范允許JESD204b通道上高達(dá)12.5 GSPS的速度,這在傳輸大量數(shù)據(jù)的高帶寬系統(tǒng)中得到了充分利用。有關(guān)這些接口的詳細(xì)說明,請參見AD9208和AD9371的數(shù)據(jù)手冊。此外,FPGA的選擇必須考慮到這個(gè)接口。來自賽靈思和 Altera 等供應(yīng)商的許多 FPGA 以及其他供應(yīng)商現(xiàn)在都采用該標(biāo)準(zhǔn)到其部件中,以便與這些數(shù)據(jù)轉(zhuǎn)換器輕松集成。

結(jié)論

所示分析分解了各種權(quán)衡,并給出了適用于在Ka波段運(yùn)行的衛(wèi)星通信系統(tǒng)的信號鏈的具體示例。該架構(gòu)提供了多種架構(gòu)選項(xiàng),包括利用集成收發(fā)器AD9371的單次轉(zhuǎn)換至高中頻,使用GSPS ADC代替集成收發(fā)器以增加瞬時(shí)帶寬的類似架構(gòu),以及增加帶寬但代價(jià)是降低鏡像抑制性能的直接變頻架構(gòu)。所示的信號鏈可以直接使用,但可作為設(shè)計(jì)過程的起點(diǎn)。根據(jù)系統(tǒng)級應(yīng)用的不同,會出現(xiàn)不同的要求,并且可能會有一條清晰的路徑,使一個(gè)信號鏈優(yōu)于另一個(gè)信號鏈。

審核編輯:郭婷

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3454瀏覽量

106244 -

接收器

+關(guān)注

關(guān)注

14文章

2480瀏覽量

72217 -

衛(wèi)星通信

+關(guān)注

關(guān)注

12文章

727瀏覽量

38823

發(fā)布評論請先 登錄

相關(guān)推薦

RadioVerse生態(tài)系統(tǒng)中的寬帶收發(fā)器

適用于能量采集應(yīng)用的電源管理架構(gòu)

適用于承受10kV ESD的手持式計(jì)算機(jī)的RS232收發(fā)器

RadioVerse生態(tài)系統(tǒng)中的寬帶收發(fā)器分享!

一款超低功耗集成收發(fā)器

介紹Xilinx 7系列FPGA收發(fā)器硬件設(shè)計(jì)主要注意的一些問題

從技術(shù)規(guī)格、收發(fā)器架構(gòu)、Ka頻段衛(wèi)星通信系統(tǒng)適用的信號鏈來了解Ka頻段帶寬

PCB板設(shè)計(jì)時(shí)如何進(jìn)行一些權(quán)衡讓PCB的電源分配網(wǎng)絡(luò)合理

TIDA-010132-適用于雷達(dá)和電子戰(zhàn)應(yīng)用的多通道射頻收發(fā)器 PCB layout 設(shè)計(jì)

可用收發(fā)器架構(gòu)中存在的一些權(quán)衡及適用于不同類型的系統(tǒng)

可用收發(fā)器架構(gòu)中存在的一些權(quán)衡及適用于不同類型的系統(tǒng)

評論