本章我們接著介紹信號完整性基礎第三章節串擾剩余知識。

04帶狀線和微帶線地串擾差異

(1)帶狀線信號在傳播的時候,可以認為其周圍介質是均勻的,因此沒有遠端串擾,或遠端串擾很小。(遠端串擾的感性和容性大小相等,幅度相反,相互抵消)

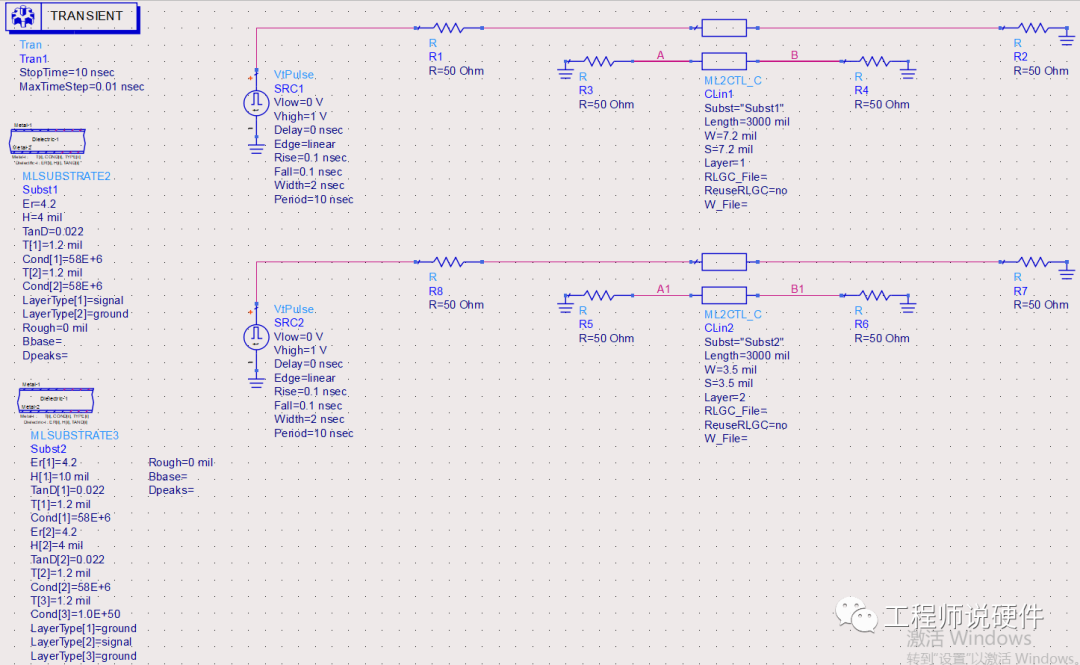

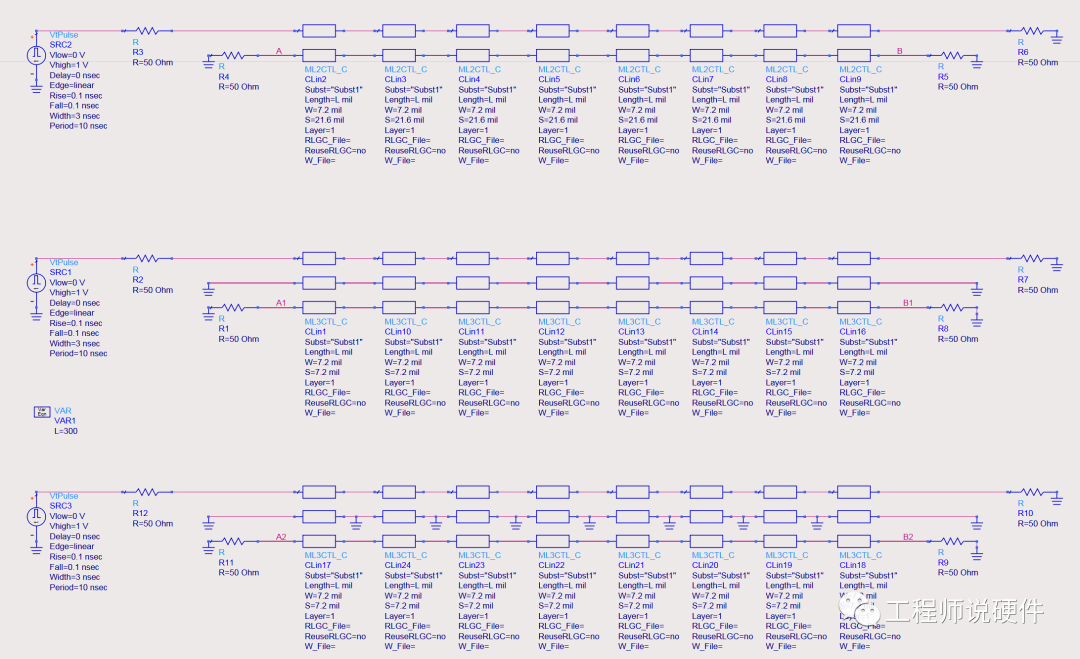

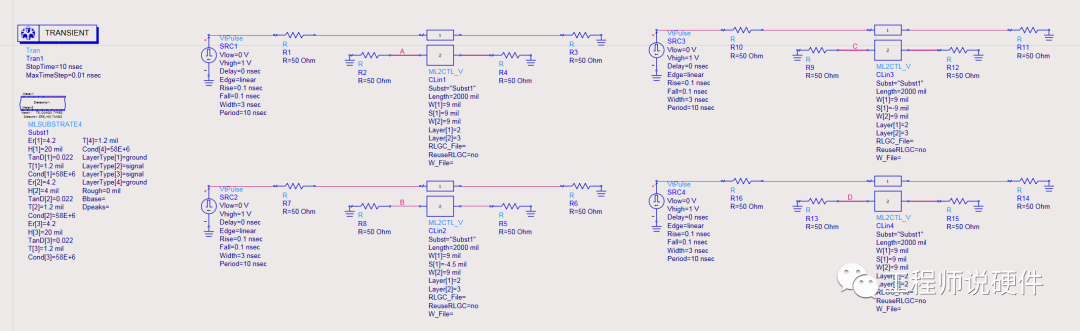

如下仿真實驗所示。

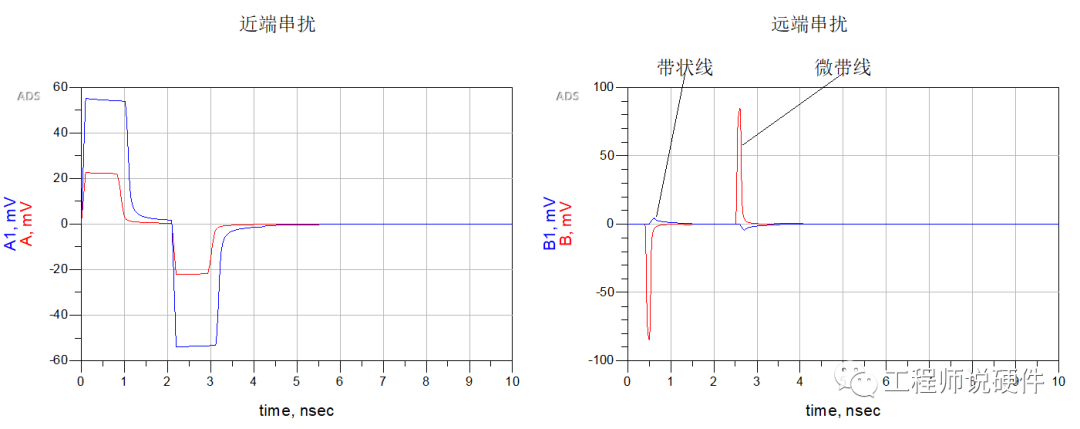

圖1、2 ADS仿真:帶狀線和微帶線遠端串擾對比(2)在較短的走線情形下,微帶線在走線間距較小的時候相對帶狀線的近端串擾更小,隨著間距的增加,帶狀線的近端串擾衰減幅度更大。

因此,實際項目中,還是建議信號在內層以帶狀線地方式進行走線。

圖3、4 ADS仿真:帶狀線和微帶線近端串擾對比

05包地處理

(1)PCB中常對關鍵信號添加保護地線,目的是引入低阻抗邊界,將信號上發射出來的干擾引入到地回路。

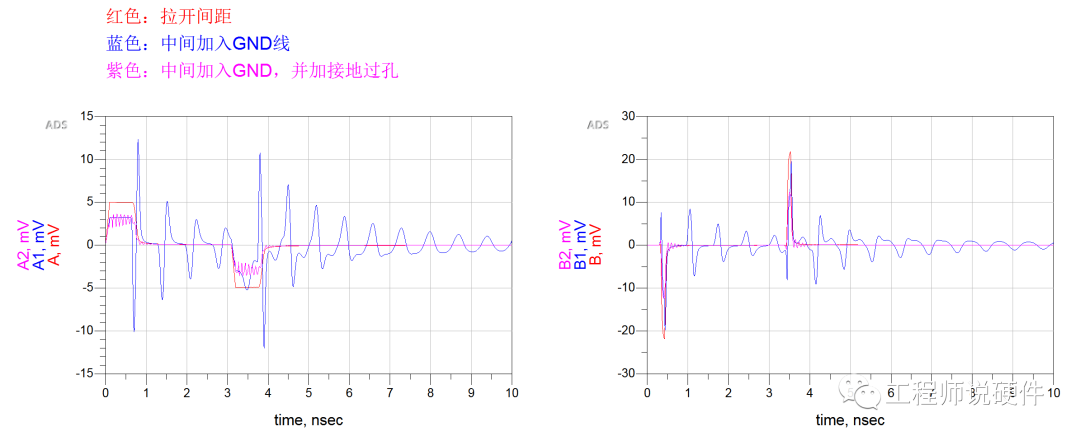

(2)合理的包地有助于優化信號,但如果包地不合理,反而會對信號造成干擾。

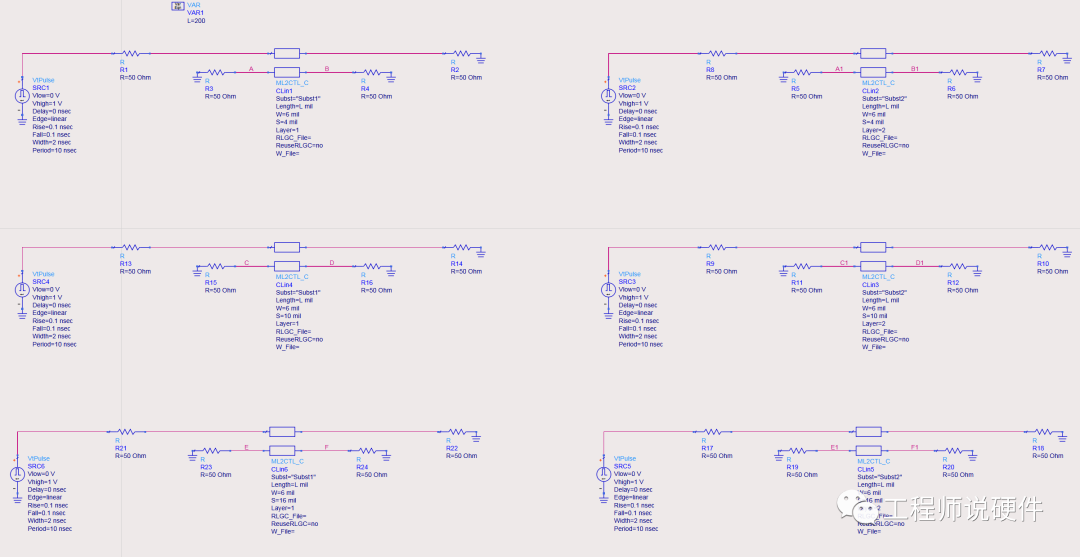

圖5、6 ADS仿真:不同包地對串擾地影響

從上述仿真實驗可以看出,加入不合理的地線之后,近端串擾反而增大,并出現了類似遠端串擾的脈沖。這是由于串擾在地線上來回反射造成的。

(3)要使保護地線發揮作用,應在保護地線上添加過孔,通常建議過孔密度大于1/20波長,不能小于1/10波長。

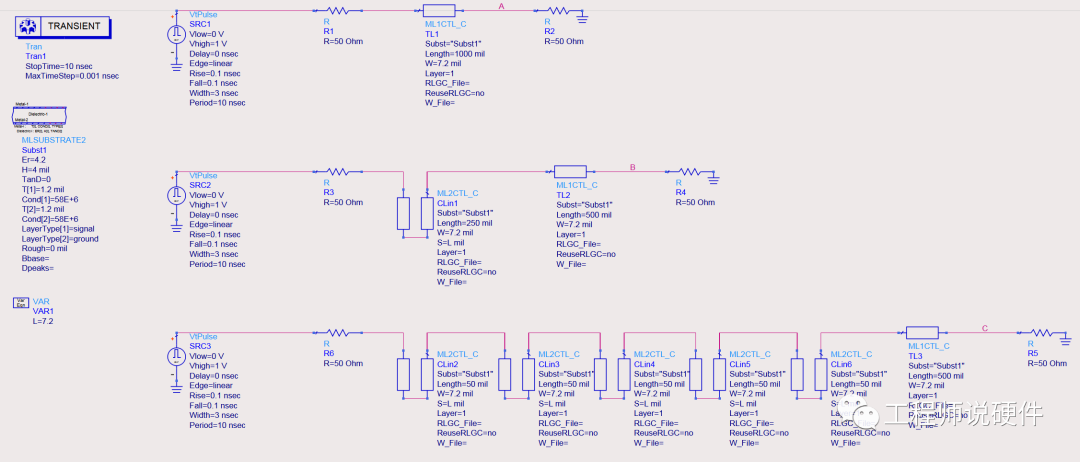

06等長方式

(1)為了保證信號傳輸延時一致,常通過蛇形走線來繞等長。

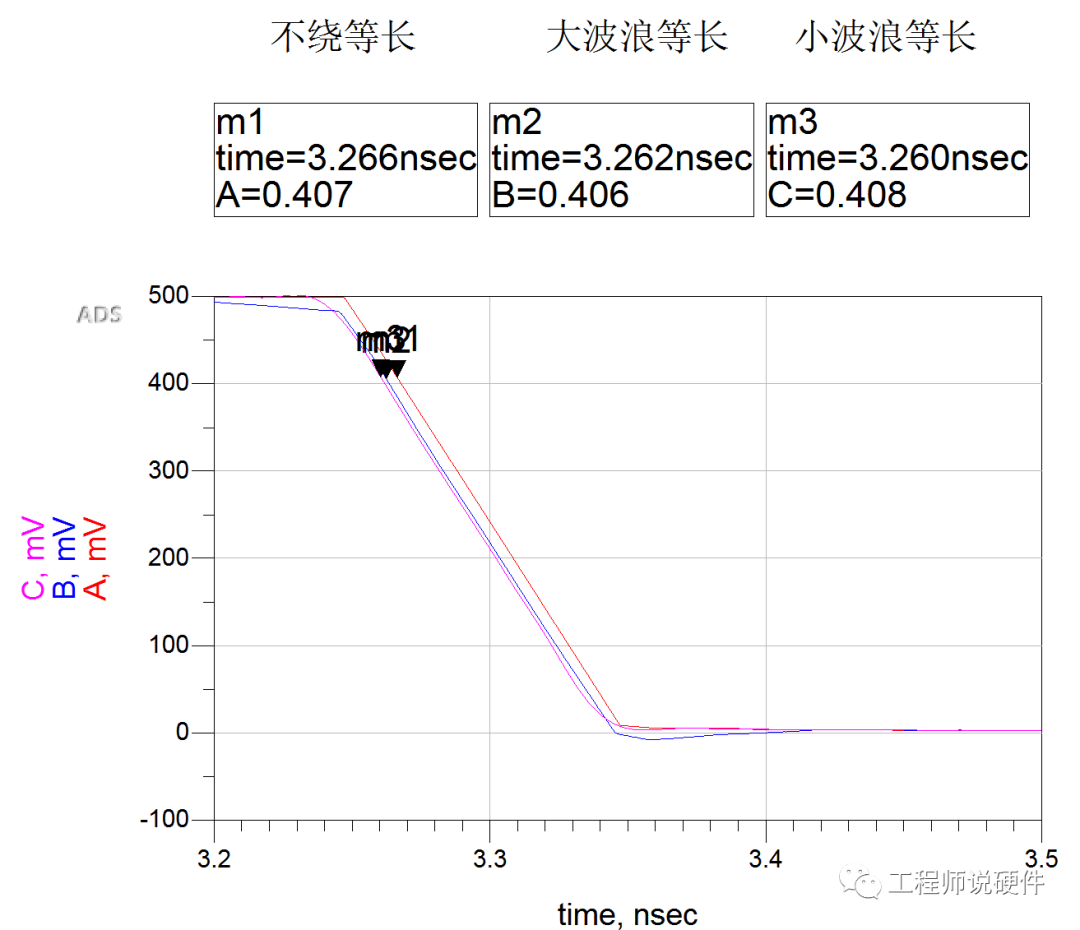

(2)等長不一定等延時,繞等長之后會使信號提前到達。不同繞等長的方式,信號提前到達的時間不一致。(5G以內信號基本忽略影響)

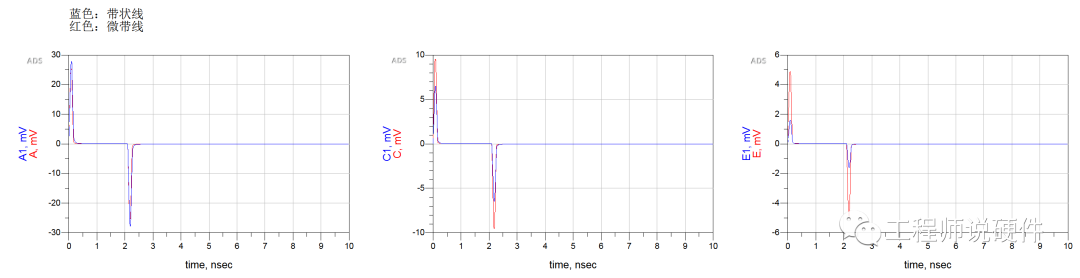

圖7、8 ADS仿真:等長方式對信號時延地影響

(3)通過加大走線之間的間隔可以將走線延時差異縮小

(4)造成信號提前到達的原因是因為自耦合。當信號在蛇形線傳輸的時候,在鄰近線產生近端串擾,和信號疊加導致信號提前到達。

(5)為了使信號盡可能同時到達,可以通過拉開蛇形走線的Gap間距,建議>=3X。同時使用小波浪繞線,避免平行走線過長。

(小波浪雖然比大波浪更提前,但是小波浪波形質量更好)(小波浪造成的近端串擾寬度較小,淹沒在信號邊沿中,對信號整體質量不影響,大波浪造成的近端串擾寬度較大,會和信號疊加,影響信號質量)

使用小波浪繞線,波浪不能太小,太小由于趨膚效應,信號會直接穿過。(波浪高度不能小于信號走線寬度的2倍)

07層間耦合

(1)如果相鄰層走線重疊或接近,同時相鄰層PP片或芯板厚度太低,串擾會在相鄰層之間產生。

(2)相鄰層耦合對信號的影響遠大于同層走線串擾帶來的影響。為了控制5%的串擾系數,應使相鄰層信號間距大于一倍線寬

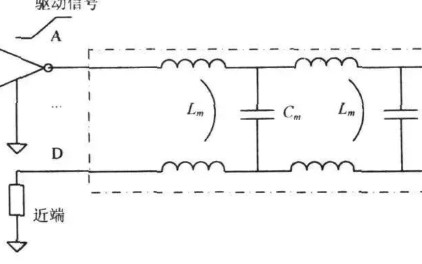

圖9、10 近端和遠端串擾示意圖

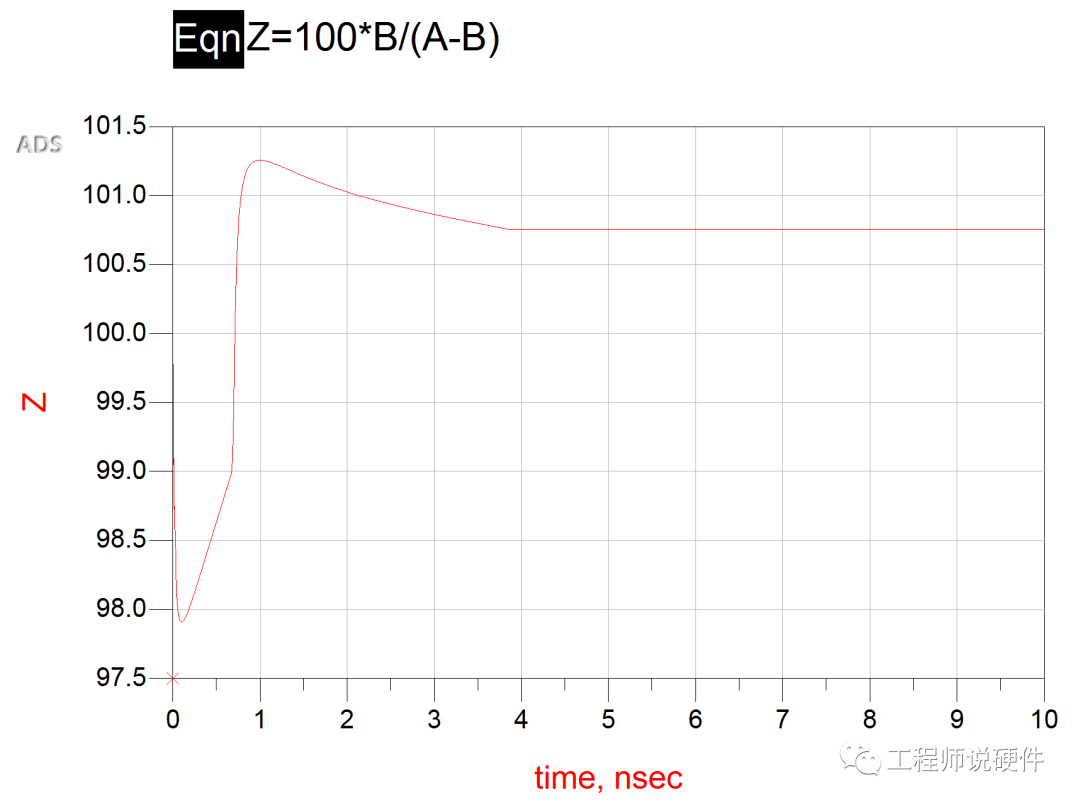

(3)當差分走線受空間限制,同層不好出線時,可以考慮利用層間耦合,通過相鄰層兩線重疊的方式達到差分效果。

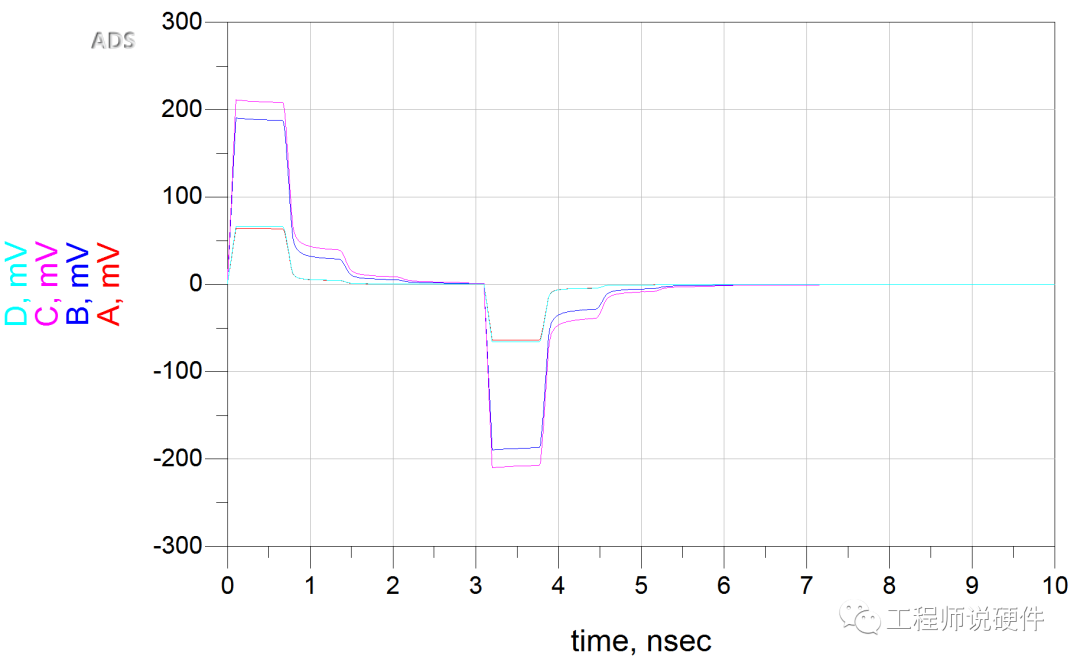

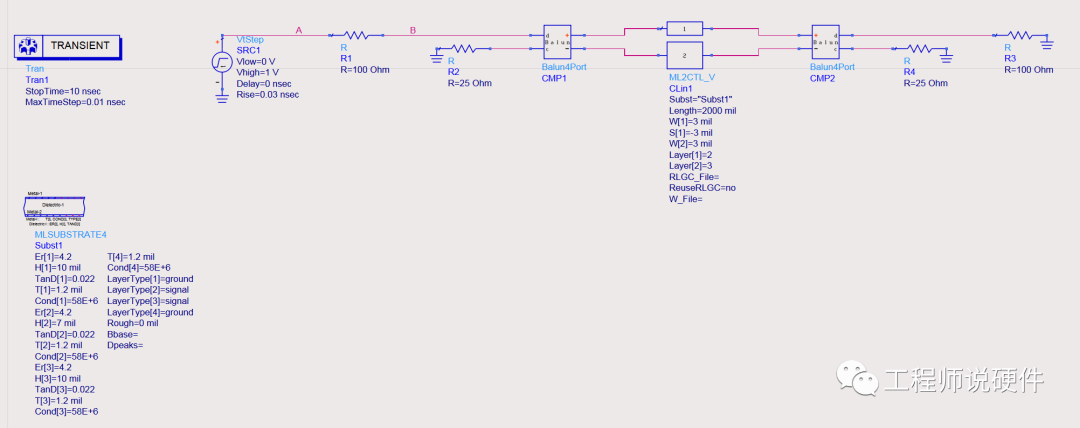

圖11、12 ADS仿真:層間耦合差分信號

審核編輯:湯梓紅

-

pcb

+關注

關注

4326文章

23160瀏覽量

399942 -

信號完整性

+關注

關注

68文章

1417瀏覽量

95633 -

串擾

+關注

關注

4文章

189瀏覽量

26992 -

微帶線

+關注

關注

2文章

82瀏覽量

16428 -

帶狀線

+關注

關注

0文章

15瀏覽量

8335

原文標題:信號完整性基礎--串擾(二)

文章出處:【微信號:工程師說硬件,微信公眾號:工程師說硬件】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

常見信號完整性的問題之PCB設計串擾的原因與Altium Designer中的串擾消除技術

信號完整性基礎--串擾(二)

信號完整性基礎--串擾(二)

評論