周末正好擼到了芯片的DFT設計,特此分享兩個案例。

DFT經典案例1:

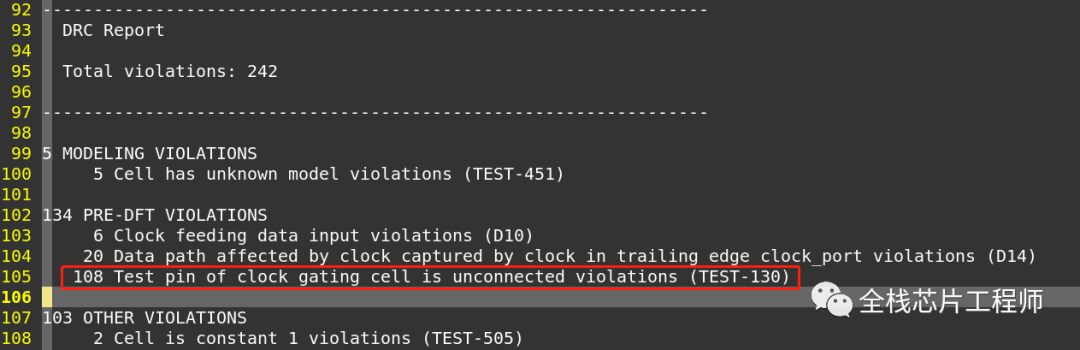

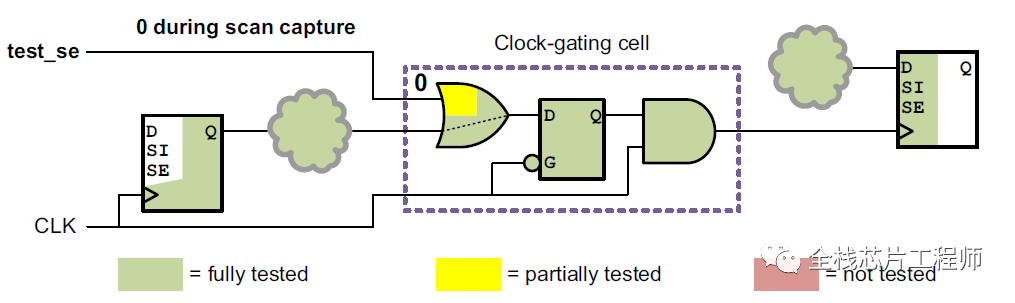

clock gating cell報警如下:Test pin unconnected。當工具運行pre-DFT DRC檢查時,每個clock gating cell都會有TEST-130 message報出來,不管clock gating cell是discrete-logic還是integrated ICG。

如下圖:108 Test pin of clock gating cell is unconnected violations (TEST-130)

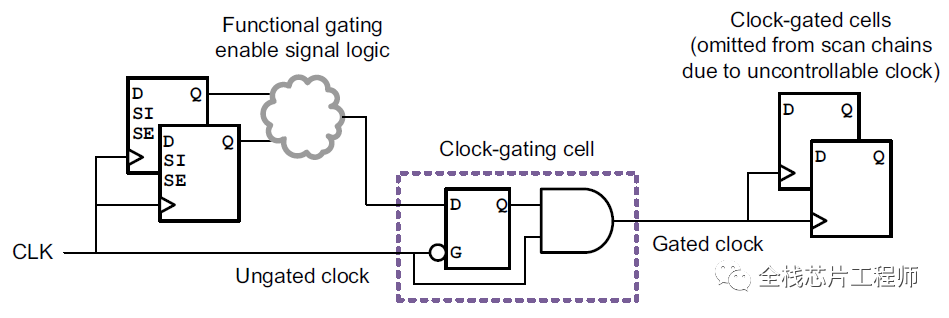

我們知道門控時鐘會造成DFT scan時鐘不可控,因此需要特殊處理,比如加入control point。

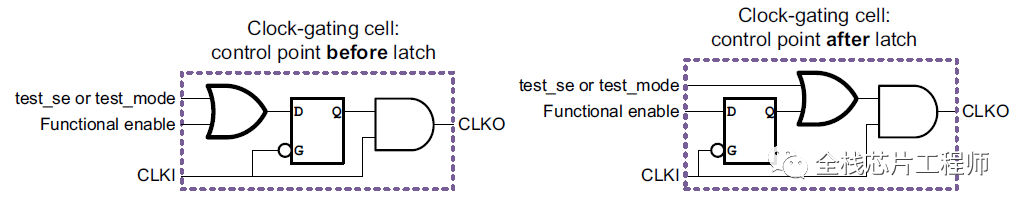

control point可以放在ICG latch的前面或者后面,為了避免毛刺,推薦control point放在latch前面,業界ICG都是將control point放在latch前面的。

另一個經典問題就是,用test_mode還是scan_enable來驅動Clock-gating cell的TE端口?

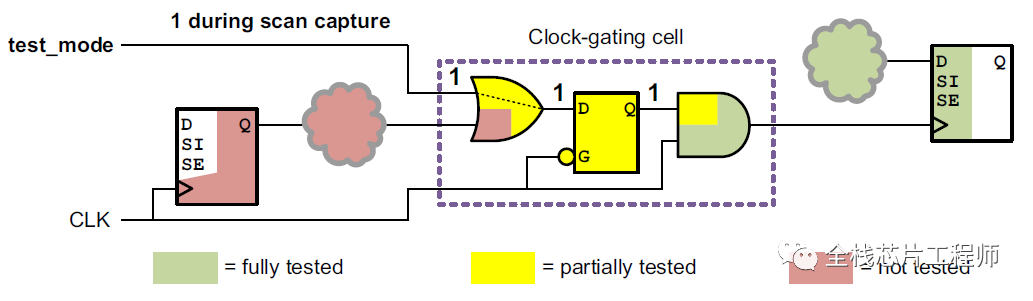

scan_enable只是在scan shift運行時候才有效,capture時候scan_enable是無效的。test_mode是整個測試期間都有效,即scan shift和scan capture階段test_mode都有效。

test_mode接TE的缺點是capture mode下無法測試到functional clock-gatinglogic,就是functional clock-gating logic完全被bypass了。此外test-mode 僅能被測試stuck-at-0 faults (假設test-mode 信號為高有效情況下)。

那么用test_mode還是scan_enable來驅動Clock-gating cell的TE端口?自然是scan_enable,可以提高測試覆蓋率。

因此我們可以在dft的約束中加入如下腳本:

set_clock_gating_style -control_point before -control_signal scan_enable

對于CRG模塊RTL里面手動例化的ICG而言,TE接test_mode的話,那么ICG在test_mode下一直是transparent,后面的flip-flop在shift in和capture時都有clock。TE接scan_enable,那么在capture 時一定要保證ICG后面的flip-flop都有clock,此時用scan_enable可以提高一些DFT的覆蓋率。

DFT經典案例2:

rst_n_pad作為芯片function的復位信號,也作為DFT Scan的復位信號,命令如下:

set_dft_signal -view existing_dft -type Reset -port rst_n_pad -active 0

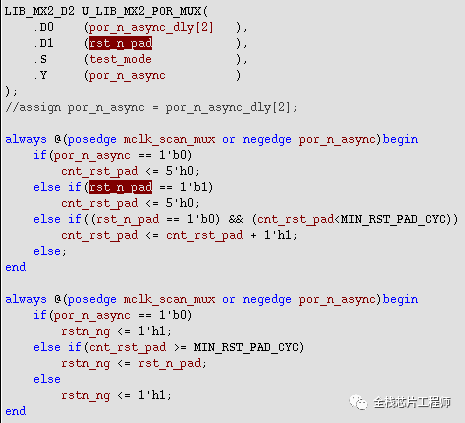

在設計的func中,有對rst_n_pad復位信號做毛刺過濾功能,代碼如下圖:

這段代碼在DFT設計中,會有什么問題呢?很精彩!

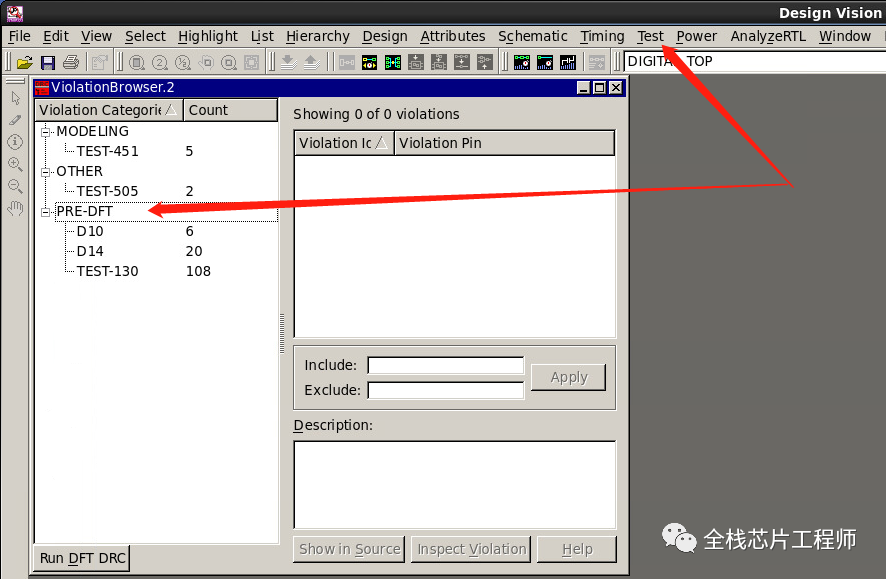

打開DC GUI界面進行DFT_DRC定位:

dc_shell> gui_start

點擊Test -> Run DFT DRC

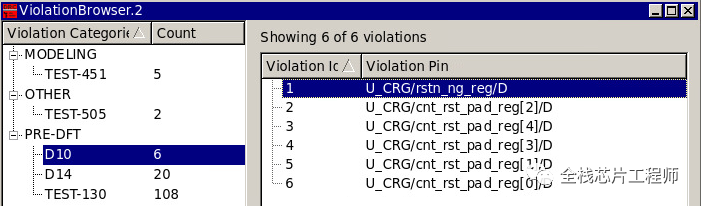

工具報錯說D10有6個,挑選一個進行解釋:

rst_n_pad ( Warning: Clock rst_n_pad connects to data input (D) of DFF U_CRG/cnt_rst_pad_reg[0]. (D10-6) )

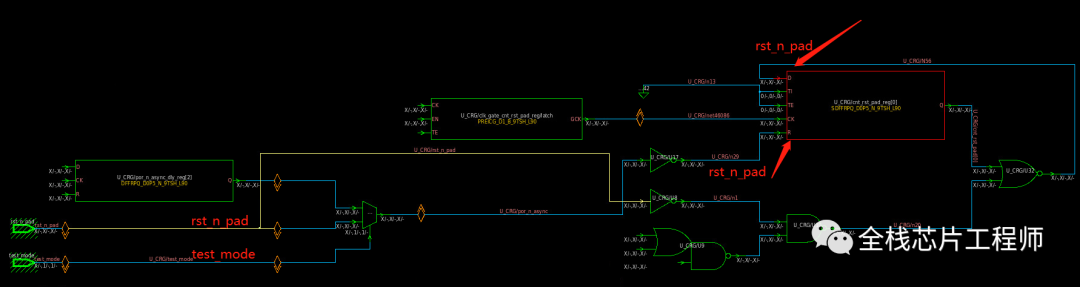

從如下電路看出,rst_n_pad作為DFT的復位信號,在test_mode=1有效時候對cnt_rst_pad_reg[0]進行復位,但是rst_n_pad也會傳遞到cnt_rst_pad_reg[0]的D端,從而造成什么問題呢?先思考下。

審核編輯 :李倩

-

芯片

+關注

關注

456文章

51192瀏覽量

427317 -

時鐘

+關注

關注

11文章

1747瀏覽量

131803 -

DFT

+關注

關注

2文章

231瀏覽量

22841 -

復位信號

+關注

關注

0文章

54瀏覽量

6366

原文標題:DFT設計實戰案例解讀

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DFT設計實戰案例解讀

DFT設計實戰案例解讀

評論