今天的電子系統(tǒng)可能有許多不同的電源軌。在采用模擬電路以及微處理器、DSP、ASIC 和 FPGA 的系統(tǒng)中尤其如此。為實(shí)現(xiàn)可靠、可重復(fù)的操作,需要控制每個(gè)電源電壓的開關(guān)時(shí)序、上升和下降速率、應(yīng)用順序和幅度。給定的電源系統(tǒng)設(shè)計(jì)可能包括電源排序、電源跟蹤以及電源電壓/電流監(jiān)測(cè)和控制。現(xiàn)有的電源管理IC可用于執(zhí)行上電和斷電的排序、跟蹤和監(jiān)控功能。

排序和跟蹤設(shè)備可以監(jiān)視和控制多個(gè)軌道;其功能可能包括設(shè)置導(dǎo)通時(shí)間和電壓斜坡速率、欠壓和過壓故障檢測(cè)、裕量調(diào)節(jié)(在標(biāo)稱電壓值范圍內(nèi)的電源調(diào)整)和有序關(guān)斷。用于這些應(yīng)用的IC范圍從簡(jiǎn)單的純模擬器件(帶有電阻器、電容和比較器)到高度集成的狀態(tài)機(jī)和可編程器件(通過I進(jìn)行數(shù)字控制)。2C總線。在某些情況下,系統(tǒng)的穩(wěn)壓器和控制器可能包括關(guān)鍵控制功能。

采用多個(gè)開關(guān)控制器和穩(wěn)壓器的系統(tǒng)的另一個(gè)考慮因素是如何最大限度地降低它們?cè)诓煌_關(guān)頻率下工作時(shí)產(chǎn)生的系統(tǒng)噪聲。通常需要同步穩(wěn)壓器的時(shí)鐘。事實(shí)上,當(dāng)今許多高性能開關(guān)控制器和穩(wěn)壓器都可以同步到外部時(shí)鐘。

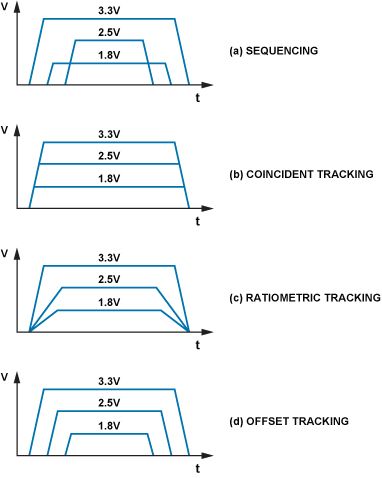

圖1.電源軌控制的類型。

電源排序和跟蹤

電源排序需要按特定順序打開或關(guān)閉電源。電源序列的控制可以簡(jiǎn)單地基于既定的時(shí)間順序,或者電源的導(dǎo)通時(shí)間可能取決于另一個(gè)電源達(dá)到編程閾值。電源跟蹤基于這樣一個(gè)事實(shí),即電源不能(通常也不應(yīng)該)提供其電壓的瞬時(shí)變化;電源系統(tǒng)設(shè)計(jì)人員可以有利地利用這一點(diǎn)來控制每個(gè)電源相對(duì)于系統(tǒng)中其他電源的壓擺率。供應(yīng)跟蹤分為三類:重合、比率和偏移。圖 1 顯示了四個(gè)圖表,分別比較了排序、重合跟蹤、比率跟蹤和偏移跟蹤。

在圖1a中,三個(gè)電源的打開和關(guān)閉順序是定時(shí)的。這里首先是3.3 V電源,后續(xù)電源的導(dǎo)通和關(guān)斷延遲時(shí)間取決于應(yīng)用的需求。這種簡(jiǎn)單的排序技術(shù)可以確保不超過有源元件的最大額定值,如果這些額定值要求按特定順序激活電源。這方面的一個(gè)例子是,在驅(qū)動(dòng)ADC的放大器上電之前,需要保證ADC的電源存在,如果不提供此電源,可能會(huì)導(dǎo)致ADC前端損壞。

在圖1b(同步跟蹤)中,所有三個(gè)電源同時(shí)導(dǎo)通,并以相同的速率相互跟蹤,因此在施加較高電源電壓之前建立最低電源電壓。掉電以相反的方式完成。這是一個(gè)很好的例子,說明在較舊的FPGA或微處理器應(yīng)用中如何啟動(dòng)電源,在輔助或I/O電源啟動(dòng)之前,較低的內(nèi)核電壓應(yīng)該處于活動(dòng)狀態(tài)。本文稍后將展示賽靈思 Virtex-5 FPGA 的同步跟蹤示例。

在圖1c中,電源以不同的壓擺率啟動(dòng)。如前所述,控制電源壓擺率dV/dt的能力對(duì)于防止電路中的大去耦電容浪涌電流(充電電流)損壞非常有用。如果不加以控制,浪涌電流可能會(huì)大大超過正常工作電流。壓擺率限制可以防止有源器件閂鎖、電容器短路、PCB走線的潛在損壞以及直插式保險(xiǎn)絲熔斷。

在圖1d中,所有電源都具有相同的壓擺率,但其應(yīng)用時(shí)間由預(yù)定的失調(diào)電壓決定。這種類型的跟蹤適用于需要限制電源電壓差的設(shè)備;通常出現(xiàn)在混合信號(hào)元件(如DAC和ADC)的最大額定值部分。這種方法可以防止對(duì)零件造成永久性損壞。

基于 FPGA 的設(shè)計(jì)示例

使用FPGA的系統(tǒng)供電為處理多個(gè)電源系統(tǒng)的主題提供了很好的對(duì)象課程。正確控制FPGA電源可以決定可靠、可重復(fù)的設(shè)計(jì)與實(shí)驗(yàn)室中或更糟糕的現(xiàn)場(chǎng)可能出現(xiàn)的災(zāi)難性故障。大多數(shù)FPGA具有多個(gè)電源軌,通常標(biāo)記為V首席運(yùn)營(yíng)官, V科考和 VCCINT.這些電源分別用于為 FPGA 內(nèi)核、輔助電路(如時(shí)鐘和 PLL)和接口邏輯供電。

這些電源軌的考慮因素可分為:

軌道的排序

軌道電壓的公差要求

可能需要電源的軟啟動(dòng)或壓擺率控制。

作為說明性示例,請(qǐng)考慮 Xilinx Virtex-5 系列 FPGA 的電源要求,該系列提供廣泛的功能,包括邏輯可編程性、信號(hào)處理和時(shí)鐘管理。根據(jù)數(shù)據(jù)手冊(cè),Virtex-5 需要 V 的上電序列CCINT, V科考和 V首席運(yùn)營(yíng)官.這些電源相對(duì)于地的斜坡時(shí)間為200 μs(最小值至50 ms最大值)。推薦的工作條件如表1所示。

表 1.賽靈思 Virtex-5 電源軌要求

| 電壓范圍 | 最小/最大電壓 | 當(dāng)前 | 啟動(dòng)時(shí)間(分鐘) | 啟動(dòng)時(shí)間(最大) | ||

| VCCINT | 1 V ± 5% | –0.5 V 至 +1.1 V | 4 安培 | 200 微秒 | 50 毫秒 | 在 V 之前打開科考/V首席運(yùn)營(yíng)官 |

| V科考 |

2.5 V ± 5% |

–0.5 V 至 +3.0 V |

~50毫安 |

200 微秒 |

50 毫秒 | 在 V 之前打開首席運(yùn)營(yíng)官 |

| V首席運(yùn)營(yíng)官 |

3 V ± 5% |

–0.5 V 至 +3.75 V |

<50毫安 |

200 微秒 |

50 毫秒 |

如前所述,Virtex-5需要同步電壓跟蹤。此外,電源必須在特定的推薦工作容差范圍內(nèi),并且必須在指定的dV/dt范圍內(nèi)上升和下降。

但FPGA只是一個(gè)更大系統(tǒng)的一部分。為了詳細(xì)說明此示例,假設(shè)有一個(gè)高電流 5V 主系統(tǒng)電源軌。為 FPGA 內(nèi)核供電的 1V 電源容差為 ±5% (±50mV),需要提供高達(dá) 4A 的電流。3V 電源是容差為 ±5% 的通用邏輯電源,在本例中,需要提供 4A 電流才能為 FPGA I/O 和設(shè)計(jì)中的其他邏輯器件供電。2.5 V電源是一種模擬電源,必須提供100 mA的低噪聲電流。

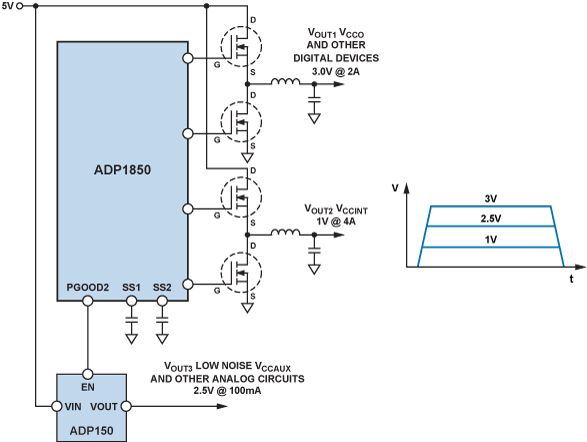

此應(yīng)用的一個(gè)良好解決方案是采用雙通道降壓控制器ADP1850,用于1 V和3 V大電流電源。ADP1850的特性包括軟啟動(dòng)控制、同步跟蹤以及從電源與主電源時(shí)序控制。上電斜坡速率由 SS1 和 SS2 引腳上的電容器控制。在本例中,3 V數(shù)字電源是主電源。對(duì)于2.5 V模擬電源,ADP150超低噪聲低壓差穩(wěn)壓器(LDO)是絕佳選擇;它可以從ADP1850的PGOOD2信號(hào)進(jìn)行排序。系統(tǒng)簡(jiǎn)化圖示,顯示了一般時(shí)序控制流程,如圖2所示(有關(guān)完整詳情,請(qǐng)參見ADP1850數(shù)據(jù)手冊(cè))。

圖2.用于 Virtex-5 的電源系統(tǒng)。

上面的例子說明了排序和跟蹤的常見用法;它可以擴(kuò)展到當(dāng)今的許多多電源系統(tǒng),包括基于微處理器的系統(tǒng)以及涉及混合信號(hào)技術(shù)的ADC和DAC系統(tǒng)。

模擬電壓和電流監(jiān)控 (ADM1191)

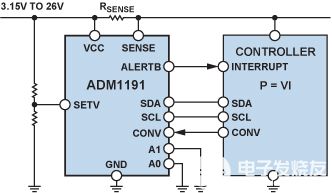

對(duì)于需要精確監(jiān)控多個(gè)系統(tǒng)電源電流和電壓的高可靠性應(yīng)用,可以使用易于部署的模擬監(jiān)控電路。例如,測(cè)量精度為1%的數(shù)字功率監(jiān)控器ADM1191包括一個(gè)用于電流和電壓回讀的12位ADC、一個(gè)精密電流檢測(cè)放大器和一個(gè)提供過流中斷的ALERTB輸出。圖3顯示了ADM1191在具有主機(jī)控制器(如微處理器或微控制器)的應(yīng)用中的應(yīng)用。

圖3.一個(gè)簡(jiǎn)單的電源電壓和電流監(jiān)視器。

ADM1191通過進(jìn)行通信I2C 總線到主機(jī)控制器。通過配置其A0和A1引腳的邏輯輸入電平,同一系統(tǒng)中總共可以尋址16個(gè)器件。本地控制器可以通過將測(cè)量的電壓和電流相乘來計(jì)算電源軌上的功耗。ALERTB 信號(hào)通過中斷控制器快速通知過流情況,即快速警告故障情況,以幫助保護(hù)系統(tǒng)免受損壞。

結(jié)合測(cè)序和監(jiān)測(cè)

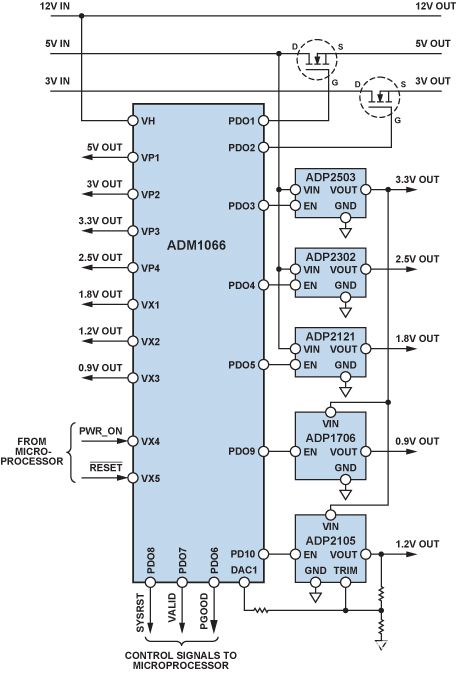

大型固定系統(tǒng),甚至一些高性能插件卡,都有許多需要控制和監(jiān)控的電源軌。圖4顯示的是一個(gè)具有8個(gè)電源軌的復(fù)雜電源系統(tǒng)。該系統(tǒng)的核心是ADM1066,這是一款靈活的高度集成的超級(jí)時(shí)序控制器,可提供完整的功率控制。功能包括排序、監(jiān)控、裕量調(diào)節(jié)和可編程性。ADM106x系列中的其他器件增加了溫度監(jiān)控和看門狗功能。

圖4.控制 8 軌電源系統(tǒng)。

8 軌系統(tǒng)有三個(gè)主電源軌:12 V、5 V 和 3 V。其他電源軌由這些電源軌派生而成,使用開關(guān)穩(wěn)壓器和LDO。每個(gè)穩(wěn)壓器都有一個(gè)使能輸入,由ADM1066的10個(gè)可編程驅(qū)動(dòng)器(PD)輸出之一驅(qū)動(dòng),從而允許用戶按受控順序啟動(dòng)所有電源軌。ADM1066內(nèi)置電荷泵,可升壓6個(gè)PD輸出電壓,為外部N-MOSFET提供高壓驅(qū)動(dòng),在需要控制更高電壓電源的情況下充當(dāng)電源軌開關(guān)。

ADM1066具有板載EEPROM,用于存儲(chǔ)電源系統(tǒng)控制參數(shù)。ADI公司提供的實(shí)用程序可簡(jiǎn)化器件配置。這使得啟動(dòng)和運(yùn)行的任務(wù)變得更加容易,消除了耗時(shí)的代碼開發(fā)。隨著系統(tǒng)的發(fā)展和新部件的加入,可以輕松調(diào)整供應(yīng)順序。時(shí)序參數(shù)和電壓跳變點(diǎn)可輕松重新編程。這一有價(jià)值的功能可節(jié)省開發(fā)時(shí)間并降低可能的電路板旋轉(zhuǎn)風(fēng)險(xiǎn)。

數(shù)字輸出信號(hào)——PWRGD(電源良好)、VALID和SYSRST(系統(tǒng)恢復(fù))——由ADM1066生成,用于在輪詢時(shí)或通過中斷或數(shù)字輸入通知系統(tǒng)微控制器電源系統(tǒng)的狀態(tài),以便在存在故障情況時(shí)采取措施。這種快速通知可以防止電容器短路和其他危險(xiǎn)情況造成的災(zāi)難性損壞。PWR_ON和/RESET是系統(tǒng)控制器到ADM1066的數(shù)字輸入,完成整個(gè)系統(tǒng)控制環(huán)路。

ADM1066的電源裕量調(diào)節(jié)

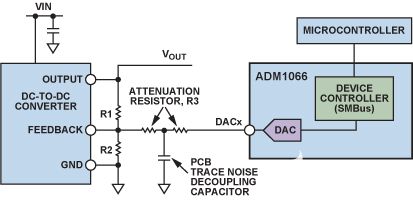

ADM1066的片內(nèi)DAC可用于在系統(tǒng)開發(fā)期間執(zhí)行電源裕量調(diào)節(jié),當(dāng)設(shè)計(jì)人員需要調(diào)整電源電壓以優(yōu)化其電平或使其遠(yuǎn)離標(biāo)稱值時(shí)。這種裕量調(diào)節(jié)功能允許系統(tǒng)在電源限值范圍內(nèi)進(jìn)行全面表征,而無需使用外部?jī)x器。該功能通常在在線測(cè)試(ICT)期間執(zhí)行,例如,當(dāng)制造商希望保證被測(cè)產(chǎn)品在標(biāo)稱電源電壓范圍內(nèi)±5%時(shí)正常工作時(shí)。從圖4所示電路開始,用戶可以在許多電源軌上實(shí)現(xiàn)裕量調(diào)節(jié)。

開環(huán)電源裕度

對(duì)電源進(jìn)行裕量調(diào)節(jié)的最簡(jiǎn)單方法(例如DC-DC轉(zhuǎn)換器或LDO)是將額外的電阻開關(guān)到電源模塊的反饋節(jié)點(diǎn)中,以改變反饋或微調(diào)節(jié)點(diǎn)處的電壓,從而使用DAC強(qiáng)制輸出電壓按所需量向上或向下裕量調(diào)節(jié)。使用這種衰減器(圖5),可以通過更新相關(guān)DAC輸出上的值,使用SMBus遠(yuǎn)程命令A(yù)DM11066為電源裕量。該過程可以使用開環(huán)技術(shù)實(shí)現(xiàn),獨(dú)立于系統(tǒng)控制回路。

圖5.開環(huán)裕量。

ADM1066可以使用六個(gè)板載電壓輸出DAC(DAC1至DAC6)驅(qū)動(dòng)到被裕量調(diào)節(jié)的功率模塊的反饋引腳,從而對(duì)多達(dá)6個(gè)電源執(zhí)行開環(huán)裕量調(diào)節(jié)。實(shí)現(xiàn)此功能的最簡(jiǎn)單電路是衰減電阻(R3),它將DACx引腳連接到DC-DC轉(zhuǎn)換器的反饋節(jié)點(diǎn)。當(dāng)DACx輸出電壓設(shè)置為等于反饋電壓時(shí),沒有電流流入衰減電阻,DC-DC轉(zhuǎn)換器輸出電壓不會(huì)改變。使DACx高于反饋電壓迫使電流進(jìn)入反饋節(jié)點(diǎn),DC-DC轉(zhuǎn)換器的輸出必須下降以補(bǔ)償這一點(diǎn)。為了提高DC-DC轉(zhuǎn)換器輸出,DACx輸出電壓設(shè)置為低于反饋節(jié)點(diǎn)電壓。為了降低噪聲,如圖所示,串聯(lián)電阻可以分成兩個(gè)電阻,它們之間的節(jié)點(diǎn)可以通過DC-DC轉(zhuǎn)換器上的電容對(duì)地去耦。

閉環(huán)電源裕度

更準(zhǔn)確和全面的裕量計(jì)算方法在閉環(huán)系統(tǒng)中使用類似的電路。圖4顯示了1.2 V輸出的示例。要裕量調(diào)節(jié)的電源軌上的電壓可以通過VX2回讀,以將電源軌精確地裕量到目標(biāo)電壓。ADM1066集成了實(shí)現(xiàn)此目的所需的所有電路,12位逐次逼近型ADC讀取監(jiān)控電壓電平,6個(gè)電壓輸出DAC如上所述調(diào)整電源電平。這些電路可與其他智能(如微控制器)一起使用,以實(shí)現(xiàn)閉環(huán)裕量調(diào)節(jié)系統(tǒng),該系統(tǒng)允許將任何DC-DC轉(zhuǎn)換器或LDO電源設(shè)置為任何電壓,精確到目標(biāo)的±0.5%以內(nèi)。

要在要測(cè)試的軌道上實(shí)現(xiàn)閉環(huán)裕量調(diào)節(jié),請(qǐng)使用以下步驟:

禁用六個(gè) DACx 輸出。

將DACx輸出電壓設(shè)置為等于反饋節(jié)點(diǎn)上的電壓。

啟用 DAC。

讀取連接到 VPx、VH 或 VXx 引腳之一的 DC-DC 轉(zhuǎn)換器輸出端的電壓。

如有必要,向上或向下修改DACx輸出電壓以調(diào)整DC-DC轉(zhuǎn)換器輸出電壓。否則停止;已達(dá)到目標(biāo)電壓。

將DAC輸出電壓設(shè)置為一個(gè)值,該值使電源輸出改變所需的量(例如,±5%)。

重復(fù)該過程,直到達(dá)到該電源軌所需的電壓。

步驟1至3確保當(dāng)每個(gè)DACx輸出緩沖器導(dǎo)通時(shí),它對(duì)DC-DC轉(zhuǎn)換器輸出幾乎沒有直接影響。DAC輸出緩沖器設(shè)計(jì)為上電時(shí)不會(huì)出現(xiàn)瞬態(tài)“毛刺”,方法是先上電緩沖器以跟隨引腳電壓。它此時(shí)不驅(qū)動(dòng)引腳。正確使能輸出緩沖器后,緩沖器輸入切換到DAC,緩沖器的輸出級(jí)導(dǎo)通,幾乎消除了輸出毛刺。

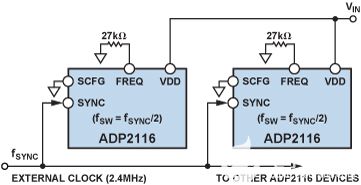

開關(guān)穩(wěn)壓器的同步

在使用多個(gè)開關(guān)穩(wěn)壓器或控制器的具有多個(gè)電源軌的系統(tǒng)中,由于內(nèi)部開關(guān)頻率的差異,這些器件存在交互的可能性。這可能會(huì)導(dǎo)致拍頻諧波,從而大大增加電源噪聲并對(duì)EMI測(cè)試造成嚴(yán)重破壞。幸運(yùn)的是,許多開關(guān)控制器和穩(wěn)壓器的設(shè)計(jì)允許其內(nèi)部時(shí)鐘同步。LDO 不存在這個(gè)問題,但由于它們的電流輸出有限,并且在大多數(shù)情況下效率低下,并不總是希望使用它們。

雙通道開關(guān)穩(wěn)壓器ADP2116是可同步器件的一個(gè)很好的例子。其 SYNC/CLKOUT 引腳可通過 SCFG 引腳配置為輸入 SYNC 引腳或輸出 CLKOUT 引腳。作為輸入SYNC引腳,它將ADP2116同步至外部時(shí)鐘;兩個(gè)通道以外部時(shí)鐘頻率的一半切換,彼此異相 180°。

作為 CLKOUT 引腳,它提供的輸出時(shí)鐘是通道開關(guān)頻率的兩倍,異相角度為 90°。因此,配置為CLKOUT選項(xiàng)的單個(gè)ADP2116可以充當(dāng)主轉(zhuǎn)換器,并為所有其他DC-DC轉(zhuǎn)換器(包括其他ADP2116器件)提供外部時(shí)鐘(圖6)。它們配置為從站,接受主站的外部時(shí)鐘并與之同步。通過同步系統(tǒng)中的所有DC-DC轉(zhuǎn)換器,這種方法可以防止可能導(dǎo)致EMI問題的拍頻諧波。

圖6.從外部時(shí)鐘同步ADP2116。

結(jié)論

本文討論處理多個(gè)電源系統(tǒng)的方法。時(shí)序控制器、監(jiān)視器、穩(wěn)壓器和控制器提供的高度功能集成使設(shè)計(jì)人員無需使用充滿分立IC的電路板即可解決潛在的電源問題,這種功能為設(shè)計(jì)人員提供了良好的價(jià)值,并以最少的重新設(shè)計(jì)和電路板旋轉(zhuǎn)增加了成功設(shè)計(jì)的幾率。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605993 -

控制器

+關(guān)注

關(guān)注

112文章

16445瀏覽量

179445 -

微處理器

+關(guān)注

關(guān)注

11文章

2274瀏覽量

82773 -

總線

+關(guān)注

關(guān)注

10文章

2903瀏覽量

88387

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

牽引供電系統(tǒng)的監(jiān)控測(cè)試系統(tǒng)的設(shè)計(jì)及應(yīng)用方案

多軌供電系統(tǒng)中的監(jiān)控和排序

多軌供電系統(tǒng)中的監(jiān)控和排序

評(píng)論