1. 偏移約束的作用

偏移約束(Offset Constraint)用來定義一個外部時鐘引腳(Pad)和數(shù)據(jù)輸入輸出引腳之間的時序關(guān)系,這種時序關(guān)系也被稱為器件上的Pad-to-Setup或Clock-to-Out路徑。這些約束對與外部元器件相連的接口十分重要,在這里,需要解釋兩個術(shù)語:

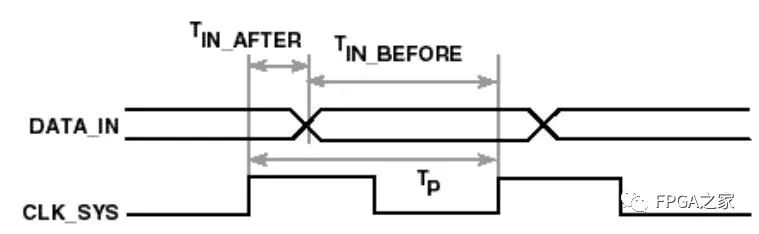

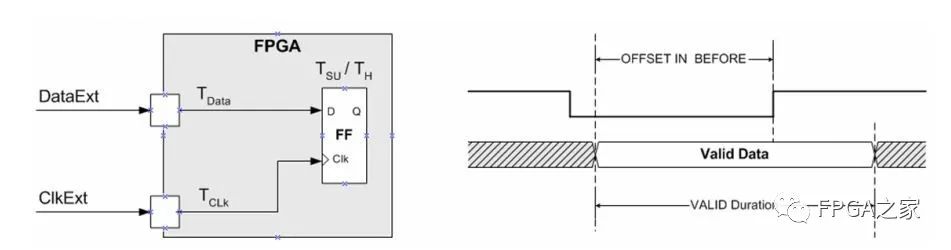

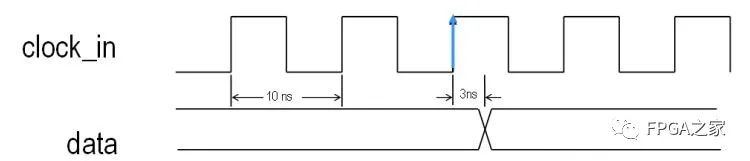

Pad-to-Setup:也被稱為OFFSET IN BEFORE約束,是用來保證外部輸入時鐘和外部輸入數(shù)據(jù)的時序滿足FPGA內(nèi)部觸發(fā)器的建立時間要求的。如下圖TIN_BEFORE約束使得FPGA在進行DATA_IN和CLK_SYS布線時努力保證DATA_IN相對于CLK_SYS的延時小于TIN_BEFORE。

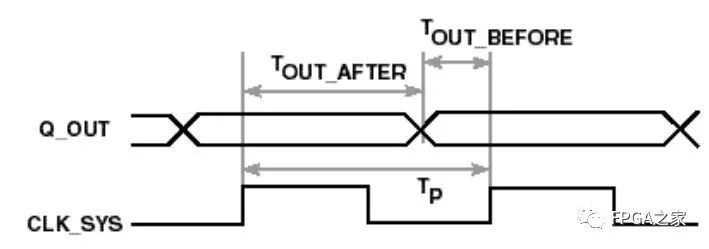

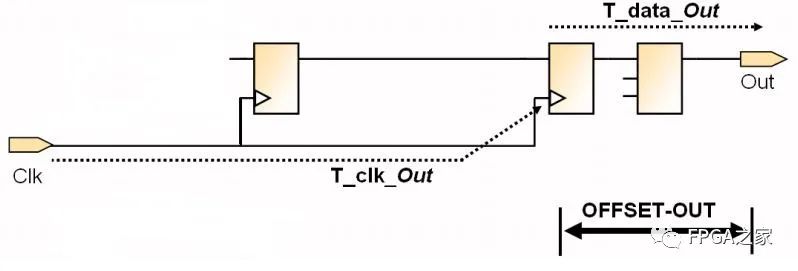

Clock-to-Out:也被稱為OFFSET OUT AFTER約束,是用來滿足下游器件建立保持(setup/hold)要求或輸出時鐘和數(shù)據(jù)之間時序要求的。

OFFSET IN BEFORE 或OFFSET OUT AFTER約束允許用戶指定外部輸入或輸出引腳相對于時鐘邊沿到內(nèi)部數(shù)據(jù)的延時。

1?1 輸入偏移約束時序參考圖

1?2 輸出偏移約束時序參考圖

Xilinx FPGA有三個層次的約束:

Global OFFSET:為所有輸入或輸出指定相對某個特定時鐘的約束;

Group OFFSET:為一組輸入或者輸出指定相對驅(qū)動他們的時鐘的約束

Net-Specific OFFSET:為某個特定的輸入或者輸出指定相對其驅(qū)動時鐘的約束;

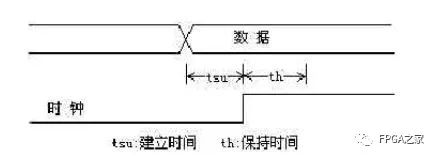

在進行約束的詳細講解之前,必須明確兩個概念:

建立時間setup time

指在觸發(fā)器始終上升沿到來之前,數(shù)據(jù)必須保持穩(wěn)定的時間,如果建立時間不夠,數(shù)據(jù)將不能被打入觸發(fā)器;

保持時間hold time

指觸發(fā)器的時鐘上升沿到來之后數(shù)據(jù)必須穩(wěn)定不變的時間,如果保持時間不夠,數(shù)據(jù)不能被打入觸發(fā)器;

1?3 建立保持時間時序圖

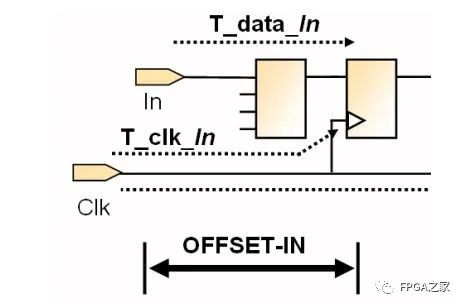

2. OFFSET IN約束

OFFSET IN約束用來設(shè)定Pad-to-Setup時序要求。OFFSET IN是對數(shù)據(jù)時鐘關(guān)系的一種說明。它當(dāng)分析建立時間要求(data_delay+setup-clock_delay-clock_arrival要求滿足約束條件)的時候,需要考慮時鐘延時(clock delay)、時鐘邊沿(clock edge)、DLL/DCM引入的時鐘相位。

2.1. OFFSET IN BEFORE 約束

OFFSET IN BEFORE約束限定了數(shù)據(jù)從引腳傳播到同步元件并在同步元件建立起來的所需的時間。比如 “OFFSET = IN 2 ns BEFORE clock_pad”這個約束,限定數(shù)據(jù)必須在下一個時鐘邊沿到來之前2ns內(nèi)讀取,因此FPGA會規(guī)劃使得數(shù)據(jù)相對時鐘邊沿的超前2ns之內(nèi)。

2?1 OFFSET IN BEFORE約束帶校準功能的電路

上圖FPGA在布線時會盡力去滿足如下不等式:

TData + TSetup - TClock 《= Toffset_IN_BEFORE;

2.1.1. VALID約束

OFFSET IN約束往往和VALID約束一起使用。OFFSET IN約束在建立時間分析中作為建立時間要求使用,而VALID約束在保持時間約束中作為保持時間要求使用。VALID約束指定了輸入數(shù)據(jù)的持續(xù)時間。在默認情況下,F(xiàn)PGA指定VALID和OFFSET的值相等,也即FPGA在默認情況下認為保持時間為0。

2?2 帶有VALID約束的輸入偏移約束

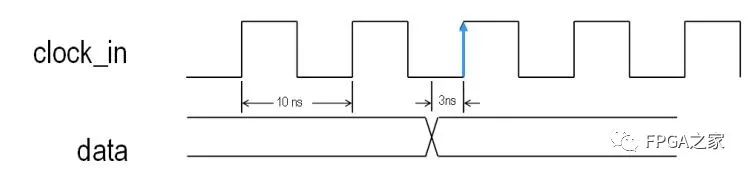

2.1.2. OFFSET IN約束的一個簡單例子

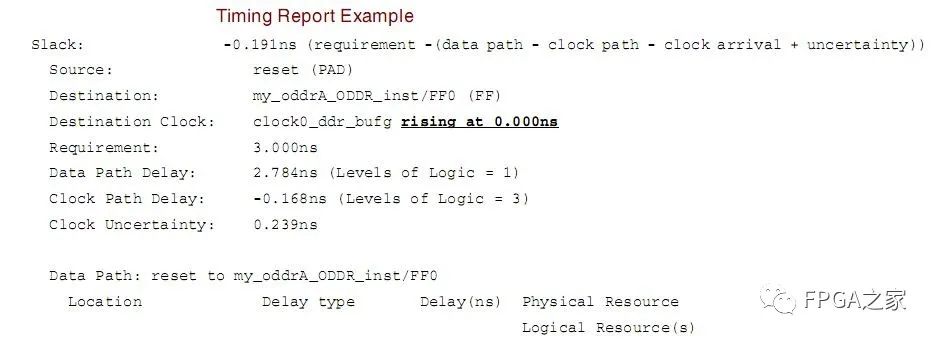

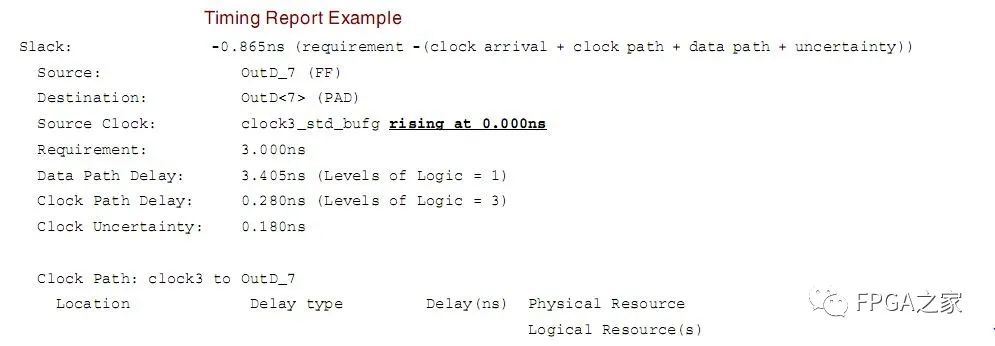

FPGA的分析工具在綜合時經(jīng)常會用到一個詞:Slack,即松弛時間,當(dāng)Slack》0時,該路徑設(shè)計滿足時序要求;當(dāng)Slack《0時,該路徑不滿足時序要求。

Slack = (Requirement - (Data Path - Clock Path - Clock Arrival))

2?3 OFFSET IN的簡單例子時序

該約束為:

TIMESPEC TS_clock = PERIOD clock_grp 10 ns HIGH 50%;

OFFSET = IN 3 ns BEFORE clock;

2?4 OFFSET IN約束時序報告

從時序約束報告的Slack的值可以看出,Data不能被Clock成功打入觸發(fā)器FF0.

2.2. OFFSET IN AFTER約束

OFFSET IN AFTER和OFFSET IN BEFORE在本質(zhì)上是一樣的,只是形式上不一樣,其約束效果是完全一樣的。OFFSET IN AFTER的約束公司如下:

TData + TSetup - TClock 《= TPeriod – Toffset_IN_AFTER;

3. OFFSET OUT約束

OFFSET OUT約束用來定義clock-to-pad時序要求。OFFSET OUT約束是對外部clock-to-data的說明并且必須考慮clock_delay、clock edge和DLL/DCM時鐘相位等。

3.1. OFFSET OUT AFTER約束

OFFSET OUT AFTER約束定義了數(shù)據(jù)從同步元件傳播到管腳最長允許時間。可以形象地理解為時鐘邊沿到達器件邊界時數(shù)據(jù)離開器件邊界的時間。“OFFSET = OUT 2 ns AFTER clock_pad”約束意思是從FPGA數(shù)據(jù)端口傳輸?shù)较掠纹骷臄?shù)據(jù)在參考時鐘2ns之后一定可讀。

3?1 OFFSET OUT AFTER約束帶校準功能的電路

下面公式規(guī)定了數(shù)據(jù)時鐘的這種關(guān)系:

TQ + TClock2Out + TClock 《= Toffset_OUT_AFTER;

OFFSET OUT AFTER約束沿著參考時鐘路徑和數(shù)據(jù)路徑的最大延時不超過偏移值。

3.1.1. OFFSET OUT AFTER約束的一個簡單例子

同樣的,OFFSET OUT的Slack也定義了輸出約束的松弛時間:

Slack = (Requirement - (Clock Arrival + Clock Path + Data Path))

3?2 OFFSET OUT 約束的簡單例子

其約束應(yīng)寫為:

TIMESPEC TS_clock = PERIOD clock_grp 10 ns HIGH 50%;

OFFSET = OUT 3 ns AFTER clock;

3?3 OFFSET OUT 時序約束報告

時序報告中Slack=-0.865ns,不滿足時序約束要求。

3.2. OFFSET OUT BEFORE約束

同樣地,OFFSET OUT BEFORE和OFFSET OUT AFTER約束本質(zhì)上沒有什么不同,只是形式上的不一樣的,其約束效果完全一樣。

審核編輯 :李倩

-

FPGA

+關(guān)注

關(guān)注

1630文章

21798瀏覽量

606065 -

元器件

+關(guān)注

關(guān)注

113文章

4747瀏覽量

92828 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2003瀏覽量

61353

原文標題:FPGA編程技巧系列之輸入輸出偏移約束詳解

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

用Cyclone FPGA實現(xiàn)雙倍數(shù)據(jù)率輸入輸出接口

FPGA開發(fā)之時序約束(周期約束)

一文詳解FPGA編程技巧輸入輸出偏移約束

添加時序約束的技巧分析

XD和XL系列可編程控制器的規(guī)格參數(shù)和輸入輸出接線及運行維護的說明

nRF24LE1低功耗應(yīng)用詳解之輸入輸出口設(shè)計

STM32的8種GPIO輸入輸出模式

2、【STM32F0系列學(xué)習(xí)】之—通用輸入輸出端口(GPIO)

創(chuàng)建輸入輸出接口時序約束的竅門

Logos系列FPGA輸入輸出接口(IO)用戶指南

FPGA編程技巧系列之輸入輸出偏移約束詳解

FPGA編程技巧系列之輸入輸出偏移約束詳解

評論