數字邏輯器件可分為通用邏輯器件和ASIC兩種類型。從理論上講,應用通用邏輯器件(如4000系列和74HC系列)、微處理器和存儲器可以構建任何數字系統。但是,通用邏輯器件的規模一般都比較小,而且功能固定,在設計復雜數字系統時需要使用大量芯片,這會導致系統的體積難以縮小、功耗難以降低,同時受到器件傳輸延遲和芯片之間布線延遲的影響,使得系統的工作速度難以有效提高。

以2015年電子設計競賽題-數字頻率計的設計進行分析。競賽題目的要求設計并制作一臺閘門時間為1s的數字頻率計,能夠測量1Hz~100MHz矩形波信號的頻率。要求頻率測量的相對誤差不大于0.01%(10^-4)。

頻率是指周期信號在單位時間內的變化次數。頻率計用于測量周期信號的頻率,有直接法、周期法和等精度3種測頻方法。

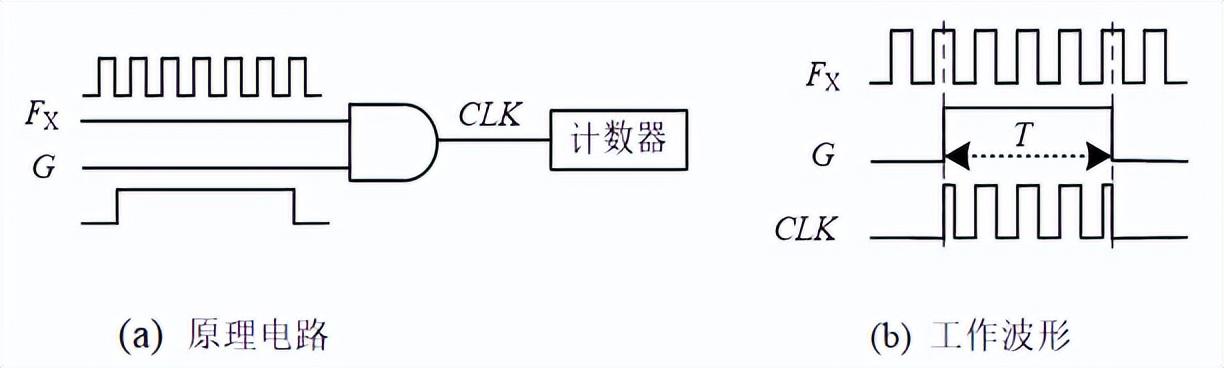

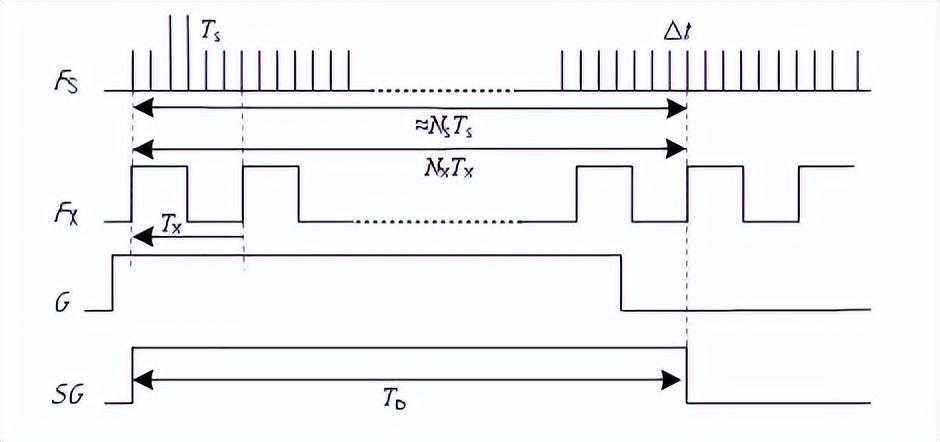

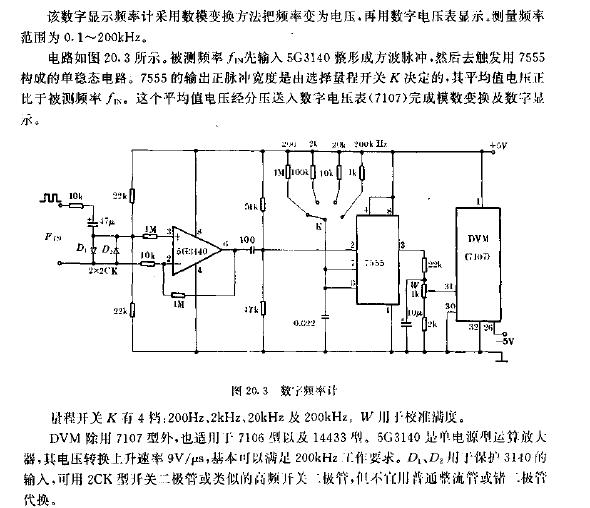

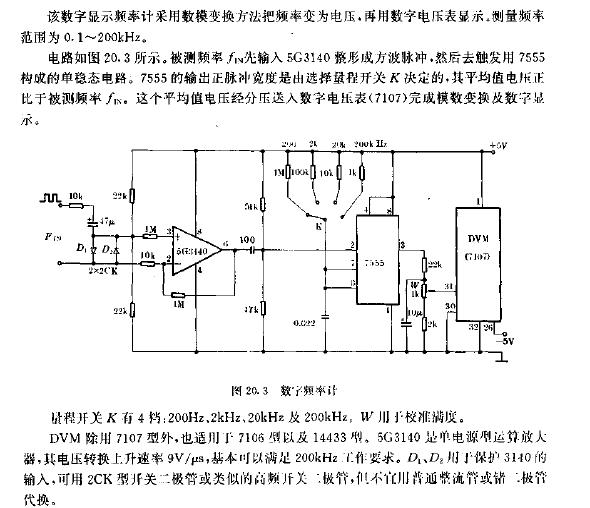

直接測頻法的原理電路如圖1(a)所示,其中與門的兩個輸入端分別接被測信號Fx和閘門信號G(Gate signal),與門的輸出作為計數器的時鐘。由閘門信號G控制計數器在固定的時間范圍內統計被測信號的脈沖數,如圖1(b)所示,脈沖數與時間之比即為被測信號的頻率。取閘門信號G的作用時間為1s時,計數器的計數值即為被測信號的頻率值。

圖1 直接測頻法原理

直接測頻法能夠測量信號頻率的范圍與閘門信號G的作用時間和計數器的容量有關。當閘門信號的作用時間為1s時,如果需要測量頻率為10kHz的信號時,那么要求計數器的容量為10^4,基于中、小規模通用邏輯器件實現時可以應用4片十進制計數器74HC160級聯實現。如果需要將測頻范圍擴展為100MHz,在閘門信號的作用時間同樣為1s的情況下,則要求計數器的容量為10^8,這就需要用8片74HC160級聯實現。一般地,在閘門信號作用時間固定的情況下,測量信號頻率的范圍越大,則計數所用的芯片越多,因而電路就越復雜。

當計數器的容量固定時,雖然可以通過縮短閘門信號的作用時間來擴展頻率測量范圍,但是會降低頻率測量的精度。這是因為,在直接測頻法中,閘門信號G的作用時間是隨機的,在計數過程中可能會存在1個脈沖的計數誤差。

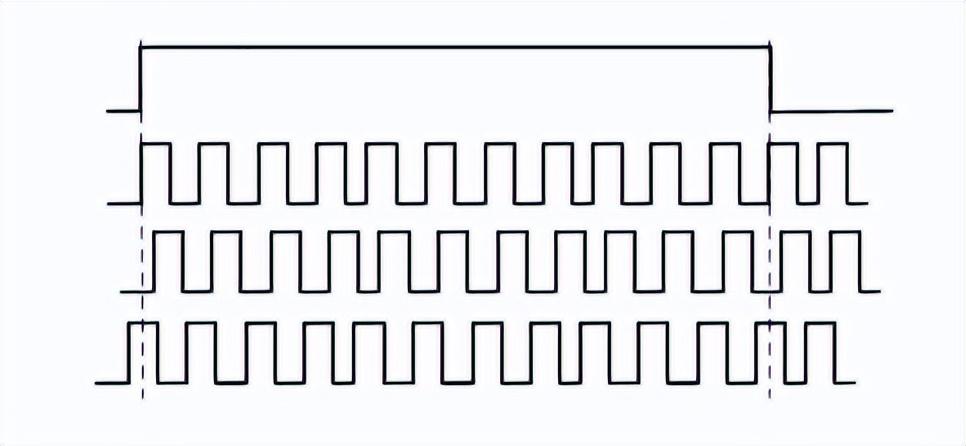

直接測頻法中計數誤差的成因分析如圖2所示,其中被測信號Fx1、Fx2和Fx3的頻率完全相同。設閘門信號G與被測信號Fx1同步,計數器在時鐘脈沖的上升沿工作。

圖2 直接測頻法誤差成因分析

在閘門信號G的作用下,如果對信號Fx1的計數值為N,則對信號Fx2的計數值為N-1,對信號Fx3的計數值為N+1。所以,取閘門信號的作用時間為1s時,直接測頻率法的計數誤差為±1Hz;取閘門信號的作用時間為0.1s時,則計數誤差為±10Hz。

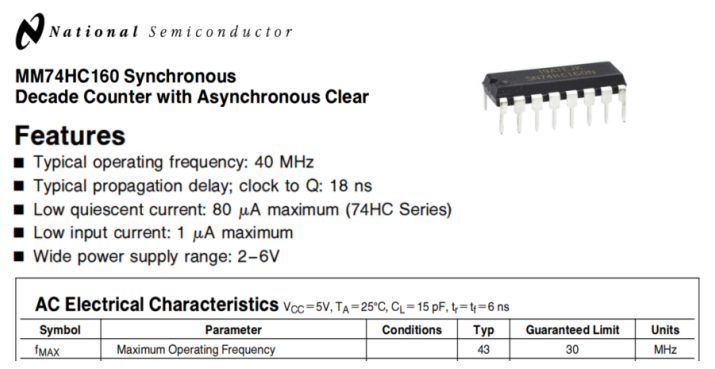

另外,基于中、小規模通用邏輯器件設計時還存在一個問題:頻率計的測頻范圍受計數器芯片性能的限制。查閱NI公司的器件資料可知,74HC160從時鐘到輸出(clock to Q)的傳輸延遲時間為18ns,典型工作頻率為40MHz,如圖3所示,極限工作頻率為43MHz。同時,應用多片74HC160級聯擴展計數容量時,還需要考慮芯片與芯片之間布線傳輸延遲的影響。因此,雖然用8片74HC160級聯理論上能夠擴展出108進制計數器,但實際上卻無法測量40MHz以上信號的頻率。

圖3 74HC160 器件資料片段

直接測頻法的原理簡單,但是由于理論上存在一個脈沖的計數誤差,所以被測信號的頻率越低,直接測頻法的相對誤差越大,存在著測量實時性和測量精度之間的矛盾。例如,取閘門信號的作用時間為1s,當被測信號的頻率為1000Hz時,理論上頻率測量的相對誤差為0.1%,而當被測信號的頻率為10Hz時,則頻率測量的相對誤差高達10%。

應用直接測頻法雖然可以通過增加閘門信號的作用時間來減小測頻誤差,但是,對于頻率為10Hz的信號,若要求頻率測量的相對誤差不大于0.01%,則閘門信號的作用時間最短為1000s。顯然,這么長的測量時間是無法接受的,所以直接測頻法不適合測量低頻信號的頻率。

從圖2可以看出,如果能夠控制閘門信號G與被測信號FX同步,那么就能夠消除計數誤差,因而從理論上講,頻率測量的相對誤差為0。

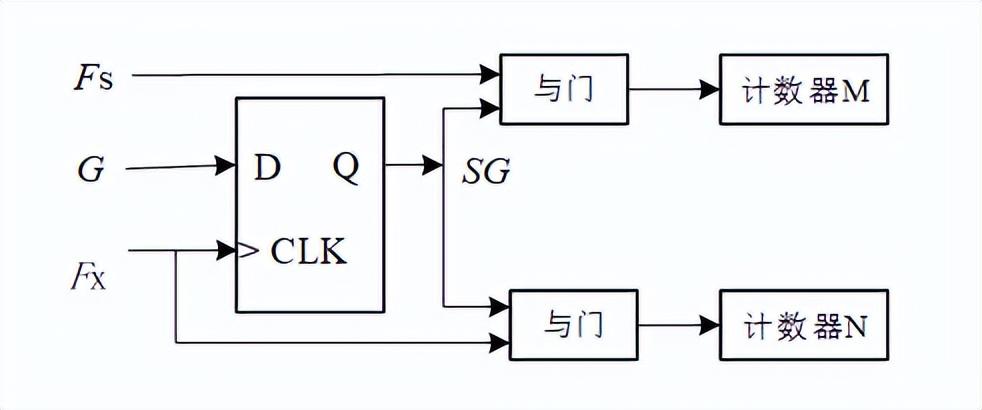

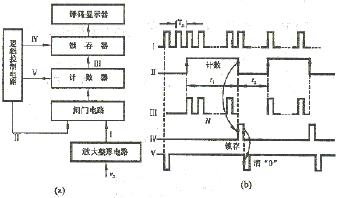

等精度測頻法就是通過控制閘門信號與被測信號同步從而消除了計數誤差,其原理電路如圖4所示,將閘門信號G作為邊沿D觸發器的輸入,被測信號Fx作為D觸發器的時鐘脈沖時,D觸發器輸出的新閘門信號SG(Synchronous Gate signal)與Fx同步。

圖4 等精度測頻法原理電路

等精度測頻法的工作原理是:當閘門信號G跳變為高電平時,只有當被測信號FX的上升沿到來時D觸發器輸出的新閘門信號SG才能跳變為高電平;當閘門信號G跳變為低電平時,同樣只有當被測信號Fx的上升沿到來時D觸發器輸出的新閘門信號SG才能跳變為低電平。因此,D觸發器輸出的新閘門信號SG與被測信號Fx嚴格同步,所以用新閘門信號控制計數器時,就能夠消除計數誤差。但是,由于新閘門信號SG的作用時間受被測信號Fx的控制,雖然取原閘門信號G的作用時間為1s,但新閘門信號的作用時間不一定為1s,因而計數器N中的計數值并不能代表被測信號的頻率值。改進的方法是,再添加一個與門和計數器M,在新閘門信號SG的作用時間內同時對被測信號Fx和一個標準頻率信號Fs進行計數,應用兩個計數器的計數時間完全相同的關系推算出被測信號的頻率值。

等精度測頻法被測信號頻率的計算原理如圖5所示。若將新閘門信號SG的作用時間記為TD,標準頻率信號Fs的周期記為Ts,被測信號Fx的周期記為Tx,在TD時間內對標準頻率信號和被測信號的計數值分別記為Ns和Nx,則閘門信號SG的作用時間TD可以精確地表示為

TD=Nx×Tx

圖5 等精度測頻法工作波形

雖然D觸發器輸出的新閘門信號SG與被測信號Fx嚴格同步,但并不一定與標準頻率信號Fs同步,所以從理論上講,在TD時間內對標準信號進行計數,仍然可能存在一個脈沖的計數誤差。因此,若用Ns×Ts表示TD時,則

TD≈Ns×Ts

如果取標準信號的頻率很高,使得Ts<

Ns×Ts≈Nx×Tx

若將標準頻率信號和被測信號的頻率分別用fs和fx表示,并將Ts=1/fs和Tx=1/fx代入上式整理可得

fx≈(Nx/Ns)×fs

其中,Ns和Nx分別為兩個計數器的計數值。根據上式即可計算出被測信號的頻率值。下面對等精度測頻的相對誤差進行分析。

設用Ns×Ts表示TD的誤差記為△t,則

△t=TD-Ns×Ts

設被測信號頻率的精確值記為fx0。由于TD=Nx×Tx0,所以fx0=Nx/TD,因此頻率測量的相對誤差δ可以表示為

δ =(fx-fx0)/fx0=fx/fx0-1

≈(fs×Nx/Ns) /(Nx/TD) -1

=TD/(Ts×Ns)-1

=(TD-Ts×Ns)/(Ts×Ns)

=△t/(Ts×Ns)

=△t/(TD-△t)

由于△t最大為一個標準頻率信號的周期,所以標準頻率信號的周期Ts<

δ≈Ts/TD

由上式可以看出,等精度測頻法頻率測量的相對誤差與被測信號的頻率無關,只取決于標準信號周期Ts與新閘門信號SG作用時間TD的比值。因此,取標準信號的頻率越高,或者閘門信號的作用時間越長,則頻率測量的相對誤差就越小。

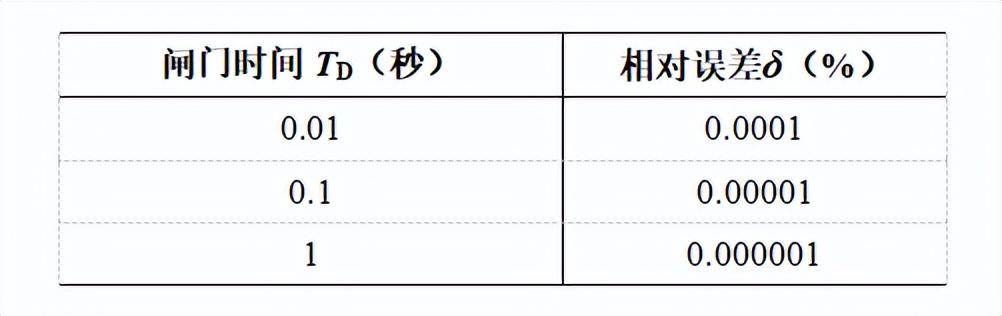

采用100MHz標準信號時,閘門信號的作用時間TD與測頻的相對誤差δ之間的關系如表1所示。可以看出,當閘門信號SG的作用時間為1s時,頻率測量的相對誤差約為0.000001%(10^-8),完全滿足競賽題目的精度要求。

表1 閘門信號作用時間與頻率測量誤差關系表

等精度測頻法頻率測量的精度很高,但是需要應用乘法和除法運算來計算被測信號的頻率值。取閘門信號G的作用時間為1s、標準信號的頻率為100MHz時,如果要求能夠測量100MHz信號的頻率時,不但需要應用27位二進制計數器(因為226<108<227)分別對被測信號Fx和標準頻率信號Fs進行計數,還需要應用27位二進制乘法器和54位二進制除法器來計算被測信號的頻率值。若應用74系列中、小規模通用邏輯器件來搭建27位乘法器和54位除法器,其電路的復雜程度是難以想象的。

那么,如何實現等精度頻率測量呢?提供以下3種方案:

(1)基于微控制器和PLD實現。

應用MCS-51、MSP430或者STM32等系列微控制器雖然計算乘除法很方便,但是對高頻信號進行計數則相對困難。若應用微控制器內部的計數/定時器來統計被測信號和標準信號的計數值,則會受到內部計數/定時器性能的限制,很難有效測量MHz級及以上信號的頻率。

如果在微控制器外圍擴展中規模集成計數器(如74HC161)進行計數,然后通過I/O口讀取被測信號和標準信號的計數值,通過編程計算被測信號的頻率值,不但外圍電路復雜,而且同樣會受集成計數器芯片性能的限制,測頻范圍難以有效擴展。因此,推薦應用可編程邏輯器件CPLD或者FPGA進行計數,基于微處理器計算乘除法。

(2)應用EDA技術,基于IP核實現。

應用EDA技術實現等精度頻率計時,可以直接用硬件描述語言描述所需要的計數器,然后在可編程邏輯器件中實現,不但不會受到具體器件功能的限制,而且計數器能夠正常工作的最高頻率遠遠超過100MHz。另外,還可以定制EDA軟件中的乘法IP和除法IP來實現乘除法運算,只需要將計算得到的二進制頻率值轉換為BCD碼顯示即可。

(3)應用EDA技術,基于片上系統實現。

在FPGA中搭建軟核處理器系統或者直接應用片內硬核處理器,用硬件描述語言描述所需要的計數器,應用片上處理器控制測頻過程,計算乘除法以及頻率轉換值與顯示。

綜上分析,要解決電子競賽中數字頻率計的設計問題,無論采用以上哪種方案設計等精度頻率計,都必須應用EDA技術。

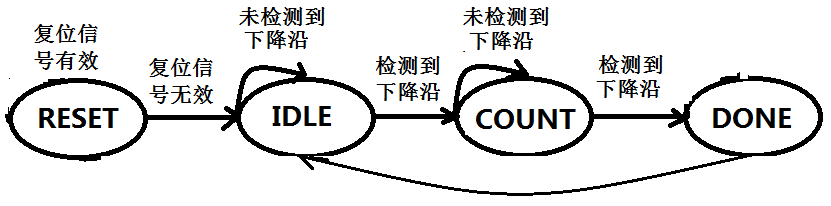

另外,等精度頻率計雖然測頻范圍寬,而且精度高,但測試表明,在閘門作用時間為1s的情況下,還不能滿足1Hz信號頻率測量的精度要求。為此,還需要設計周期法頻率計,與直接法頻率計或者等精度頻率計相配合,才能實現滿足競賽精度要求的1Hz~100MHz頻率計,而設計周期法頻率計需要應用圖6所示的狀態機來統計被測信號兩個相鄰脈沖之間的脈沖數,然后通過脈沖數計算出被測信號的周期,再根據頻率與周期之間的倒數關系應用除法計算出頻率值,同樣需要學習EDA技術。

圖6 周期測量狀態機

-

FPGA

+關注

關注

1630文章

21798瀏覽量

606040 -

asic

+關注

關注

34文章

1206瀏覽量

120766 -

微處理器

+關注

關注

11文章

2274瀏覽量

82778 -

邏輯器件

+關注

關注

0文章

88瀏覽量

20153 -

數字頻率計

+關注

關注

17文章

104瀏覽量

35823

發布評論請先 登錄

相關推薦

數字頻率計

設計簡易數字頻率計

數字頻率計的三種測頻方法

數字頻率計的三種測頻方法

評論