R-S觸發器又名復位-置位觸發器(R-復位RESET,S-置位SET。),基本結構是由兩個與非門(or或非門)的輸入、輸出端交叉連接而成。本人曾經做過一個項目,為半周期鎖定的DLL(即鎖相誤差為π)。這個DLL使用R-S觸發器當做鑒相器,來鑒別參考時鐘和反饋時鐘的相位差。

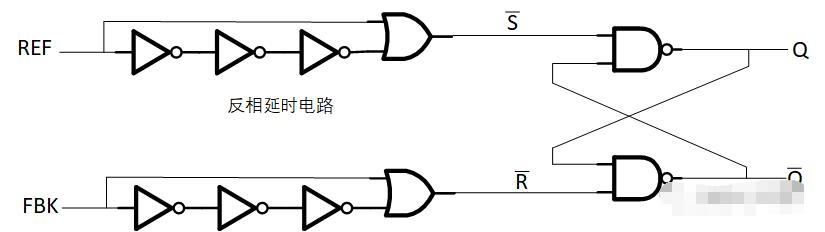

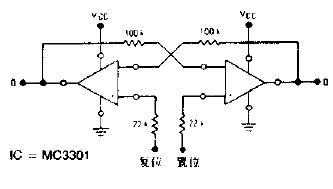

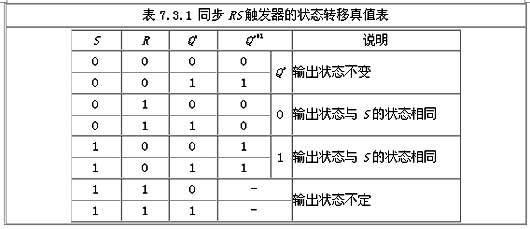

具體結構如下所示:

圖1 鑒相器

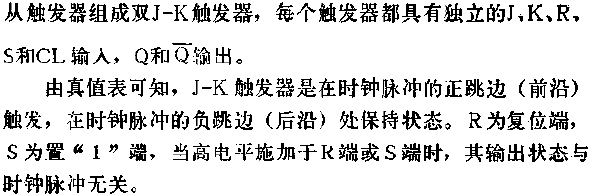

其中,R-S觸發器真值表如下,置位信號和復位信號都是低有效。

| 置位端 | 復位端 | Q |

QN |

|

0 |

0 |

X |

X |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

保持不變 |

保持不變 |

Note:當置位端和復位端都為0,當同時撤掉0之后,輸出狀態是不確定的。

圖1所示鑒相器電路。REF信號經過3級反相延時后的信號和初始信號進行邏輯或運算,得到R-S觸發器的置位信號。另一邊,FBK信號經過3級反相延時后的信號和初始信號進行邏輯或運算,得到R-S觸發器的復位信號。R-S觸發器在置位信號和復位信號控制下輸出Q和QN。而Q和QN可以作為UP、DN信號驅動后級的電荷泵電路。

鑒相原理:

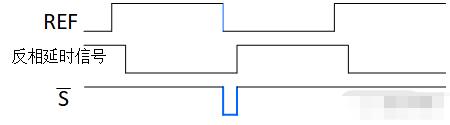

圖2 :信號的邊沿提取

如上圖所示,以REF為例,可以看到置位信號在REF的下降沿處產生負脈沖,負脈沖的寬度約等于3級反相器的延時大小。同理,復位信號將在FBK下降沿處同樣產生負脈沖。

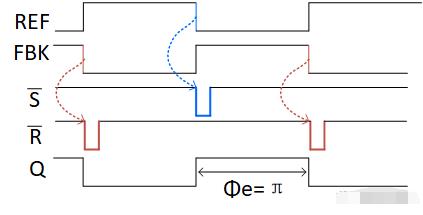

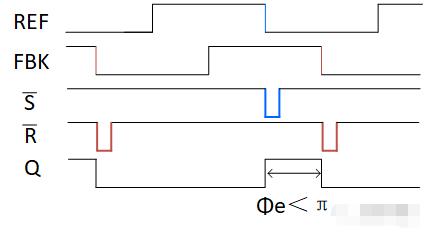

對于DLL而言,REF和FBK的頻率相同,所不同的只是相位的差別。用上面提到的方法,REF和FBK所對應的每個下降沿處將產生負脈沖,因此兩個負脈沖之間的寬度可以表示為相位誤差。進一步利用R-S觸發器的鎖存特性,可以用Q的高電平寬度代表相位誤差。這一點可以從下面的圖片直觀地表示出來。

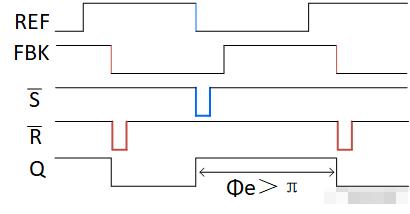

圖3:相位誤差為π時

圖4:相位誤差<π時

圖5:相位誤差>π時

總結:

本文提到的鑒相器用在半周期鎖定的DLL中,也就是說在半周期鎖定的應用中,環路鎖定狀態下相位誤差等于π。這一點和大多數的鎖相電路不同。對于常規的DLL,一般都是整周期延時鎖定,理論上鎖定時的相位誤差等于0。

-

dll

+關注

關注

0文章

116瀏覽量

45542 -

信號

+關注

關注

11文章

2804瀏覽量

77096 -

真值表

+關注

關注

0文章

25瀏覽量

15268 -

鑒相器

+關注

關注

1文章

61瀏覽量

23339 -

觸發器

+關注

關注

14文章

2003瀏覽量

61345

發布評論請先 登錄

相關推薦

R-S觸發器的鑒相原理

R-S觸發器的鑒相原理

評論