SPI是Serial Peripheral Interface的簡稱,是由Motorola公司推出的一種高速、全雙工的總線協議,可以實現一對一、一對多芯片通信。

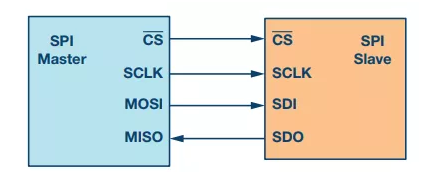

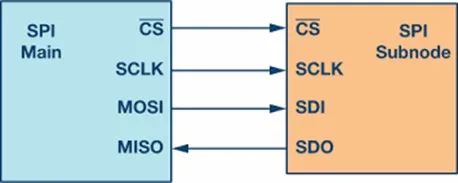

SPI由SCLK、CS/SSEL、MOSI,MISO四根線組成,

SCLK,時鐘信號,時鐘頻率即SPI速率,和SPI模式有關;

MOSI,主機輸出,從機輸入;

MISO,主機輸入,從機輸出;

CS/SSEL,從機設備選擇,低電平有效;

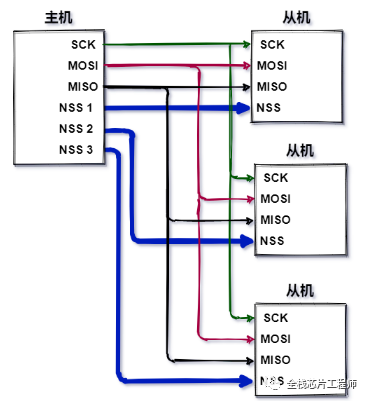

多從機模式

如果主機有多個片選CS端口,可采用下圖模式,主機只能獲取一個從機的MISO信號,其它從機輸出信號須為高阻。

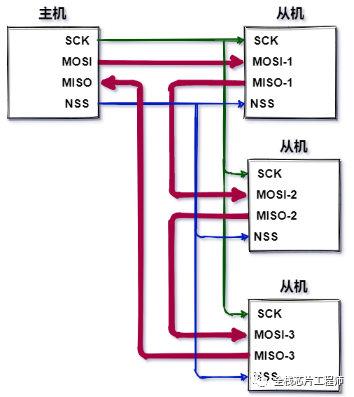

菊花鏈連接,節省GPIO、節省布線面積,但需要保證從機支持菊花鏈模式。

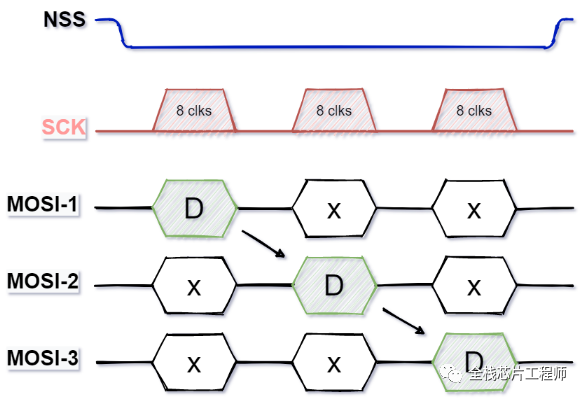

菊花鏈的數據傳輸時序:通過移位 送達數據。

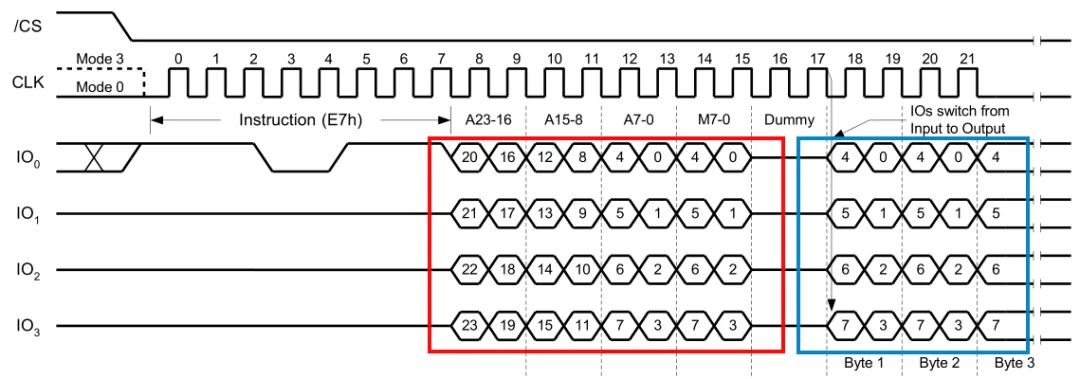

QSPI協議

QSPI協議讀寫時序:

注意,很多人寫公眾號都沒說清楚,為什么SPI能做到全雙工,而有些QSPI不能呢?

因為從下面時序圖可看到,發送時,待發送數據的一組8bit寄存器只在下降沿向左移位(高位先發,低位補充0即可),那么必然存在另一組8bit寄存器用以在上升沿接收數據,這樣就可以構成全雙工,而QSPI一般用FIFO/SRAM進行數據傳輸,基于成本考慮,一般只能半雙工。

SPI工作模式

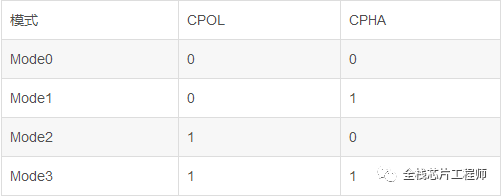

根據時鐘極性CPOL(Clock Polarity)、時鐘相位CPHA(Clock Phase),SPI有4種模式,最廣泛使用的是模式0和3:

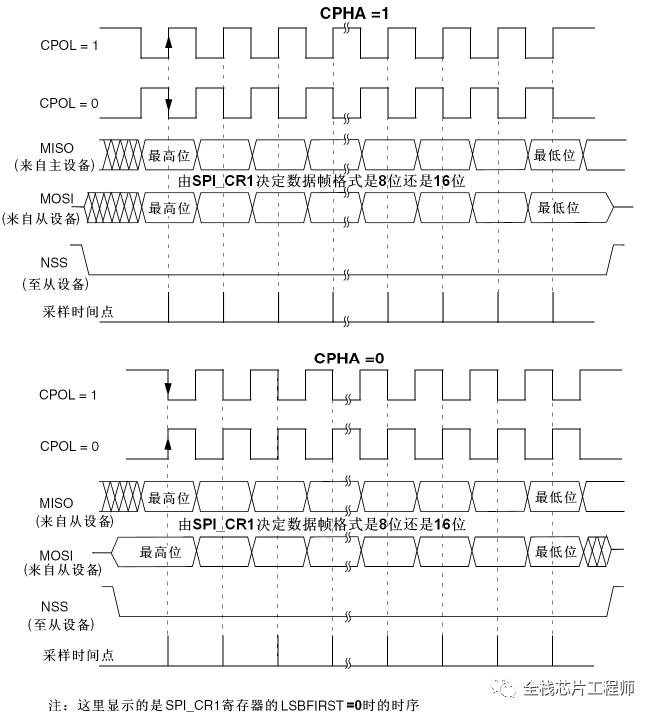

官方時序圖如下:

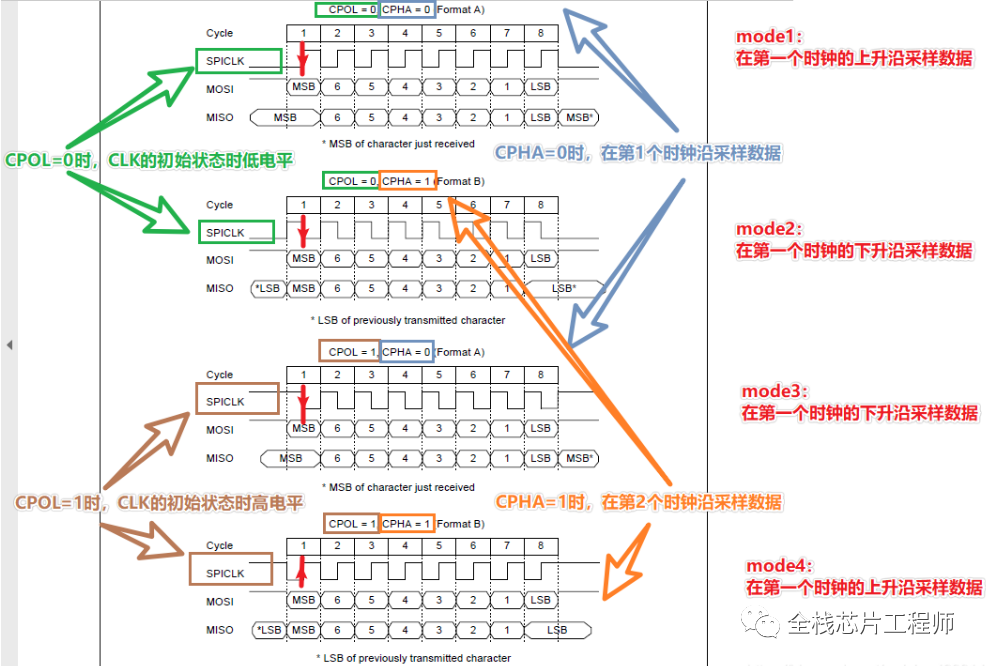

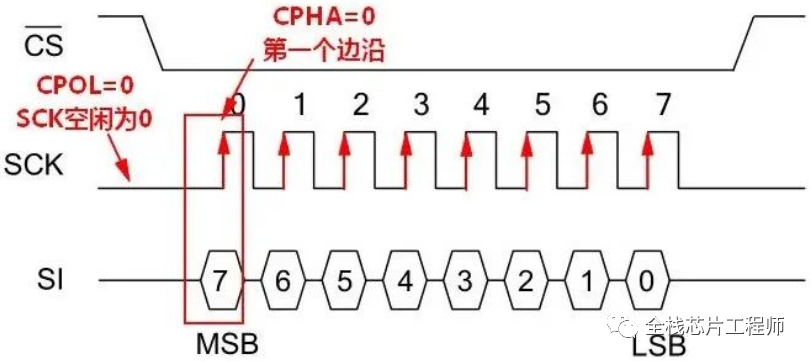

CPOL=0CPHA=0(常用)

CPOL=0,SPICLK空閑狀態為低電平;

CPHA=0,SPICLK第一個邊沿(上升沿)采集數據、第二個沿輸出數據;

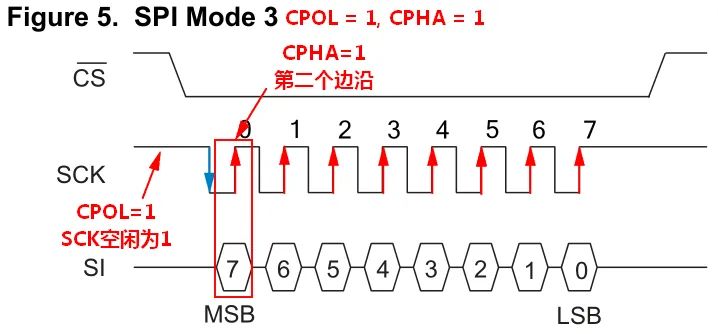

CPOL=1,CPHA=1 (常用)

CPOL=1,SPICLK空閑狀態為高電平;

CPHA=1,SPICLK第二個邊沿(上升沿)采集數據、第三個沿輸出數據;

? ?

? ?

CPOL=0,CPHA=1(不常用)

CPOL=0,SPICLK空閑狀態為低電平;

CPHA=1,SPICLK第二個邊沿(下升沿)采集數據、第三個沿輸出數據;

CPOL=1,CPHA=0

(不常用)

CPOL=1,SPICLK空閑狀態為高電平;

CPHA=0,SPICLK第一個邊沿(下升沿)采集數據、第二個沿輸出數據;

審核編輯:劉清

-

通信協議

+關注

關注

28文章

915瀏覽量

40439 -

SPI

+關注

關注

17文章

1721瀏覽量

92124 -

時鐘信號

+關注

關注

4文章

453瀏覽量

28664 -

miso

+關注

關注

0文章

7瀏覽量

5446

原文標題:詳解SPI通信協議

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

常用的串口通信協議之SPI協議簡析

一文搞懂SPI通信協議

SPI通信協議

通信協議(SPI)

i2c和spi通信協議的概念與區別 I2C/SPI總線通信協議你搞懂沒有

【世說知識】一文搞懂UART通信協議

SPI通信協議原理是什么

一文搞懂SPI通信協議

一文搞懂SPI通信協議

評論