調(diào)試寄存器

在x86/x64CPU內(nèi)部,還有一組用于支持軟件調(diào)試的寄存器。

調(diào)試,對于我們程序員是家常便飯,必備技能。但你想過你的程序能夠被調(diào)試背后的原理嗎?

程序能夠被調(diào)試,關(guān)鍵在于能夠被中斷執(zhí)行和恢復(fù)執(zhí)行,被中斷的地方就是我們設(shè)置的斷點。那程序是如何能在遇到斷點的時候停下來呢?

對于一些解釋執(zhí)行(PHP、Python、JavaScript)或虛擬機執(zhí)行(Java)的高級語言,這很容易辦到,因為它們的執(zhí)行都在解釋器/虛擬機的掌控之中。

而對于像C、C++這樣的“底層”編程語言,程序代碼是直接編譯成CPU的機器指令來執(zhí)行的,這就需要CPU來提供對于調(diào)試的支持了。

對于通常的斷點,也就是程序執(zhí)行到某個位置下就停下來,這種斷點實現(xiàn)的方式,在x86/x64上,是利用了一條軟中斷指令:int 3來進行實現(xiàn)的。

注意,這里的int不是指高級語言里面的整數(shù),而是表示interrupt中斷的意思,是一條匯編指令,int 3則表示中斷向量號為3的中斷。

在我們使用調(diào)試器下斷點時,調(diào)試器將會把對應(yīng)位置的原來的指令替換為一個int 3指令,機器碼為0xCC。這個動作對我們是透明的,我們在調(diào)試器中看到的依然是原來的指令,但實際上內(nèi)存中已經(jīng)不是原來的指令了。

順便提一句,兩個0xCC是漢字【燙】的編碼,在一些編譯器里,會給線程的棧中填充大量的0xCC,如果程序出錯的時候,我們經(jīng)常會看到很多燙燙燙出現(xiàn),就是這個原因。

言歸正傳,CPU在執(zhí)行這條int 3指令時,將自動觸發(fā)中斷處理流程(雖然這實際上不是一個真正的中斷),CPU將取出IDTR寄存器指向的中斷描述符表IDT的第3項,執(zhí)行里面的中斷處理函數(shù)。

而這個中斷描述符表,早在操作系統(tǒng)啟動之初,就已經(jīng)提前安排好了,所以執(zhí)行這條指令后,操作系統(tǒng)的中斷處理函數(shù)將介入,來處理這一事件。

后面的過程就多了,簡單來說,操作系統(tǒng)會把觸發(fā)這一事件的進程凍結(jié)起來,隨后將這一事件發(fā)送到調(diào)試器,調(diào)試器拿到之后就知道目標(biāo)進程觸發(fā)斷點了。這個時候,咱們程序員就能通過調(diào)試器的UI交互界面或者命令行調(diào)試接口來調(diào)試目標(biāo)進程,查看堆棧、查看內(nèi)存、變量都隨你。

如果我們要繼續(xù)運行,調(diào)試器將會把之前修改的int 3指令給恢復(fù)回去,然后告知操作系統(tǒng):我處理完了,把目標(biāo)進程解凍吧!

上面簡單描述了一下普通斷點的實現(xiàn)原理。現(xiàn)在思考一個場景:我們發(fā)現(xiàn)一個bug,某個全局整數(shù)型變量的值老是莫名其妙被修改,但你發(fā)現(xiàn)有很多線程,很多函數(shù)都有可能會去修改這個變量,你想找出到底誰干的,怎么辦?

這個時候上面的普通斷點就沒辦法了,你需要一種新的斷點: 硬件斷點 。

這時候就該本小節(jié)的主人公調(diào)試寄存器登場表演了。

在x86架構(gòu)CPU內(nèi)部,提供了8個調(diào)試寄存器DR0~DR7。

DR0~DR3:這是四個用于存儲地址的寄存器

DR4~DR5 :這兩個有點特殊,受前面提到的CR4寄存器中的標(biāo)志位DE位控制,如果CR4的DE位是1,則DR4、DR5是不可訪問的,訪問將觸發(fā)異常。如果CR4的DE位是0,則DR4和DR5將會變成DR6和DR7的別名,相當(dāng)于做了一個軟鏈接。這樣做是為了將DR4、DR5保留,以便將來擴展調(diào)試功能時使用。

DR6 :這個寄存器中存儲了硬件斷點觸發(fā)后的一些狀態(tài)信息

DR7 :調(diào)試控制寄存器,這里面記錄了對DR0-DR3這四個寄存器中存儲地址的中斷方式(是對地址的讀,還是寫,還是執(zhí)行)、數(shù)據(jù)長度(1/2/4個字節(jié))以及作用范圍等信息

通過調(diào)試器的接口設(shè)置硬件斷點后,CPU在執(zhí)行代碼的過程中,如果滿足條件,將自動中斷下來。

回答前面提出的問題,想要找出是誰偷偷修改了全局整形變量,只需要通過調(diào)試器設(shè)置一個硬件寫入斷點即可。

描述符寄存器

所謂 描述符 ,其實就是一個數(shù)據(jù)結(jié)構(gòu),用來記錄一些信息,‘描述’一個東西。把很多個描述符排列在一起,組成一個表,就成了描述符表。再使用一個寄存器來指向這個表,這個寄存器就是 描述符寄存器 。

在x86/x64系列CPU中,有三個非常重要的描述符寄存器,它們分別存儲了三個地址,指向了三個非常重要的描述符表。

gdtr: 全局描述符表寄存器,前面提到,CPU現(xiàn)在使用的是段+分頁結(jié)合的內(nèi)存管理方式,那系統(tǒng)總共有那些分段呢?這就存儲在一個叫全局描述符表( GDT )的表格中,并用gdtr寄存器指向這個表。這個表中的每一項都描述了一個內(nèi)存段的信息。

ldtr: 局部描述符表寄存器,這個寄存器和上面的gdtr一樣,同樣指向的是一個段描述符表( LDT )。不同的是,GDT是全局唯一,LDT是局部使用的,可以創(chuàng)建多個,隨著任務(wù)段切換而切換(下文介紹任務(wù)寄存器會提到)。

GDT和LDT中的表項,就是段描述符,描述了一個內(nèi)存分段的信息。

一個表項占據(jù)8個字節(jié)(32位CPU),里面存儲了一個內(nèi)存分段的諸多信息:基地址、大小、權(quán)限、類型等信息。

除了這兩個段描述符寄存器,還有一個非常重要的描述符寄存器:

idtr : 中斷描述符表寄存器,指向了 中斷描述符表IDT ,這個表的每一項都是一個中斷處理描述符,當(dāng)CPU執(zhí)行過程中發(fā)生了硬中斷、異常、軟中斷時,將自動從這個表中定位對應(yīng)的表項,里面記錄了發(fā)生中斷、異常時該去哪里執(zhí)行處理函數(shù)。

IDT中的表項稱為 Gate ,中文意思為 門 ,因為這是應(yīng)用程序進入內(nèi)核的主要入口。雖然表的名字叫中斷描述符表,但表中存儲的不全是中斷描述符,IDT中的表項存在三種類型,對應(yīng)三種類型的門:

- 任務(wù)門

- 陷阱門

- 中斷門

三種描述符中都存儲了處理這個中斷/異常/任務(wù)時該去哪里處理的地址。三種門用途不一,其中中斷門是真正意義上的中斷,而像前面提到的調(diào)試指令int 3以及老式的系統(tǒng)調(diào)用指令int 2e/int 80都屬于陷阱門。任務(wù)門則用的較少,要了解任務(wù)門,先了解下任務(wù)寄存器。

任務(wù)寄存器

現(xiàn)代操作系統(tǒng),都是支持多任務(wù)并發(fā)運行的,x86架構(gòu)CPU為了順應(yīng)時代潮流,在硬件層面上提供了專門的機制用來支持多任務(wù)的切換,這體現(xiàn)在兩個方面:

CPU內(nèi)部設(shè)置了一個專用的寄存器—— 任務(wù)寄存器TR ,它指向當(dāng)前運行的任務(wù)。

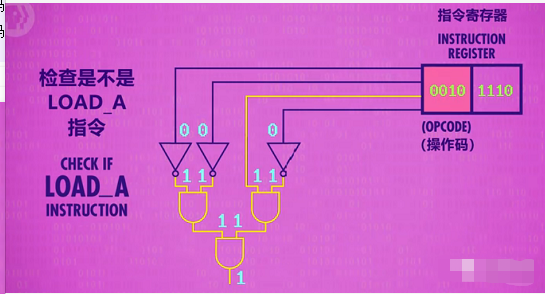

定義了描述任務(wù)的數(shù)據(jù)結(jié)構(gòu) TSS ,里面存儲了一個任務(wù)的上下文(一系列寄存器的值),下圖是一個32位CPU的TSS結(jié)構(gòu)圖:

x86CPU的構(gòu)想是每一個任務(wù)對應(yīng)一個TSS,然后由TR寄存器指向當(dāng)前的任務(wù),執(zhí)行任務(wù)切換時,修改TR寄存器的指向即可,這是硬件層面的多任務(wù)切換機制。

這個構(gòu)想其實還是很不錯的,然而現(xiàn)實卻打了臉,包括Linux和Windows在內(nèi)的主流操作系統(tǒng)都沒有使用這個機制來進行線程切換,而是自己使用軟件來實現(xiàn)多線程切換。

所以,絕大多數(shù)情況下,TR寄存器都是指向固定的,即便線程切換了,TR寄存器仍然不會變化。

注意,我這里說的的是絕大多數(shù)情況,而沒有說死。雖然操作系統(tǒng)不依靠TSS來實現(xiàn)多任務(wù)切換,但這并不意味著CPU提供的TSS操作系統(tǒng)一點也沒有使用。還是存在一些特殊情況,如一些異常處理會使用到TSS來執(zhí)行處理。

下面這張圖,展示了控制寄存器、描述符寄存器、任務(wù)寄存器構(gòu)成的全貌:

模型特定寄存器

從80486之后的x86架構(gòu)CPU,內(nèi)部增加了一組新的寄存器,統(tǒng)稱為 MSR寄存器 ,中文直譯是模型特定寄存器,意思是這些寄存器不像上面列出的寄存器是固定的,這些寄存器可能隨著不同的版本有所變化。這些寄存器主要用來支持一些新的功能。

隨著x86CPU不斷更新?lián)Q代,MSR寄存器變的越來越多,但與此同時,有一部分MSR寄存器隨著版本迭代,慢慢固化下來,成為了變化中那部分不變的,這部分MSR寄存器,Intel將其稱為Architected MSR,這部分MSR寄存器,在命名上,統(tǒng)一加上了IA32的前綴。

這里選取三個代表性的MSR簡單介紹一下:

- IA32_SYSENTER_CS

- IA32_SYSENTER_ESP

- IA32_SYSENTER_EIP

這三個MSR寄存器是用來實現(xiàn) 快速系統(tǒng)調(diào)用 。

在早期的x86架構(gòu)CPU上,系統(tǒng)調(diào)用依賴于軟中斷實現(xiàn),類似于前面調(diào)試用到的int 3指令,在Windows上,系統(tǒng)調(diào)用用到的是 int 2e ,在Linux上,用的是 int 80 。

軟中斷畢竟還是比較慢的,因為執(zhí)行軟中斷就需要內(nèi)存查表,通過IDTR定位到IDT,再取出函數(shù)進行執(zhí)行。

系統(tǒng)調(diào)用是一個頻繁觸發(fā)的動作,如此這般勢必對性能有所影響。在進入奔騰時代后,就加上了上面的三個MSR寄存器,分別存儲了執(zhí)行系統(tǒng)調(diào)用后,內(nèi)核系統(tǒng)調(diào)用入口函數(shù)所需要的段寄存器、堆棧棧頂、函數(shù)地址,不再需要內(nèi)存查表。快速系統(tǒng)調(diào)用還提供了專門的CPU指令sysenter/sysexit用來發(fā)起系統(tǒng)調(diào)用和退出系統(tǒng)調(diào)用。

在64位上,這一對指令升級為 syscall/sysret 。

總結(jié)

以上就是全部要介紹的寄存器了,需要說明一下的是,這并不是x86CPU全部所有的寄存器,除了這些,還存在XMM、MMX、FPU浮點數(shù)運算等其他寄存器。

這篇文章以x86/x64架構(gòu)CPU為目標(biāo),通過對CPU內(nèi)部寄存器的闡述,串講了CPU執(zhí)行代碼機制、內(nèi)存尋址技術(shù)、中斷與異常處理、多任務(wù)管理、系統(tǒng)調(diào)用、調(diào)試原理等多種計算機底層知識。

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121166 -

cpu

+關(guān)注

關(guān)注

68文章

10902瀏覽量

213017 -

X64

+關(guān)注

關(guān)注

0文章

5瀏覽量

7866 -

X86構(gòu)架

+關(guān)注

關(guān)注

0文章

6瀏覽量

6546

發(fā)布評論請先 登錄

相關(guān)推薦

移位寄存器怎么用_如何使用移位寄存器_移位寄存器的用途

寄存器變量

通過了解寄存器的功能與作用去揭秘CPU核心技術(shù)

CS,IP和PC寄存器

如何在VHDL中實現(xiàn)一個簡單的寄存器

如何使用ALU,RAM,寄存器打造一個CPU 1

如何使用ALU,RAM,寄存器打造一個CPU 3

cpu寄存器和存儲器的區(qū)別

45個寄存器、CPU核心技術(shù)大揭秘(上)

45個寄存器、CPU核心技術(shù)大揭秘(下)

45個寄存器、CPU核心技術(shù)大揭秘(下)

評論