系統(tǒng)時序設(shè)計中對時鐘信號的要求是非常嚴格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準。但實際中時鐘信號往往不可能總是那么完美,會出現(xiàn)抖動(Jitter)和偏移(Skew)問題。

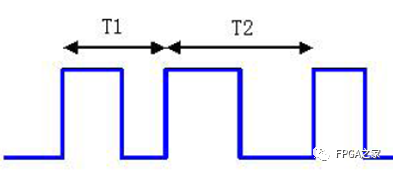

所謂抖動(jitter),就是指兩個時鐘周期之間存在的差值,這個誤差是在時鐘發(fā)生器內(nèi)部產(chǎn)生的,和晶振或者PLL內(nèi)部電路有關(guān),布線對其沒有影響。如下圖所示:

除此之外,還有一種由于周期內(nèi)信號的占空比發(fā)生變化而引起的抖動,稱之為半周期抖動。總的來說,jitter可以認為在時鐘信號本身在傳輸過程中的一些偶然和不定的變化之總和。

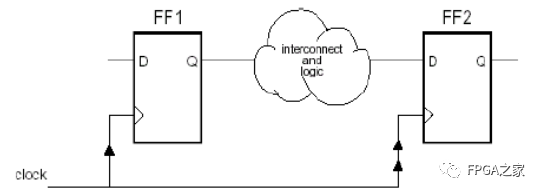

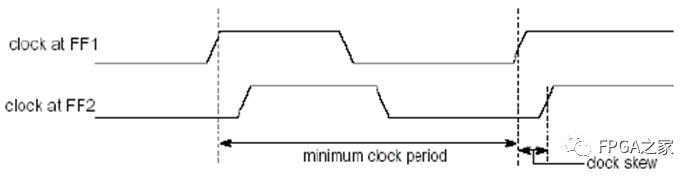

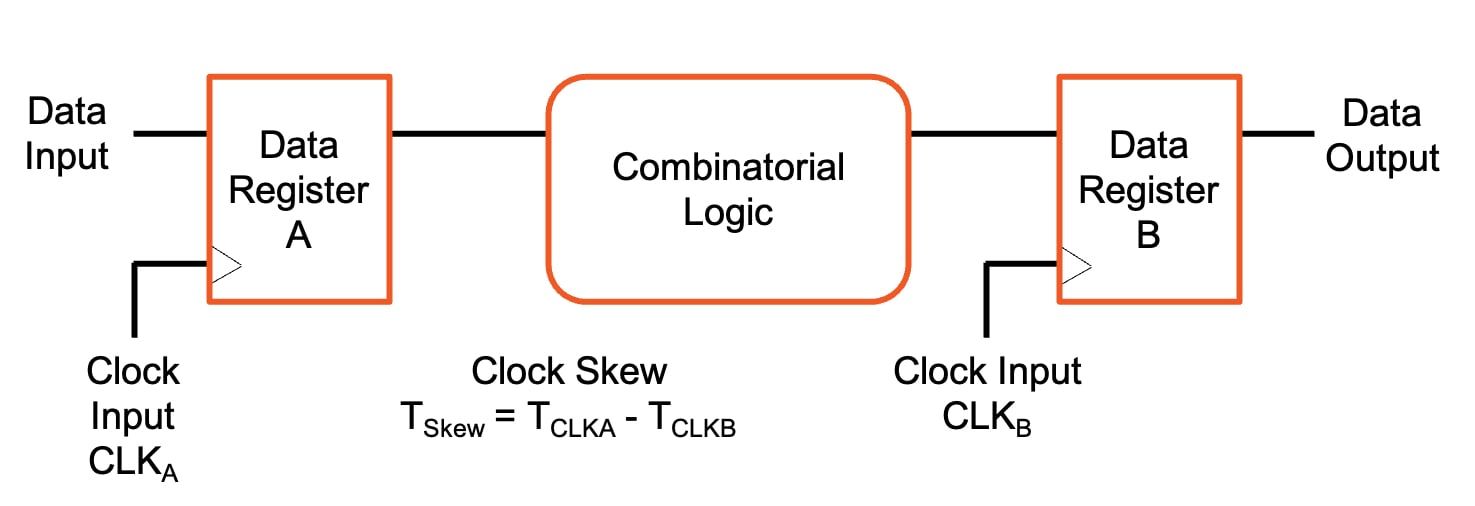

時鐘偏斜(skew)是指同樣的時鐘產(chǎn)生的多個子時鐘信號之間的延時差異。它表現(xiàn)的形式是多種多樣的,既包含了時鐘驅(qū)動器的多個輸出之間的偏移,也包含了由于PCB走線誤差造成的接收端和驅(qū)動端時鐘信號之間的偏移。

時鐘偏斜指的是同一個時鐘信號到達兩個不同寄存器之間的時間差值,時鐘偏斜永遠存在,到一定程度就會嚴重影響電路的時序。如下圖所示:

信號完整性對時序的影響,比如串擾會影響微帶線傳播延遲;反射會造成數(shù)據(jù)信號在邏輯門限附近波動,從而影響最大/最小飛行時間;時鐘走線的干擾會造成一定的時鐘偏移。有些誤差或不確定因素是仿真中無法預(yù)見的,設(shè)計者只有通過周密的思考和實際經(jīng)驗的積累來逐步提高系統(tǒng)設(shè)計的水平。

Clock skew 和Clock jitter 是影響時鐘信號穩(wěn)定性的主要因素。很多書里都從不同角度里對它們進行了解釋。

其中“透視”一書給出的解釋最為本質(zhì):

Clock Skew: The spatial variation in arrival time of a clock transition on an integrated circuit;

Clock jitter: The temporal vatiation of the clock period at a given point on the chip;

簡言之,skew通常是時鐘相位上的不確定,而jitter是指時鐘頻率上的不確定(uncertainty)。造成skew和jitter

的原因很多。由于時鐘源到達不同寄存器所經(jīng)歷路徑的驅(qū)動和負載的不同,時鐘邊沿的位置有所差異,因此就帶來了

skew。而由于晶振本身穩(wěn)定性,電源以及溫度變化等原因造成了時鐘頻率的變化,就是jitter。

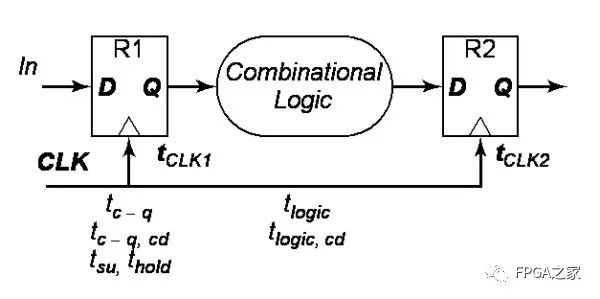

skew和jitter對電路的影響可以用一個簡單的時間模型來解釋。假設(shè)下圖中t(c-q)代表寄存器的最大輸出延遲,

t(c-q, cd)表示最大輸出延時;t(su)和t(hold)分別代表寄存器的setup, hold time(暫不考慮p.v.t)差異;t(logic)

和t(logic, cd)分別表示最大的組合邏輯傳輸延遲和最小組合邏輯傳輸延遲;

在不考慮skew和jitter的情況下,及t(clk1)和t(clk2)同頻同相時,時鐘周期T和t(hold)需要滿足

T > t(c-q) + t(logic) + t(su)

t(hold) < t(c-q, cd) + t(logic, cd)

這樣才能保證電路的功能正常,且避免競爭的發(fā)生。如果考慮CLK2比CLK1晚t1的相位,及skew=t1。

則 t(hold) < t(c-q, cd) + t(logic, cd) - t1

這意味著電路由更大的傾向發(fā)生hold time violation;如果考慮CLK1比CLK2晚t2的相位,及skew=-t2,

則 T > t(c-q) + t(logic) + t(su) + t2

這意味著電路的性能下降了,但由于R2的hold time始終滿足,所以不會有競爭的麻煩存在。clock jitter

始終是對性能造成負面的影響,一般設(shè)計中都需要專門留取10%左右的margin來保證。

clock uncertainty = clock jitter + clock skew. jitter 是 由時鐘源產(chǎn)生的抖動。skew是時鐘樹不平衡引起的到達兩個寄存器的延遲差。在cts之后,skew由工具算出,因此sta的時候clock uncertainty 可以設(shè)一個比較小的值。另外做hold check的時候因為檢查的是同一個時鐘沿,因此沒有jitter只有skew.

審核編輯:湯梓紅

-

驅(qū)動器

+關(guān)注

關(guān)注

53文章

8271瀏覽量

147056 -

晶振

+關(guān)注

關(guān)注

34文章

2899瀏覽量

68310 -

時鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131798 -

時鐘抖動

+關(guān)注

關(guān)注

1文章

62瀏覽量

15969 -

時鐘偏斜

+關(guān)注

關(guān)注

0文章

4瀏覽量

6376

原文標題:時鐘抖動(Clock Jitter)和時鐘偏斜(Clock Skew)

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Astro工具解決ASIC設(shè)計時鐘偏斜和干擾分析

在PCB設(shè)計中如何避免時鐘偏斜

大型多GHz時鐘樹中的時鐘偏斜

什么是時鐘偏斜?了解時鐘分配網(wǎng)絡(luò)中的時鐘偏斜

FPGA如何消除時鐘抖動

時鐘抖動和時鐘偏移的區(qū)別

CDC509高性能、低偏斜、低抖動、鎖相環(huán)(PLL)時鐘驅(qū)動器數(shù)據(jù)表

時鐘抖動和時鐘偏斜講解

時鐘抖動和時鐘偏斜講解

評論