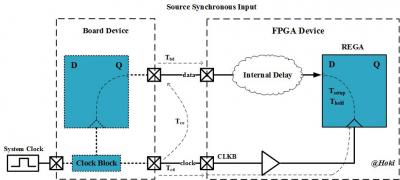

在設置input_delay時,我們經常會使用下面的方式:

set_input_delay-clockclk-min2[get_portsdata_in] set_input_delay-clockclk-max4[get_portsdata_in]

set_input_delay-clockclk-max2.1[get_portsdata_in] set_input_delay-clockclk-max1.9[get_portsdata_in]-clock_fall-add_delay set_input_delay-clockclk-min0.9[get_portsdata_in] set_input_delay-clockclk-min1.1[get_portsdata_in]-clock_fall-add_delay

在默認情況下,一個port只需要一個min和max的dealy值,如果我們設置兩次,那么第二次設置的值會覆蓋第一次的值:下面的第一行就無效了。

set_input_delay-clockclk-max2.1[get_portsdata_in] set_input_delay-clockclk-max2.5[get_portsdata_in]

但如果是加了-add_delay參數,就可以多個約束同時存在:

set_input_delay-clockclk-max2.1[get_portsdata_in] set_input_delay-clockclk-max2.5[get_portsdata_in]-add_delay

但其實,第一行也是無效的,因此2.5比2.1要大,如果滿足2.5了,那一定滿足2.1。

因此,-add_delay參數一般都是用于雙沿采樣的場景:

set_input_delay-clockclk-max2.1[get_portsdata_in] set_input_delay-clockclk-max1.9[get_portsdata_in]-clock_fall-add_delay

如果不增加-add_delay參數,那么第二條會覆蓋第一條約束,那么上升沿的約束就沒有了。

在UG903中,也有下面的描述:

AddDelayInputDelayCommandOption The-add_delayoptionmustbeusedif: ?Amax(ormin)inputdelayconstraintexists,and ?Youwanttospecifyasecondmax(ormin)inputdelayconstraintonthesameport. Thisoptioniscommonlyusedtoconstrainaninputportrelativetomorethanoneclock edge,as,forexample,DDRinterface

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

DDR

+關注

關注

11文章

715瀏覽量

65535 -

ADD

+關注

關注

1文章

20瀏覽量

9462

原文標題:set_input_delay中-add_delay的作用

文章出處:【微信號:傅里葉的貓,微信公眾號:傅里葉的貓】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA的IO約束如何使用

??set_input_delay屬于時序約束中的IO約束,我之前的時序約束教程中,有一篇關于set_input_delay的文章,但里面寫的并不是很詳細,今天我們就來詳細分析一下,這

發表于 09-06 09:22

?2015次閱讀

Vivado IP核心約束錯誤的解決辦法?

[get_clocks FT_CLK] -min -add_delay 1.000 [get_ports {FT_PDB }] set_input_delay -clock [get_clocks

發表于 04-27 09:11

保持輸入雙倍數據速率的時間錯誤的解決辦法?

vi_clk150Mhz]set_input_delay -clock [get_clocks vi_clk150Mhz] -clock_fall -min -add_delay 0.500 [get_ports DE

發表于 05-01 14:42

IDDR LVDS25時序違規如何改善?

[get_clocks clkin_adc_a] -clock_fall -max -add_delay 0.3 [get_ports {datain_adc_a_p }] set_input_delay -clock

發表于 08-06 06:07

input_delay應該設置為多少?

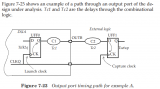

1、如下圖所示,當CLK1為100MHz時,約束set_input_delay -clocks CLK1 -max 5sig_a,如果CLK1變成50MHz,需要保證的約束效果不變,此時

發表于 07-22 07:11

FPGA設計約束技巧之XDC約束之I/O篇 (上)

從UCF到XDC的轉換過程中,最具挑戰的可以說便是本文將要討論的I/O約束了。 I/O 約束的語法 XDC 中可以用于 I/O 約束的命令包括 set_input_delay / set_ou

發表于 11-17 18:54

?1.3w次閱讀

set_max_delay被覆蓋的解決辦法

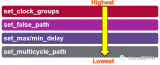

XDC描述的時序約束是有優先級的,尤其是涉及到時序例外的約束,如set_clock_groups、set_false_path、set_max_delay和set_multicycle

怎么解決有關于data保存時間的時序錯誤?

-min -add_delay -1.300 [get_ports rxData_n] set_input_delay -clock [get_clocks rxDco_p] -clock_fall

STM32上進行Delay延時的方法

1、使用SYStick專門的延時。void delay_us(uint32_t us){ static uint32_t delay_flag = 0; delay_flag = 1; /*

發表于 12-24 19:39

?2次下載

詳解FPGA的時序input delay約束

本文章探討一下FPGA的時序input delay約束,本文章內容,來源于配置的明德揚時序約束專題課視頻。

發表于 05-11 10:07

?4157次閱讀

set_output_delay的本質是什么?淺談set_ouput_delay時序

set_output_delay是對模塊output信號在模塊外部延遲的約束,本質上EDA工具會根據約束調整內部器件(UFF0)的類型,擺放位置以及組合邏輯(C1)以滿足約束要求,即EDA工具保證模塊DUA的UFF0的Tclk2q+Tc1延時能夠滿足約束要求。

詳細講解SDC語法中的set_input_delay和set_output_delay

在數字集成電路設計中,Synopsys Design Constraints(SDC)是一種重要的約束語言,用于指導綜合、布局布線等后續流程。

set_input_delay中-add_delay的作用簡析

set_input_delay中-add_delay的作用簡析

評論