現(xiàn)代接收器系統(tǒng)對(duì)更高容量和更多數(shù)據(jù)吞吐量的需求不斷增加。我們必須擁有高采樣率數(shù)據(jù)轉(zhuǎn)換器和高動(dòng)態(tài)范圍系統(tǒng)。一些模數(shù)轉(zhuǎn)換器(ADC)架構(gòu)確實(shí)實(shí)現(xiàn)了非常高的采樣率,但沒有最佳的信噪比(SNR)。其他器件可實(shí)現(xiàn)非常好的SNR,但其采樣率有限。沒有一個(gè)內(nèi)核ADC器件同時(shí)滿足高采樣速率和動(dòng)態(tài)范圍的要求。

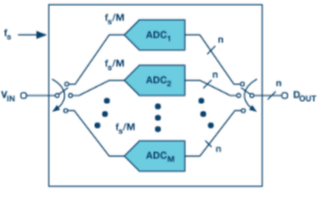

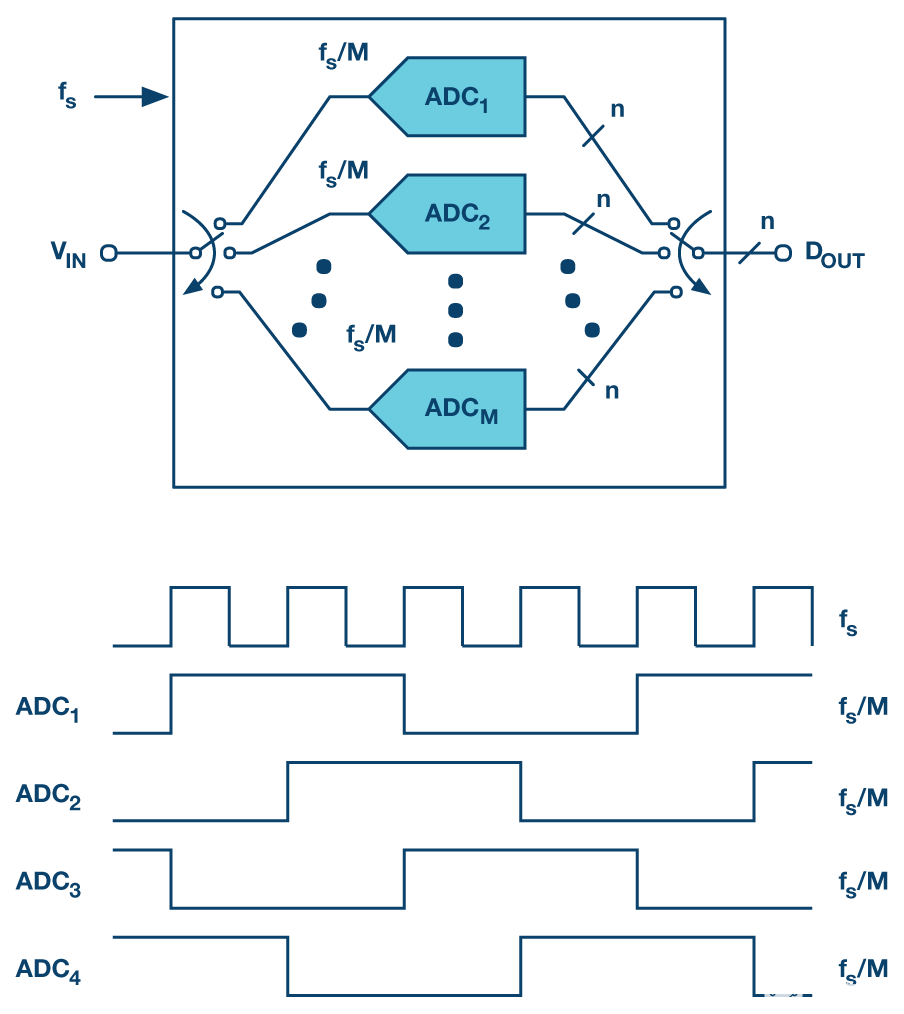

交錯(cuò)解決了這個(gè)問題。交錯(cuò)將多個(gè)低采樣速率轉(zhuǎn)換器組合在一起,以創(chuàng)建一個(gè)采樣速率較高的轉(zhuǎn)換器。每個(gè)轉(zhuǎn)換器的時(shí)鐘源都有延遲,因此信號(hào)采樣時(shí)間略有不同。樣本在輸出端組合成一個(gè)數(shù)據(jù)流。

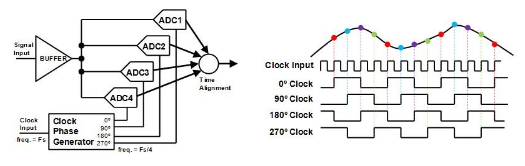

圖1:四路交錯(cuò)框圖和時(shí)序圖

圖1所示為四路交錯(cuò)式ADC示例。四個(gè)轉(zhuǎn)換器中的每一個(gè)都以相同的速率計(jì)時(shí)。時(shí)鐘的相位相對(duì)于每個(gè)轉(zhuǎn)換器偏移90度。時(shí)序圖說明了時(shí)鐘邊沿的延遲如何在不同時(shí)間對(duì)模擬信號(hào)進(jìn)行采樣。一旦數(shù)據(jù)在輸出端合并,數(shù)據(jù)流的樣本數(shù)是一個(gè)轉(zhuǎn)換器的四倍。這看起來像一個(gè)采樣速度是四倍的轉(zhuǎn)換器。復(fù)合SNR性能大致相當(dāng)于單個(gè)內(nèi)核的性能。

有一個(gè)問題:使用多個(gè)轉(zhuǎn)換器會(huì)增加功耗。此外,由于模擬電路的缺陷,小誤差會(huì)導(dǎo)致交錯(cuò)雜散。這些交錯(cuò)雜散會(huì)影響整體無雜散動(dòng)態(tài)范圍(SFDR)。

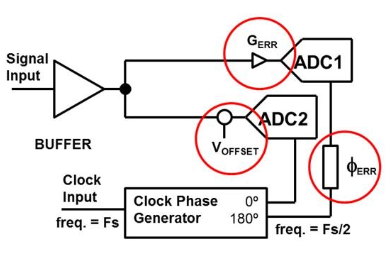

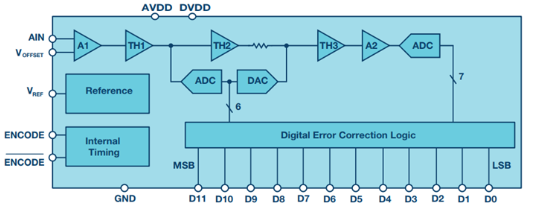

模擬誤差主要表現(xiàn)在三個(gè)方面,如圖2所示。直流失調(diào)失配會(huì)改變轉(zhuǎn)換器之間的相對(duì)共模,而增益和時(shí)鐘相位對(duì)齊誤差會(huì)導(dǎo)致信號(hào)采樣位置不精確。

圖 2:交錯(cuò)式 ADC 中的誤差源

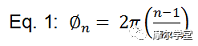

這些誤差轉(zhuǎn)化為捕獲頻譜中的雜散產(chǎn)物。失調(diào)誤差會(huì)引入離散雜散音。雜散的數(shù)量取決于交錯(cuò)內(nèi)核的數(shù)量 (N)。離散交錯(cuò)雜散(ILS)頻率位置相對(duì)于采樣速率(Fs)求出,公式1表示:

他們n= Fs*n/N 其中 n = 1, 2, ...N-1 (1)

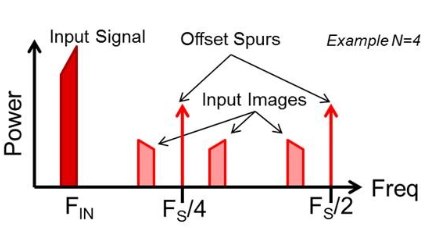

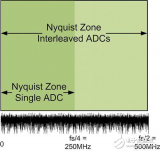

對(duì)于四路交錯(cuò)式ADC,交錯(cuò)雜散位于Fs/4和Fs/2。增益和時(shí)鐘相位的信號(hào)相關(guān)誤差產(chǎn)生以上述離散頻率位置為中心的圖像。圖3顯示了四路交錯(cuò)器件的交錯(cuò)雜散頻譜性能。

圖 3:四核器件的交錯(cuò)雜散

當(dāng)然,這些虛假產(chǎn)品是不可取的。在同一芯片上制造的ADC內(nèi)核本質(zhì)上會(huì)很好地匹配,但它們不會(huì)是完美的。需要校準(zhǔn)才能獲得良好的SFDR性能,通過模擬調(diào)整或在前景或背景中進(jìn)行數(shù)字調(diào)整來實(shí)現(xiàn)。前臺(tái)校準(zhǔn)要求器件停止處理數(shù)據(jù),同時(shí)校準(zhǔn)例程優(yōu)化性能。后臺(tái)校準(zhǔn)在ADC運(yùn)行時(shí)不斷更新調(diào)整,使其永遠(yuǎn)不會(huì)離線。

ADC12J4000 ADC使用四個(gè)交錯(cuò)內(nèi)核來實(shí)現(xiàn)4GSPS輸出采樣速率。該器件提供兩種交錯(cuò)校正選項(xiàng)。前臺(tái)校準(zhǔn)使采樣脫離,并在內(nèi)核修整時(shí)保持輸出數(shù)據(jù)靜態(tài)。根據(jù)校準(zhǔn)模式和采樣率,此過程可能需要數(shù)十毫秒才能完成。如果無法接受離線,則器件具有背景校準(zhǔn)模式,其中第五個(gè)內(nèi)核插入混音中。當(dāng)一個(gè)內(nèi)核脫機(jī)校準(zhǔn)時(shí),其他四個(gè)內(nèi)核正在正常進(jìn)行。然后,新校準(zhǔn)的內(nèi)核無縫聯(lián)機(jī),而另一個(gè)內(nèi)核關(guān)閉以進(jìn)行校準(zhǔn)。此過程重復(fù),而不會(huì)中斷輸出。

在室溫下,前景校正通常可以使交錯(cuò)雜散保持在-70 dBc以上。ADS54J60 是一款雙通道 ADC,每通道使用四個(gè)交錯(cuò)內(nèi)核來實(shí)現(xiàn) 1GSPS 輸出采樣速率。該轉(zhuǎn)換器采用專有的數(shù)字交錯(cuò)校正模塊來調(diào)整內(nèi)核不平衡。此校正方案始終在后臺(tái)工作,因此輸出數(shù)據(jù)流永遠(yuǎn)不會(huì)中斷。該方案可實(shí)現(xiàn)優(yōu)于-80 dBc的校正。

審核編輯:郭婷

-

接收器

+關(guān)注

關(guān)注

14文章

2481瀏覽量

72220 -

adc

+關(guān)注

關(guān)注

99文章

6534瀏覽量

545770 -

RF

+關(guān)注

關(guān)注

65文章

3059瀏覽量

167369

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于時(shí)間交錯(cuò)技術(shù)實(shí)現(xiàn)10位/400 MSPS ADC的設(shè)計(jì)

詳解時(shí)間交錯(cuò)技術(shù)

拓展一些關(guān)于交錯(cuò)ADC的觀點(diǎn)

利用多頻段無線電接收機(jī)——使用RF采樣ADC

RF采樣ADC的優(yōu)勢(shì)

一文詳細(xì)了解ADC時(shí)間交錯(cuò)技術(shù)

交錯(cuò)式ADC的基礎(chǔ)知識(shí)

交錯(cuò)ADC:揭開謎團(tuán)

RF采樣ADC在系統(tǒng)設(shè)計(jì)中具有優(yōu)勢(shì)

一文帶你了解交錯(cuò)式ADC(數(shù)據(jù)轉(zhuǎn)換器)

ADC08DJ5200RF射頻采樣千兆采樣模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADC12D1800RF一款RF采樣GSPS ADC數(shù)據(jù)表

ADC12D500RF, ADC12D800RF 12位1.6/1.0 GSPS RF采樣ADC數(shù)據(jù)表

ADC12D1x00RF 12位、3.2 GSPS和2 GSPS RF采樣ADC數(shù)據(jù)表

基于TI射頻直接采樣ADC(ADC32RF80)的RX鏈路設(shè)計(jì)

RF采樣:交錯(cuò)構(gòu)建更快的ADC

RF采樣:交錯(cuò)構(gòu)建更快的ADC

評(píng)論