如果你做過功能驗證并且開發過隨機用例,那么你就會知道場景組合會如雪球般地爆炸增長。

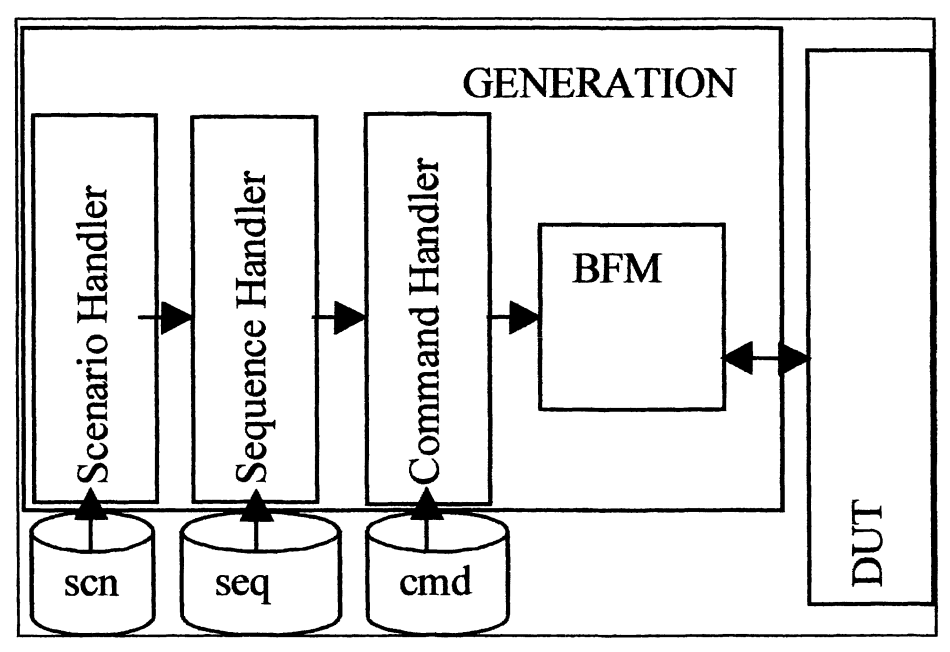

Sequences和Scenarios的概念就是通過分層的方法解決芯片流程驗證的復雜性。

通常,這種分層方法涉及三個層次。舉個例子,大多數芯片都有一個軟件配置接口,用于配置和控制芯片。

第一層是指令。我們為每個命令創建一個類來保存BFM信息(命令字段、數據字段和時序相關字段)。

第二層是基礎命令的組合,就是序列層。我們可以約束每個命令的各個字段,將這少數幾個命令組合成一個簡單的序列,例如配置序列、中斷處理和內存操作序列等。考慮實際的情況,序列層也可以復雜,凡事沒有絕對。

第三層是場景層。我們將多個序列組合成一個場景,例如先配置軟件接口,然后發送內存讀寫,最后處理中斷。序列之間可以串行或者并行組合。

命令、序列和場景的劃分會讓我們的功能驗證更加有條理,也更容易實現。這和我們的代碼開發一樣,只有良好的分層,驗證代碼可重用、可理解和可擴展的。

審核編輯:劉清

-

控制芯片

+關注

關注

2文章

511瀏覽量

39462 -

中斷處理

+關注

關注

0文章

94瀏覽量

11015 -

BFM

+關注

關注

0文章

3瀏覽量

6681

原文標題:芯片功能驗證中的Sequences和Scenarios

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Veloce平臺在大規模SOC仿真驗證中的應用

關于功能驗證、時序驗證、形式驗證、時序建模的論文

數字IC驗證之“UVM”基本概述、芯片驗證和驗證計劃(1)連載中...

各種驗證技術在SoC設計中的應用

Programming Sequences and Tips

關于無源高頻電子標簽芯片功能驗證的FPGA原型驗證平臺設計

可重用的驗證組件中構建測試平臺的步驟

解讀芯片驗證中的機器學習技術

芯片功能驗證中的Sequences和Scenarios介紹

芯片功能驗證中的Sequences和Scenarios介紹

評論