一、寫(xiě)在文前

目前對(duì)于DDR4、DDR5等并行信號(hào),信號(hào)速率越來(lái)越高,電源性能要求也越來(lái)越高,今天我們就來(lái)看看電源噪聲對(duì)信號(hào)質(zhì)量的影響;

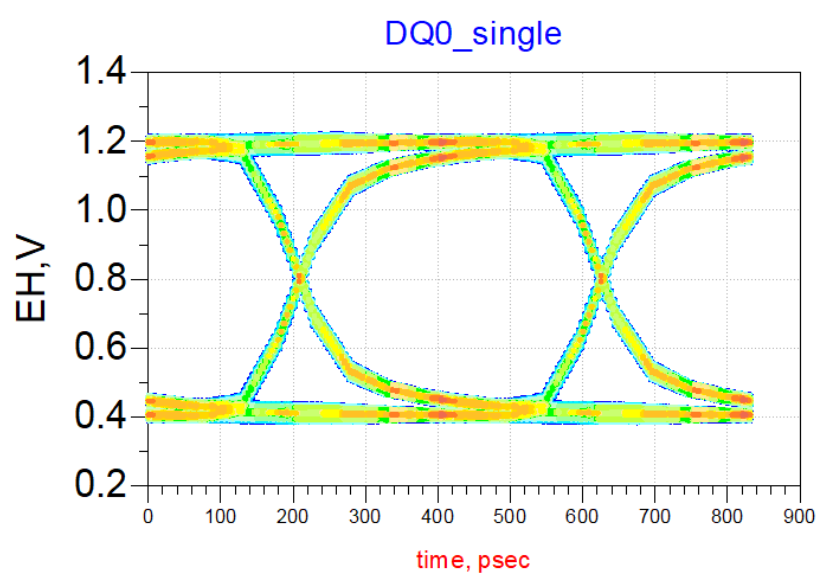

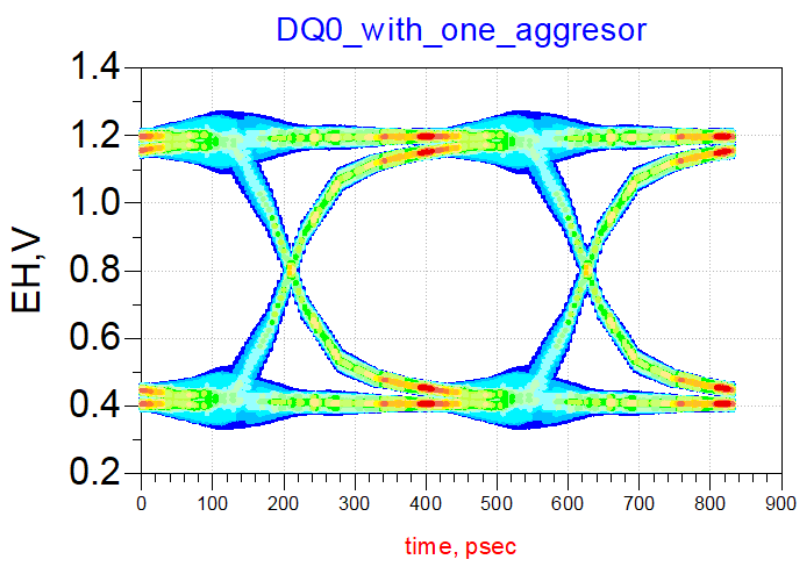

先來(lái)看下面的一組DQ 信號(hào),信號(hào)速率為2400Mbps,眼圖如下:

從眼圖來(lái)看,還是不錯(cuò)的,但是現(xiàn)在對(duì)于DDR信號(hào)而言,除了信號(hào)單通道的影響外,還有一些其他影響,比如臨近線(xiàn)的串?dāng)_,在上圖信號(hào)的基礎(chǔ)上,增加了一個(gè)臨近線(xiàn)的串?dāng)_,眼圖如下:

可以看到,眼圖惡化了不少,上面這只是其中一條表層微帶線(xiàn)的影響,平行走線(xiàn)為400mil,線(xiàn)間距為2*w(中心距);

當(dāng)然這不是本文的重點(diǎn),本文的重點(diǎn)是討論一下電源對(duì)信號(hào)的影響;

二、DDR4-2400信號(hào)電源聯(lián)合仿真

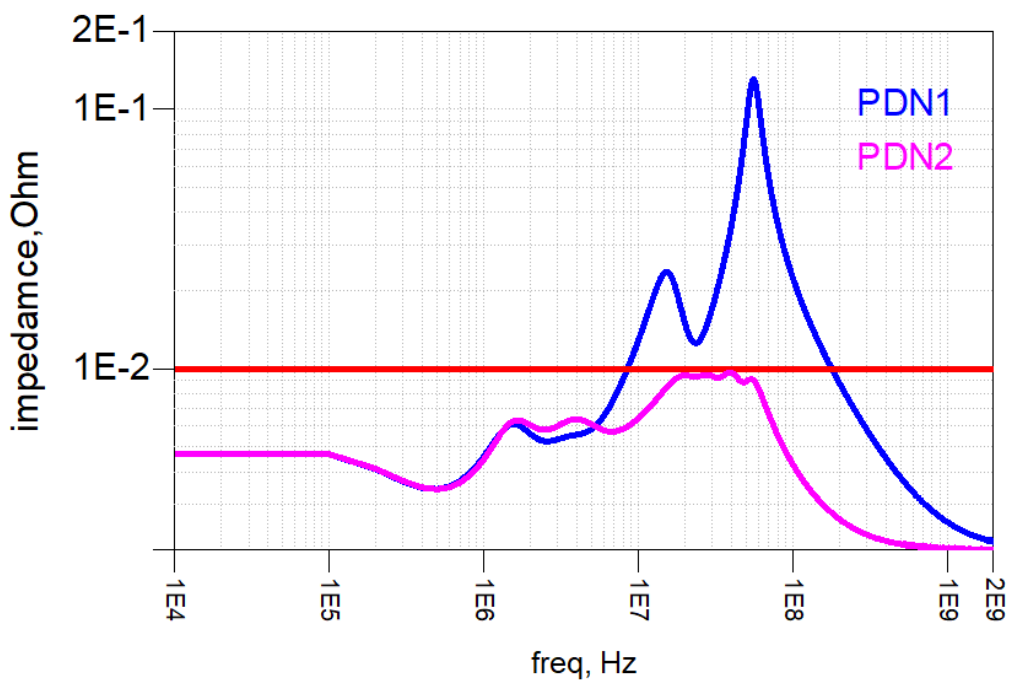

為了對(duì)比,我們?cè)O(shè)計(jì)了兩組電源系統(tǒng)(以下用PDN1、PDN2代替),包含了DIE_model、PKG、PCB以及VRM的RL等效模型;其各自的PDN阻抗曲線(xiàn)對(duì)比如下:

可以很明顯看出,PDN1的阻抗曲線(xiàn)在15MHz和50MHz處有較大諧振,阻抗值已經(jīng)達(dá)到了0.1Ohm,而PDN2的阻抗則比較平坦,且都保持在0.01Ohm以下;

對(duì)于PDN1的電源系統(tǒng),很容易產(chǎn)生比較大的噪聲,而DDR4這種多端口并行鏈路很容易產(chǎn)生同步跳變電流,從而作用在PDN1這樣的系統(tǒng)中,進(jìn)而產(chǎn)生電源噪聲,影響芯片電路和信號(hào);

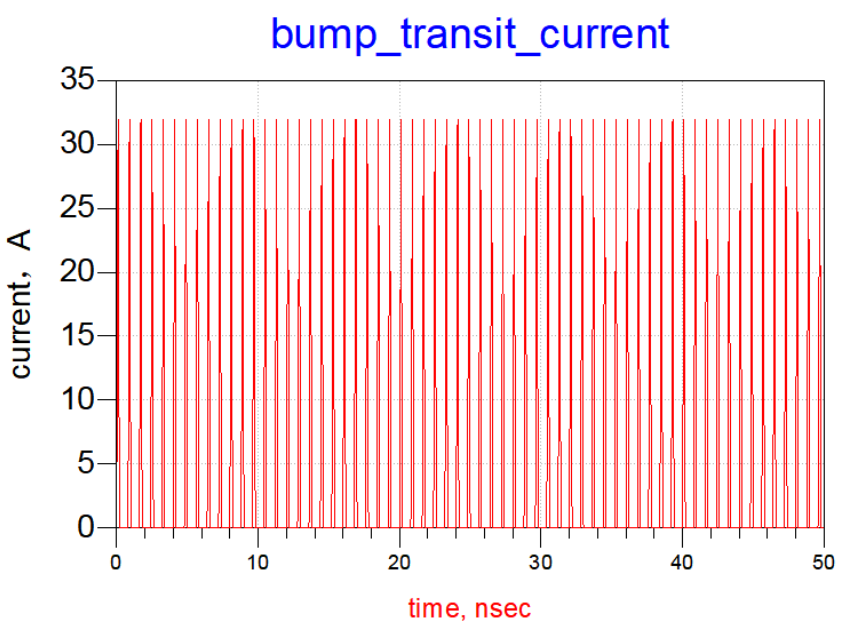

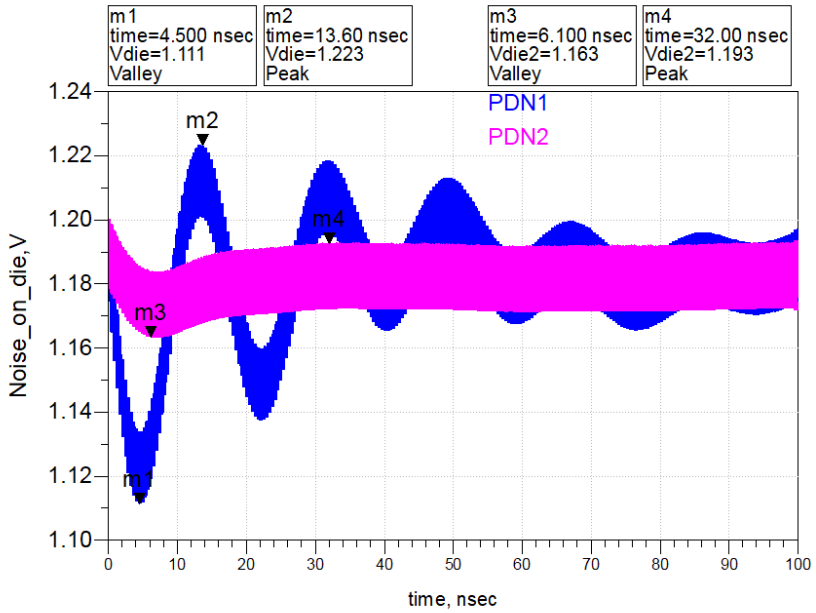

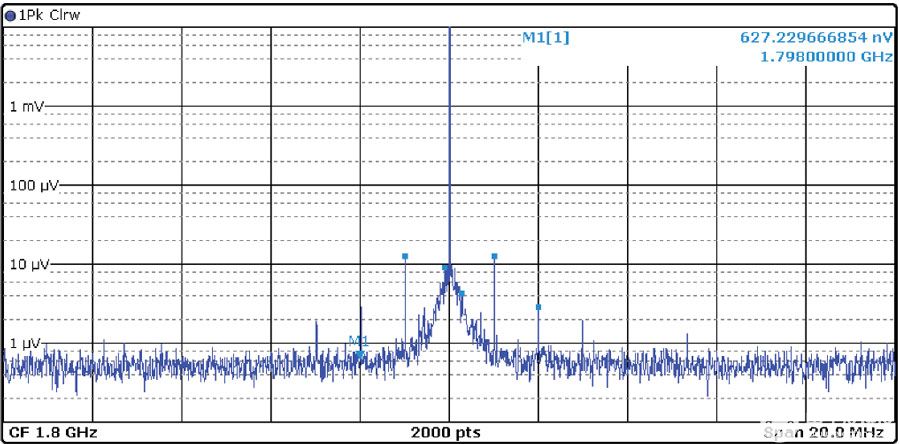

我們用下圖的脈沖電流加載PDN1和PDN2的die端,觀(guān)察噪聲情況:

可以看到兩個(gè)電源系統(tǒng)產(chǎn)生的噪聲差異非常大,PDN1的噪聲更大;

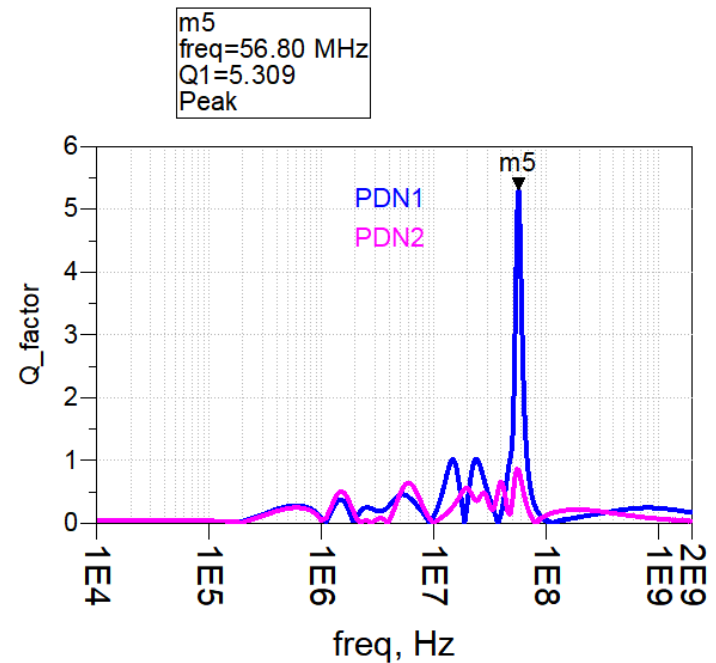

兩個(gè)系統(tǒng)的Q值比較如下:

可以看到 ,PDN1系統(tǒng)的阻抗值不僅大,而且Q值非常高;

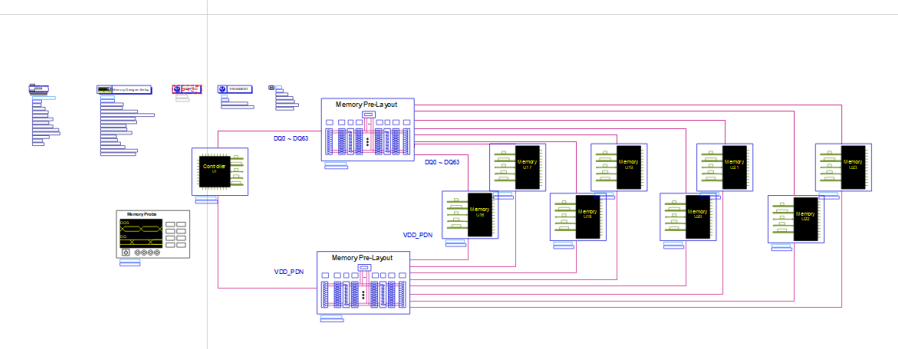

下面我們?cè)趐ower-aware當(dāng)中實(shí)際跑一下信號(hào)、電源的聯(lián)合仿真,來(lái)看一下電源對(duì)信號(hào)的影響,我們運(yùn)行的DDR4為2400Mbps、64bit、8顆mem芯片;

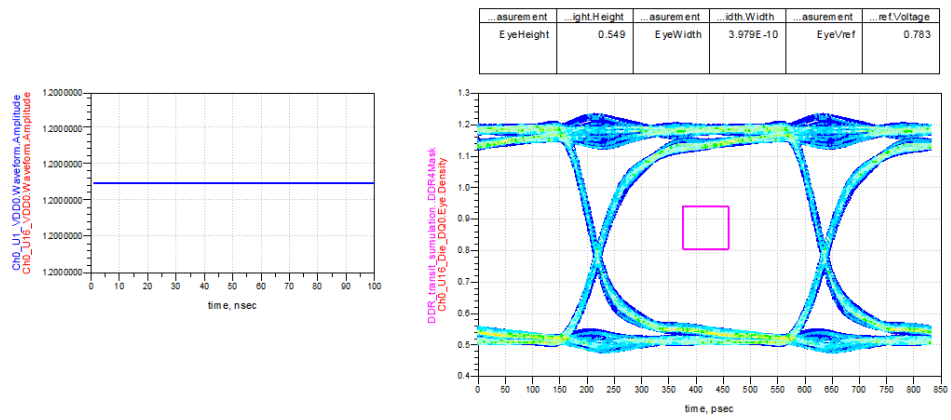

在沒(méi)有考慮電源的影響時(shí),眼圖如下:

可以看到,控制器和DDR芯片的電源是恒定的1.2V,此時(shí)眼圖還算比較干凈,和之前我們仿真的有一個(gè)臨近線(xiàn)串?dāng)_的眼圖基本一致;

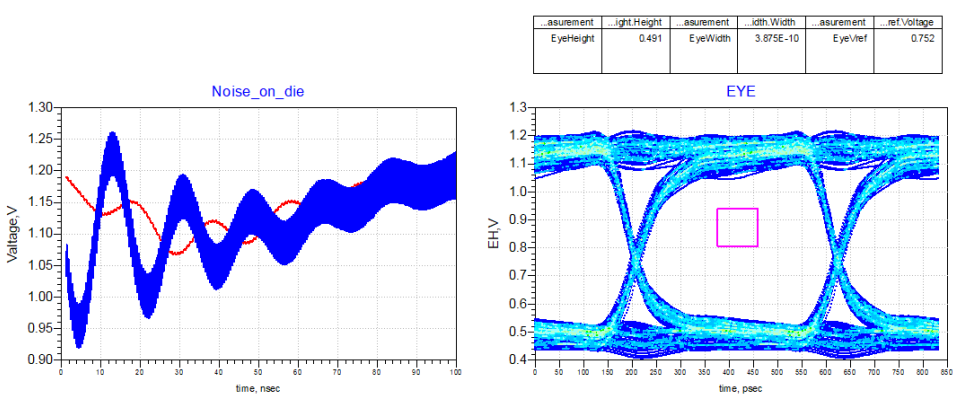

接下來(lái)看一下在PDN1系統(tǒng)下的信號(hào)質(zhì)量:

可以看到,此時(shí),電源已不再是恒定的1.2V,而是有了噪聲,而此時(shí)的DQ眼圖也變差很多;

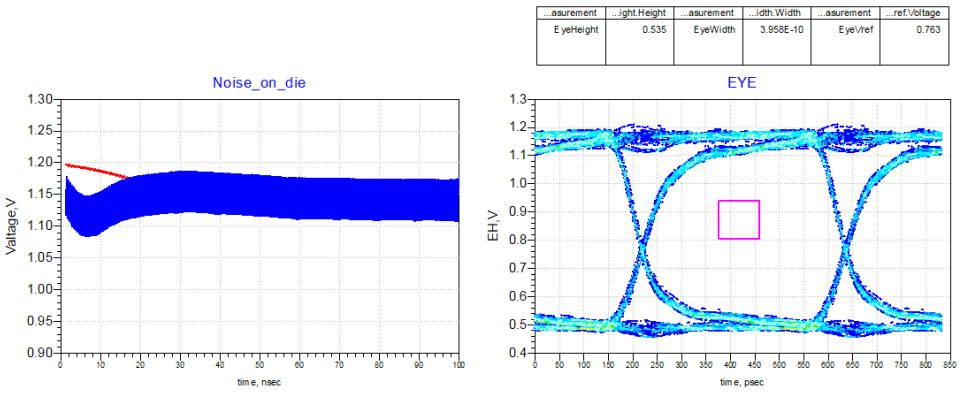

我們?yōu)榱藢?duì)比,再在PDN2上面運(yùn)行,結(jié)果如下:

無(wú)論是電源噪聲,還是眼圖質(zhì)量都是比PDN1要好的,可見(jiàn)電源對(duì)于信號(hào)的影響是非常大的,尤其對(duì)于DDR這么多的并行端口同時(shí)反轉(zhuǎn)時(shí)導(dǎo)致的SSO,而且DDR信號(hào)本身的敏感度也在提升,所以單純的考慮信號(hào)本身的影響已經(jīng)不夠謹(jǐn)慎。

審核編輯:劉清

-

pcb

+關(guān)注

關(guān)注

4326文章

23161瀏覽量

399969 -

DDR4

+關(guān)注

關(guān)注

12文章

322瀏覽量

40960 -

VRM

+關(guān)注

關(guān)注

0文章

30瀏覽量

12720 -

電源仿真

+關(guān)注

關(guān)注

1文章

17瀏覽量

7078 -

DDR5

+關(guān)注

關(guān)注

1文章

430瀏覽量

24209

原文標(biāo)題:DDR4-2400信號(hào)電源聯(lián)合仿真:電源噪聲對(duì)信號(hào)質(zhì)量的影響

文章出處:【微信號(hào):sim_ol,微信公眾號(hào):模擬在線(xiàn)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

改善RF信號(hào)質(zhì)量的電源線(xiàn)噪聲對(duì)策

電源噪聲對(duì)模擬信號(hào)處理器件的影響

多級(jí)運(yùn)放級(jí)聯(lián)如何安排運(yùn)放放大倍數(shù)才能讓信號(hào)質(zhì)量最優(yōu)噪聲小?

為什么FPGA產(chǎn)生高頻信號(hào)影響電源質(zhì)量

改善RF信號(hào)質(zhì)量的電源線(xiàn)噪聲對(duì)策

優(yōu)化信號(hào)鏈的電源系統(tǒng) — 多少電源噪聲可以接受?

電源噪聲的主要來(lái)源

對(duì)電源噪聲的分析與產(chǎn)生的原因

如何量化信號(hào)處理鏈中負(fù)載的電源噪聲靈敏度

信號(hào)鏈的電源管理如何選?

看看電源噪聲對(duì)信號(hào)質(zhì)量的影響

看看電源噪聲對(duì)信號(hào)質(zhì)量的影響

評(píng)論