在芯片驗證中,要想發現bug

需要激勵能夠覆蓋到特定場景

需要一系列的checker能夠發現DUT的錯誤

checker分為兩種類型:

典型的和驗證組件相對比較獨立的checker,這些checker通常與時序相關,例如檢查DUT中的狀態機是否永遠不會進入某個狀態,檢查接口上的vld-rdy時序符合協議。

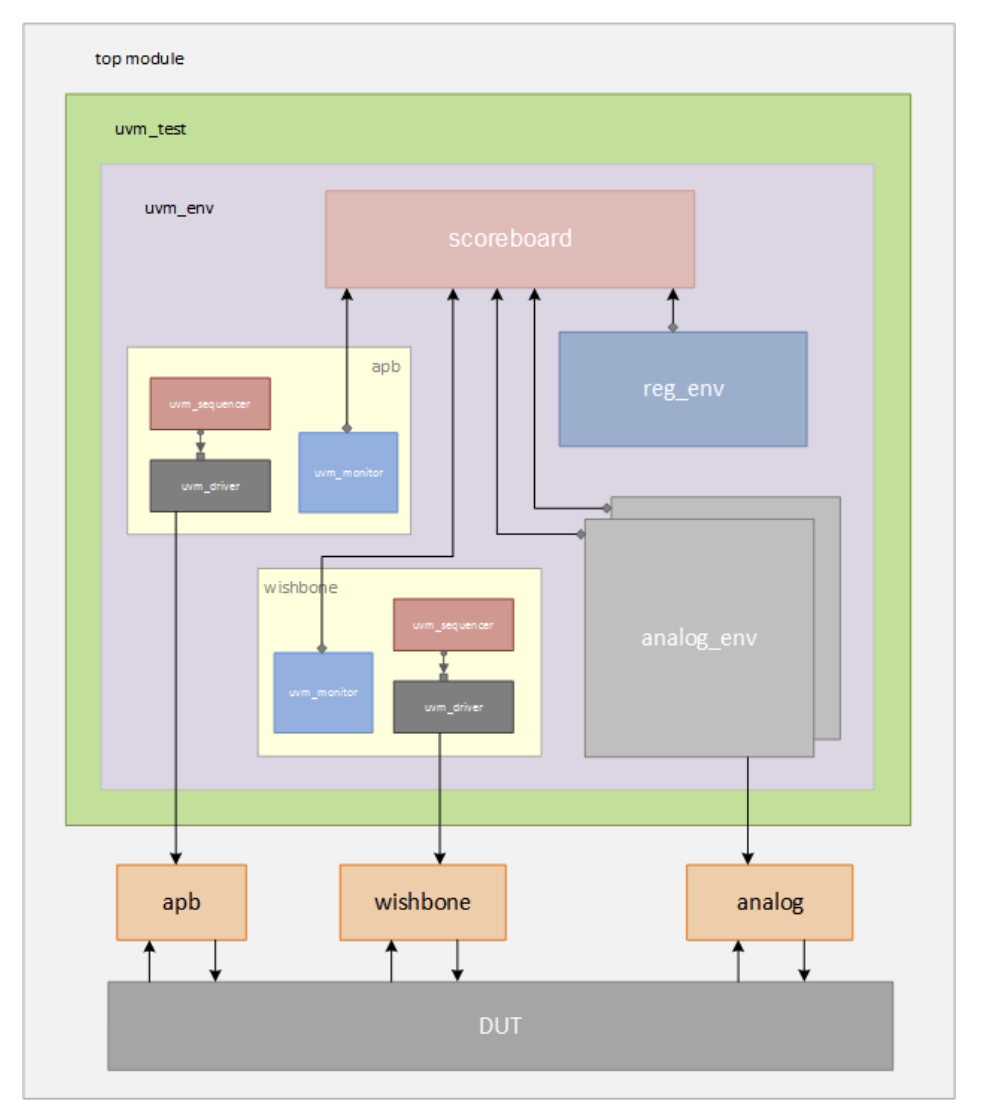

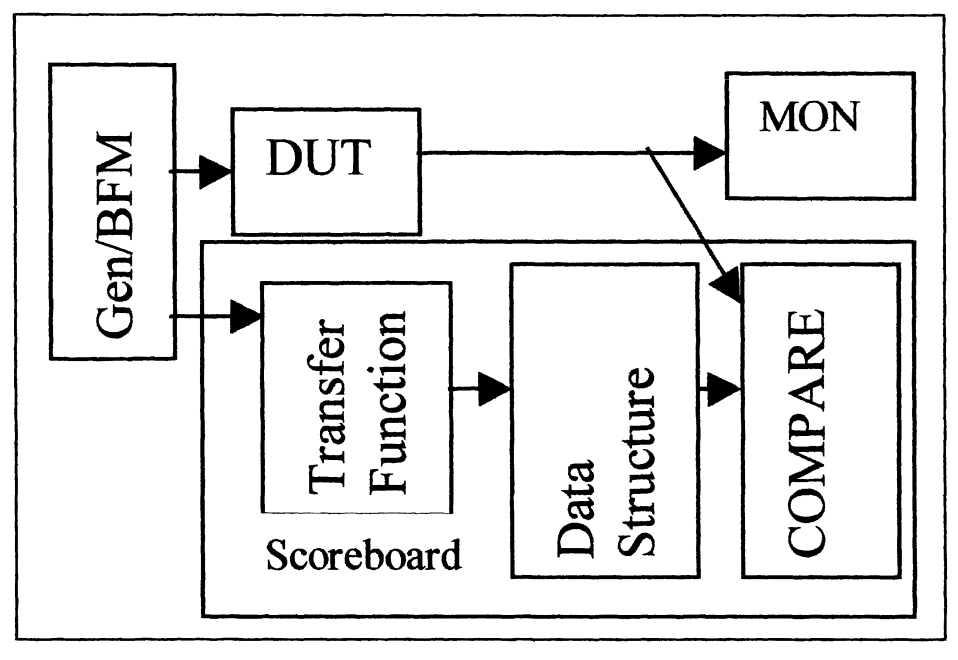

另一種類型的檢查就是數據scoreboard。scoreboard用于檢查系統中數據的完整性。

本文我們先介紹時序的checker,即非scoreboard的checker

時序checker通常用于檢查隨時序變化的行為。時序checker通過時間表達式觸發以對某些條件進行檢查,這個時序表達式可能像時鐘周期一樣簡單,也可能嵌套了很多非常復雜的時間表達式。

時序checker一般是比較白盒的,深入探索DUT中RTL中的一切預期行為:

A事件在條件a下一定發生

B事件一定不會發生

A事件發生后一定會發生B事件

舉個具體例子

在用例結束可以做一個驗證環境和DUT的final值check

檢查fifo不會讀空和寫滿

輸出接口不會違反AMBA協議

理論上,我們可以加入無限多的checker,我們甚至沒法判斷哪些checker是沒有價值的,最終導致checker指數級增長,從而降低仿真器的運行效率。

也許,我們的隊員在會議中提出了很多很多的checker,聽起來都似乎有些道理。但事實上是否真的有價值,還是只是個雞肋般的checker?

審核編輯:劉清

-

RTL

+關注

關注

1文章

385瀏覽量

59954 -

FIFO存儲

+關注

關注

0文章

103瀏覽量

6037 -

AMBA協議

+關注

關注

0文章

7瀏覽量

6488 -

DUT

+關注

關注

0文章

189瀏覽量

12491

原文標題:芯片驗證中的checker和scoreboard

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

康耐視第三代Checker視覺傳感器Checker3G系列

IC驗證"UVM驗證平臺"組成(三)

數字IC驗證之“典型的UVM平臺結構”(3)連載中...

數字IC驗證之“構成uvm測試平臺的主要組件”(4)連載中...

聊聊芯片IC驗證中的風險

淺談IC設計驗證中的打包思想

康耐視新型Checker 4G系列視覺傳感器

基于OVM驗證平臺的IP芯片驗證

什么是UVM environment?

芯片驗證中的checker和scoreboard介紹

芯片驗證中的checker和scoreboard介紹

評論