顧名思義,模數轉換器(ADC)驅動器是專門設計用于與ADC配合使用的專用放大器,包括逐次逼近、流水線和基于Δ-Σ的架構。這些專用放大器是使ADC能夠全性能工作的關鍵電路元件,將在下一節(jié)中探討。隨著傳感器在各種終端市場中變得越來越豐富,對模擬信號調理(包括ADC)的需求持續(xù)增長。這些終端市場包括:

醫(yī)療

消費者

汽車

對于ADC,市場趨勢是更高分辨率和更高速的器件,因為此類解決方案的成本變得更加實惠。

了解 ADC 輸入

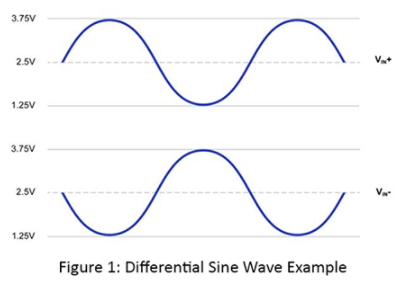

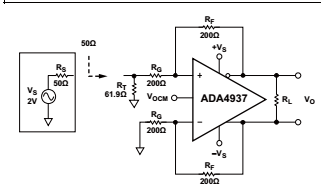

在討論ADC驅動器所需的技術功能之前,需要簡要概述當今ADC的輸入架構。差分信號可以定義為兩個節(jié)點,它們在一個固定點(共模電平)周圍具有相等但相反的信號。兩個信號節(jié)點通常稱為正負(同相和反相),如圖1所示。

在上例中,滿量程輸入電壓峰峰值差分為5V,每個橋臂峰峰值擺動2.5V。本例中的共模電平為2.5V。當今大多數高性能ADC都采用差分輸入架構,因為它提供了卓越的性能(相對于單端輸入)。這些性能優(yōu)勢包括能夠抑制共模噪聲和共模干擾信號,以及動態(tài)范圍增加6 dB(或2倍)。

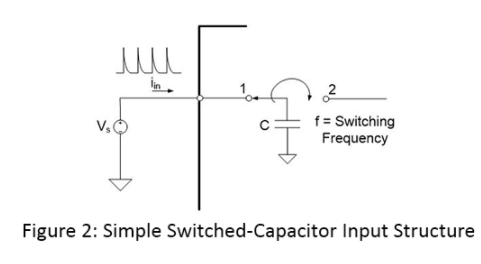

ADC可能會給系統設計人員帶來特別困難的挑戰(zhàn),因為ADC提供了必須在系統級考慮的各種不同輸入采樣架構。出于本討論的目的,重點將放在使用開關電容結構完成輸入采樣的ADC上。在最基本的形式中,這種輸入結構由一個相對較小的電容和一個模擬開關組成,如下圖2所示。

當開關配置在位置1時,采樣電容充電至采樣節(jié)點的電壓,在本例中為VS。然后將開關翻轉到位置2,然后采樣電容上的累積電荷轉移到采樣電路的其余部分。然后,該過程重新開始。

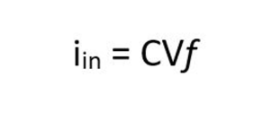

如上所述,無緩沖開關電容輸入可能會導致嚴重的系統級問題。將采樣電容充電至適當電壓所需的電流必須由連接到ADC輸入端的外部電路提供。當電容器切換到采樣節(jié)點(圖1中的開關位置2)時,需要大量電流才能開始為電容器充電。該瞬時電流的大小是采樣電容大小、電容開關頻率以及采樣節(jié)點上電壓的函數。該開關電流可以用以下公式描述:

在上面的示例中,C是采樣電容的電容,V是采樣節(jié)點上的電壓(在本例中表示為VS),f是采樣開關打開和關閉的頻率。該開關電流導致采樣節(jié)點上出現高電流尖峰,如圖2所示。

在設計A/D轉換器前面的模擬電路時,必須考慮該開關電流的影響。當該電流通過任何電阻時,將發(fā)生壓降,導致A/D轉換器采樣節(jié)點出現電壓誤差。如果輸入節(jié)點在下一個采樣周期之前未完全建立,也可能發(fā)生失真。

解決方案:ADC 驅動器

保持所需的傳感器信號完整性以充分利用這些更高分辨率、更高速的ADC變得非常具有挑戰(zhàn)性。隨著ADC分辨率和速度的提高,傳感器信號的噪聲和失真的影響變得更加明顯。在較高的ADC采樣速度下,必須注意確保輸入信號在采樣事件之前已經穩(wěn)定,并且更高帶寬的信號不會混疊回目標信號帶寬。

為了克服這些信號調理挑戰(zhàn),許多ADC應用需要一個能夠提供足夠建立和抗混疊的ADC驅動器。如上所述,大多數現代ADC都采用差分輸入架構。ADC驅動器的主要功能之一是提供輸入信號的單端至差分轉換。

ADC驅動器的另一個功能是緩沖輸入信號,從而將電路的其余部分與ADC輸入節(jié)點上的電荷注入隔離開來。ADC驅動器提供瞬時電荷,以確保采樣節(jié)點在跟蹤時間內建立,從而最大限度地減少與建立相關的任何失真。

大多數ADC驅動器放大器還提供硬件引腳,使用戶能夠對共模電壓進行電平轉換。該特性非常適合確保產生的差分信號以ADC的輸入電壓范圍為中心,從而最大化動態(tài)范圍。

最后,與大多數放大器元件類似,ADC驅動器可以提供輸入信號的放大以及有源濾波。應該注意的是,大多數ADC驅動器的額定增益相對較低,通常增益僅為1或2 V/V。通過保持放大器的閉環(huán)增益較低,環(huán)路增益最大化,從而獲得最低失真。例如,如果放大器的開環(huán)增益為100 dB,而閉環(huán)增益配置為200或46 dB,則只有54 dB的開環(huán)增益裕量來確保線性度,或大約是500分之一。因此,通常有一個單獨的增益級位于信號源附近。

為了充分利用數據轉換器,ADC驅動器必須優(yōu)化性能,同時為源信號增加可忽略不計的失真、噪聲和建立時間誤差。MCP6D11差分驅動器專為最大限度地提高高速ADC的性能而設計,例如MCP33131,這是一款16位、1MSPS SAR ADC。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13629瀏覽量

214211 -

驅動器

+關注

關注

53文章

8271瀏覽量

147061 -

adc

+關注

關注

99文章

6533瀏覽量

545753

發(fā)布評論請先 登錄

相關推薦

3位半和4位半、單片ADC,帶有LED驅動器和μC接口

AD8275 ADC驅動器,具有電平轉換功能,可簡化信號調理

ADC驅動器或差分放大器設計指南

MAX2055應用電路(差分模數轉換器(ADC)驅動器/放大

德州儀器(TI)推出全差動模數轉換器(ADC)驅動器

低功耗差分ADC驅動器數據手冊

為何要組合使用低通濾波器和模數轉換器驅動器?

ADI-高速差分ADC驅動器設計指南

OPAx625高帶寬、高精度、模數轉換器(ADC)驅動器數據表

OPA2626高速、高精度、低失真、16位和18位模數轉換器(ADC)驅動器數據表

了解模數(ADC)驅動器的功能

了解模數(ADC)驅動器的功能

評論