當調(diào)制方式為16-AQM,64-QAM和256-QAM時需要做位交織,交織的目的是將突發(fā)的錯誤分散開來,把一個較長的突發(fā)差錯離散成隨機差錯,再用隨機差錯的編碼(FEC)等信道編碼技術(shù)消除隨機差錯,提高通信的可靠性。交織的越深,抗突發(fā)錯誤的能力也越強。位交織的本質(zhì)是做矩陣的轉(zhuǎn)置運算,需要轉(zhuǎn)置的數(shù)據(jù)包括信息位和校驗位,在交織的過程中分兩步完成,步為檢驗位交織,第二步為列旋轉(zhuǎn)交織。

1.QAM調(diào)制方式介紹

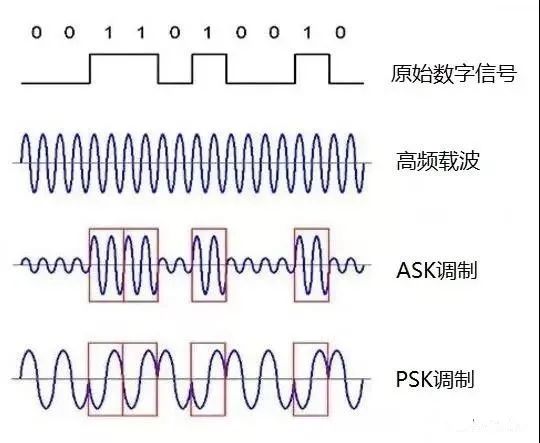

QAM正交振幅調(diào)制,其幅度和相位同時變化,屬于非恒包絡(luò)二維調(diào)制。它把2ASK和2PSK兩種調(diào)制結(jié)合起來,使得帶寬得到雙倍擴展。ASK和PSK調(diào)制方式如下圖所示:

QAM調(diào)制技術(shù)用兩路獨立的基帶信號對頻率相同、相位正交的兩個載波進行調(diào)幅,并將已調(diào)信號加在一起進行傳輸。nQAM代表n個狀態(tài)的正交調(diào)幅,一般有二進制(4QAM)、四進制(16QAM)、八進制(64QAM)、十六進制(256QAM)。得到多進制的QAM信號,需要將二進制信號轉(zhuǎn)換為m電平的多進制信號,然后進行正交調(diào)制,相加輸出。

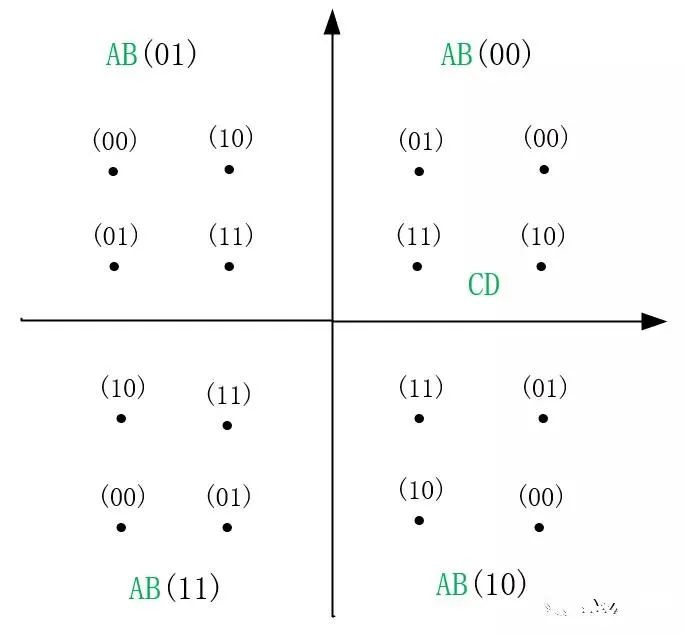

通信系統(tǒng)中通常把信號矢量端點的分布圖成為星座圖,同眼圖相比,星座圖可以看成數(shù)字信號的一個二維眼圖陣列,屏幕上的圖形對應(yīng)著幅度和相位,通過星座圖,可以發(fā)現(xiàn)諸如幅度噪聲,相位噪聲,相位誤差等調(diào)制問題,采用格雷碼編碼技術(shù),16QAM星座圖編碼映射關(guān)系如下圖所示:

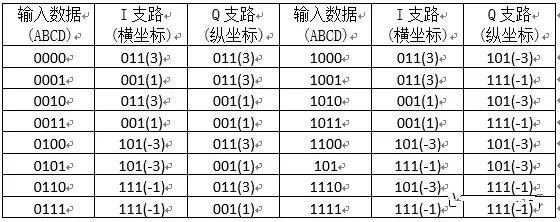

橫縱、坐標的取值均有4種,分別為±1、±3,每種坐標需要3bit二進制來表示,差分編碼后輸入的符號與QAM調(diào)制系統(tǒng)中的I、Q之路幅值映射關(guān)系如下表所示:

2. 檢驗位交織

檢驗位進行交織的時候,信息為的數(shù)據(jù)需要保持不變,檢驗位交織需要滿足以下方程:

根據(jù)校驗位交織地址生成公式可知,交織前的矩陣為Qldpc*360,即依次向數(shù)據(jù)每行寫入360個數(shù),第361個數(shù)為第二行列數(shù),依次類推。存放Rom地址如圖所示:

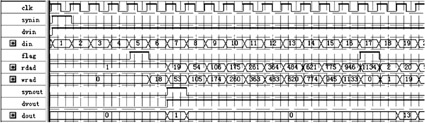

交織的本質(zhì)是行進列出,即取數(shù)據(jù)依次如下地址取數(shù)據(jù),重新生成新的一組向量Matlab 中,重新產(chǎn)生讀數(shù)據(jù)的地址索引,即可實現(xiàn)矩陣的轉(zhuǎn)置,使用兩個for循環(huán)在硬件平臺上實現(xiàn)上述操作則需要兩個計數(shù)器來實現(xiàn)地址的累加,實現(xiàn)的波形如圖所示3. 列旋轉(zhuǎn)交織

校驗位交織輸出ui按列順序依次寫入列旋轉(zhuǎn)交織器,然后按行依次讀出,完成列旋轉(zhuǎn)交織,每列寫入的起始位置由tc決定,整個旋轉(zhuǎn)交織見下圖列旋轉(zhuǎn)交織用公式表示如下:

輸入為ui,0≤i≤Nldpc,寫入交織器的ci列,ri行,其中列旋轉(zhuǎn)交織器的輸出為ui,0≤i≤Nldpc,從交織器的ri行,ci列讀出,其中列旋轉(zhuǎn)交織測參數(shù)為Nldpc = 16200,Rows Nr =2025,Columns Nc = 8,列旋轉(zhuǎn)參數(shù)tc見下表交織之前的數(shù)據(jù)地址為

對于列旋轉(zhuǎn)交織,每列Tc的值都是確定的,因此可以按照一定規(guī)律求出每列的地址,如下圖所示,以第四列Tc為7為例,即數(shù)據(jù)整體往后移7行,7行的數(shù)據(jù),移到前面的幾行。求出新的地址后,依次將行地址數(shù)據(jù)讀出即完成位旋轉(zhuǎn)交織。

在計算列旋轉(zhuǎn)交織的時候需要考慮固定延遲Tc,在matlab中,可以這樣得到交織的結(jié)果相比奇偶校驗,列旋轉(zhuǎn)交織多了Tc的延遲,需要在正常產(chǎn)生地址的情況下再進行操作,正常地址產(chǎn)生的操作同奇偶校驗。Tc是21,因此可以定義一個狀態(tài)機來完成此操作,如下:

對照交織之后得到的地址矩陣,在狀態(tài)Row_1讀取行的地址,前三列Tc =0,不做任何操作,正常讀出轉(zhuǎn)置后的地址即可;第四列需要加上2025-1,第五列加2025-7,后面的三列也按照Tc的延遲進行操作。Row_2代表第二行,依次類推,讀完21行之后,相同的列對應(yīng)的操作都一樣,都在Row_last中完成Gen_end表示交織完成,跳轉(zhuǎn)到狀態(tài)0,等待下一幀的操作。

從以往的學習經(jīng)驗來看,想從新手進階為FPGA高手、行業(yè)資深FPGA開發(fā)工程師,您不僅要學習基礎(chǔ)的數(shù)字電路知識,掌握基礎(chǔ)電路如組合邏輯、時序邏輯電路的原理與實現(xiàn)方法。編程語言方面,學會使用硬件描述語言Verilog或者VHDL,并選擇相應(yīng)FPGA開發(fā)平臺設(shè)計軟件(Quartus或者ISE),找相關(guān)的實例“抄寫”代碼,逐漸熟悉FPGA硬件語言編程及編譯器使用。經(jīng)過前面一段的鋪墊學習,然后你就可以自行嘗試設(shè)計數(shù)字電路了。在做項目的時候,根據(jù)提供時序圖使用HDL語言去完成它,這時候你就可以購買FPGA開發(fā)板去完成項目后續(xù)設(shè)計、驗證和sim仿真設(shè)計了。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1630文章

21797瀏覽量

606012 -

仿真

+關(guān)注

關(guān)注

50文章

4124瀏覽量

133993 -

調(diào)制方式

+關(guān)注

關(guān)注

0文章

18瀏覽量

10363 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1629瀏覽量

80822 -

QAM

+關(guān)注

關(guān)注

0文章

78瀏覽量

30472

發(fā)布評論請先 登錄

相關(guān)推薦

為什么要進行交織處理?什么是分組交織?什么是卷積交織?

求一個Verilog HDL ***數(shù)據(jù)交織/解交織器的代碼

基于FPGA的交織編碼技術(shù)研究及實現(xiàn)

[Mill]無線通信連載——交織

地面數(shù)字視頻廣播中內(nèi)交織器與解內(nèi)交織器設(shè)計

基于FPGA的改進型分組交織器的設(shè)計與實現(xiàn)

可變參數(shù)交織編碼器的FPGA實現(xiàn)

TURBO碼實時交織器的FPGA實現(xiàn)

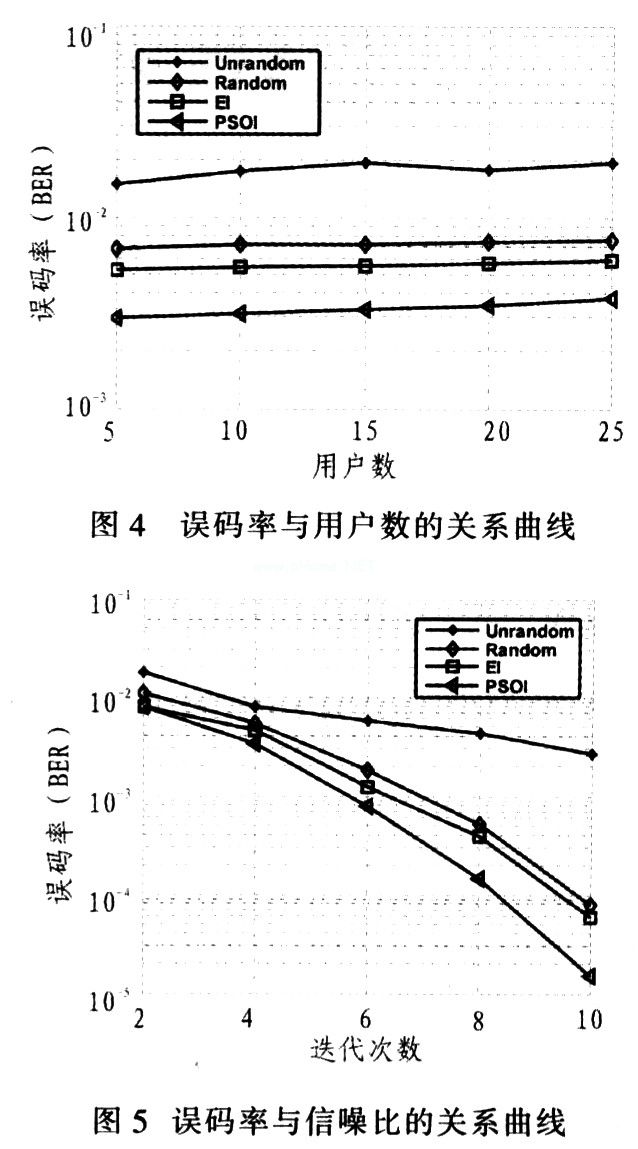

IDMA通信系統(tǒng)中的粒子群交織算法

一種交織器和解交織器的FPGA電路實現(xiàn)

利用FPGA技術(shù)實現(xiàn)數(shù)字通信中的交織器和解交織器

基于FPGA的改進型分組交織器的設(shè)計與實現(xiàn)

IDMA通信系統(tǒng)中的粒子群交織算法

FPGA如何使用RAM分區(qū)循環(huán)移位法實現(xiàn)解交織器

FPGA無限通信技巧—位交織

FPGA無限通信技巧—位交織

FPGA無限通信技巧—位交織

評論