多年來,虛擬現(xiàn)實 (VR) 和增強現(xiàn)實 (AR) 與游戲和娛樂應(yīng)用密切相關(guān)。如今,VR/AR 及其組合版本混合現(xiàn)實 (MR) 的應(yīng)用已擴展到其他領(lǐng)域,如醫(yī)療保健、軍事、教育、制造、零售、營銷和廣告。下一代 VR 顯示器面臨哪些挑戰(zhàn)?是什么讓 MIPI 接口最適合 VR/AR/MR 應(yīng)用?Mixel, Inc. 如何將不同的 MIPI PHY 產(chǎn)品組合成獨特、差異化、靈活的解決方案?這些問題的答案將在整篇文章中揭曉。

為了支持 VR 的多樣化應(yīng)用和用例,并滿足對 PC、手機和便攜式設(shè)備驅(qū)動 VR 顯示器不斷增長的需求,與當(dāng)前一代相比,下一代 VR 顯示器在許多方面都取得了進步。

第一代 VR 顯示器支持 1k x 1k 分辨率,這不足以在近視場顯示高分辨率圖像。下一代 VR 顯示器的目標(biāo)是支持約 1000 像素每英寸 (PPI) 的顯示分辨率,以實現(xiàn) 2k x 2k 的最低顯示分辨率,一直到 4k x 4k,提供最佳用戶體驗。

下一代 VR 顯示器的另一個目標(biāo)是響應(yīng)能力,即 LCD 晶體必須在用戶觀看之前穩(wěn)定下來,以便在近場視野中呈現(xiàn)清晰的 LCD 圖像。實現(xiàn)這一點的技術(shù)之一是加載像素,讓它們有一些時間穩(wěn)定下來,然后閃爍背光,這樣用戶只能在像素穩(wěn)定后才能看到它們。為實現(xiàn)這一點,顯示面板必須以更快的速度更新,這意味著更高的帶寬要求。

降低視頻延遲是另一項挑戰(zhàn)。高視頻延遲會導(dǎo)致視頻內(nèi)容滯后,從而導(dǎo)致視頻和音頻內(nèi)容不同步。這種影響會導(dǎo)致暈車問題。下一代 VR 顯示 IC 應(yīng)針對最低延遲進行優(yōu)化,這需要部署低延遲接口。

如果在乎功耗的增加,就無法增加帶寬以支持更高分辨率、更高刷新率和更快的響應(yīng)速度。通常部署在沉浸式頭戴式顯示器中,VR 設(shè)備應(yīng)該消耗最小的功率,從而產(chǎn)生的熱量可以忽略不計,以提供方便的用戶體驗。在顯示器由手機或其他便攜式設(shè)備驅(qū)動的應(yīng)用中,最小化功耗仍然是關(guān)鍵要求。雖然所有標(biāo)準(zhǔn)化接口都在競相實現(xiàn)最高帶寬,但 MIPI 規(guī)范是從頭開始開發(fā)的,以支持高帶寬、低延遲應(yīng)用程序,同時最大限度地降低功耗。

XR 系統(tǒng)中的 MIPI

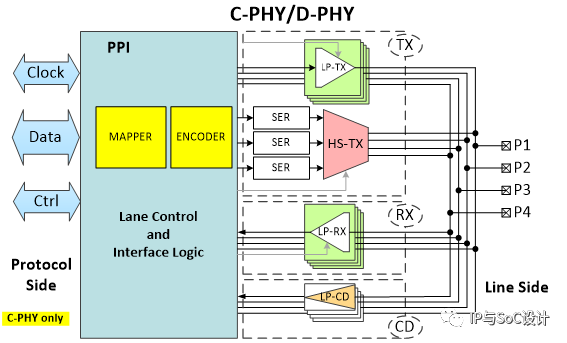

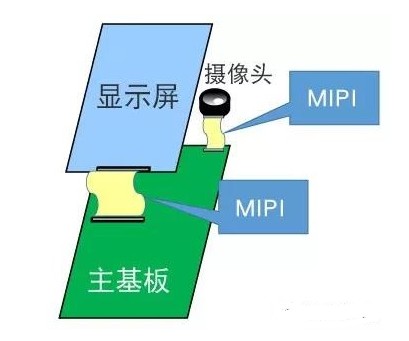

術(shù)語 XR 通常用于指代任何現(xiàn)實技術(shù) VR、AR 和 MR 或其任意組合。現(xiàn)在,讓我們快速瀏覽一下 MIPI C-PHYSM 和 D-PHYSM 接口,解釋為什么它們是 XR 應(yīng)用的最佳選擇,以及 Mixel 如何以最小的面積和功率開銷在單個 PHY 中結(jié)合這兩種接口的特性。

MIPI D-PHY 是一種簡單的源同步 PHY,它使用一個時鐘通道和不同數(shù)量的數(shù)據(jù)通道。它自 2009 年以來一直存在,并廣泛部署在 CSI-2SM 和 DSISM 應(yīng)用程序中。另一方面,C-PHY 是 MIPI 家族的新成員,也是更復(fù)雜的 PHY。C-PHY 在三個信號上運行,一個三重奏,時鐘嵌入到數(shù)據(jù)中,因此不需要單獨的時鐘通道。單通道 D-PHY 1.2 配置需要四個引腳,兩個引腳用于時鐘通道,兩個引腳用于數(shù)據(jù)通道,實現(xiàn)高達 2.5 Gbps 的數(shù)據(jù)速率。單三重 C-PHY 1.1 配置僅需要三個引腳,可實現(xiàn)高達 2.5 Gsps 的符號率,即 5.7 Gbps。得益于 MIPI C-PHY 巧妙而高效的映射和編碼技術(shù),數(shù)據(jù)速率效率提高了 2.28 倍。

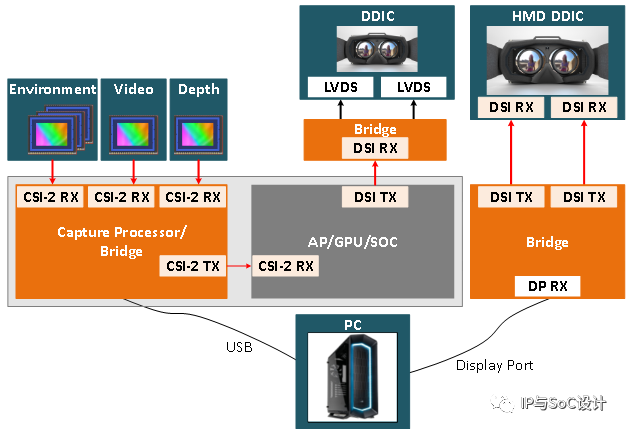

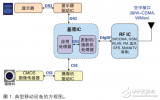

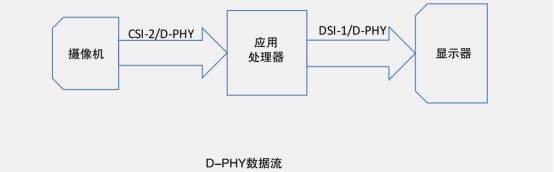

為了解釋 MIPI D-PHY 和 MIPI C-PHY 在 VR、AR 和 MR 系統(tǒng)中的不同用例,讓我們看一下圖 1。

Figure 1: MIPI Use Cases in XR System

MIPI CSI-2 接口通常用于 AR 應(yīng)用,作為一側(cè)不同類型傳感器(環(huán)境、視頻捕捉、深度捕捉)與另一側(cè)捕捉處理器或橋接芯片之間的接口。DSI 接口通常用于 VR 應(yīng)用程序,其中 GPU 處理器將驅(qū)動顯示面板。捕獲處理器和主機處理器之間的接口可以部署另一對 MIPI TX/RX 低延遲 PHY。在系留應(yīng)用中,處理器(手機、臺式機或筆記本電腦)使用非 MIPI 接口,可以部署橋接芯片將數(shù)據(jù)轉(zhuǎn)換為 MIPI 形式。DSI 和 CSI-2 都是 MIPI 協(xié)議,可以通過 MIPI C-PHY 和/或 MIPI D-PHY 物理層發(fā)送數(shù)據(jù)。

Mixel 的雙模 C-PHY/D-PHY

Mixel 的雙模式 C-PHY/D-PHY 實現(xiàn)將兩者組合成一個組合 PHY,同時共享相同的管腳盤。D-PHY 鏈路可以作為 1 到 4 條通道運行,每條通道以 2.5Gbps 運行,而 C-PHY 鏈路可以作為 1 到 3 條通道運行,每條通道以高達 2.5Gbsps 的速度運行,相當(dāng)于 5.7Gbps。Mixel Combo PHY 在 D-PHY 模式下支持高達 10 Gbps 的聚合數(shù)據(jù)速率,在 C-PHY 模式下支持高達 17.1Gbps 的聚合數(shù)據(jù)速率。

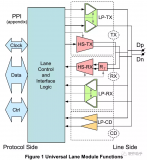

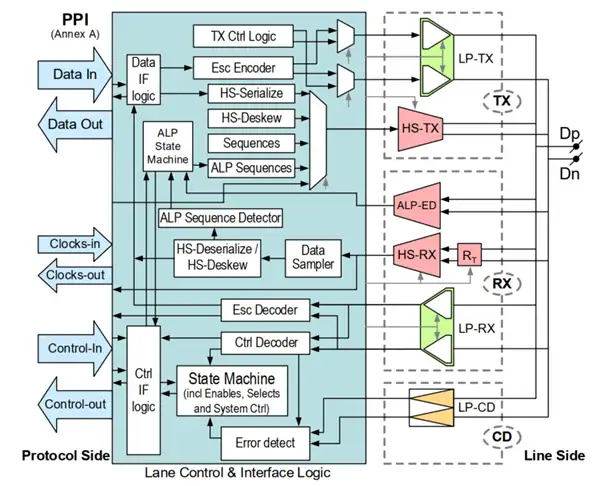

Combo PHY IP 不僅共享串行接口引腳,而且 Mixel 的實現(xiàn)還為 MIPI C-PHY 重用了所有 MIPI D-PHY 功能塊,從而最大限度地減少了管芯面積和泄漏功率。下面的圖 2 顯示了 Mixel MIPI C-PHY/D-PHY Combo TX 的框圖,用于 DSI 主機應(yīng)用,旨在驅(qū)動最新的 VR 顯示器。

Figure 2: Mixel MIPI C-PHY/D-PHY Combo TX Block Diagram

Mixel Combo C-PHY/D-PHY 支持 D-PHY 和 C-PHY 模式下的通道交換和極性更改功能。有了這樣的功能,系統(tǒng)集成和 PCB 布線就會更加順暢,因為通道/三重奏可以配置為多種組合。

它還配備了內(nèi)置自測試 (BIST) 引擎,可以跨多個抽象層(IC、PCB 等)測試 PHY。BIST 引擎能夠在不同的 MIPI 操作模式下測試 Combo PHY,并提高可觀察性和可控性。實施了各種測試場景以支持生產(chǎn)和特性測試。

Synaptics 的用例

部署 Mixel C-PHY/D-PHY 組合 TX 解決方案,領(lǐng)先的高科技人機界面解決方案提供商 Synaptics Incorporated 開發(fā)了世界上第一款同時使用 MIPI C-PHY 和 D-PHY 的顯示應(yīng)用 IC。VXR7200 VR Bridge 是一種連接解決方案,適用于部署完整 VESA DP1.4 帶寬的系留 USB Type-C 電纜。它針對分辨率高達 3k x 3k @ 120Hz 的 VR、AR 和 MR 雙顯示器耳機進行了優(yōu)化,具有 DSC 壓縮功能,可實現(xiàn)一流的 HMD 用戶體驗。Synaptics R63455 VR 顯示驅(qū)動器 IC 是一款配套芯片,可使用特殊的 VR 顯示時序模式驅(qū)動顯示器。

VXR7200 VR 橋芯片管理橋的 DisplayPort 和 MIPI 端。它通過顯示端口接口與 GPU 處理器通信,以提供顯示要求,如視頻格式(子像素渲染、420、444、8 位、10 位)、壓縮設(shè)置和幀時序分配。另一方面,Mixel MIPI C-PHY/D-PHY 和 DSI-2 控制器用于與顯示驅(qū)動器 IC (DDIC) 通信以配置視頻格式、壓縮設(shè)置、面板掃描時間、建立時間、背光閃爍時間和 局部調(diào)光設(shè)置。

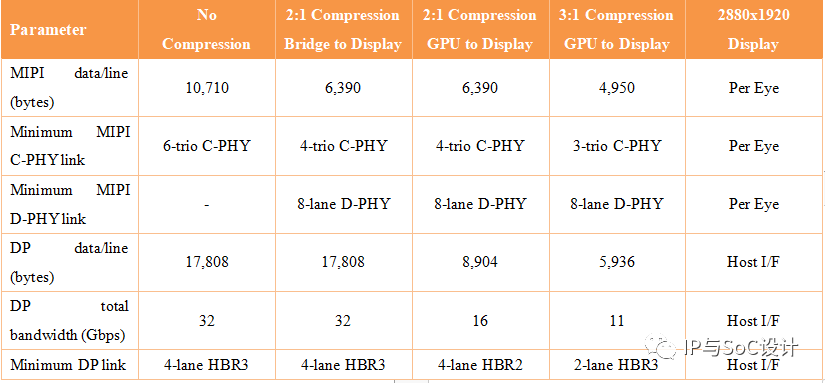

通過在每個鏈路上集成兩個 Mixel Combo C-PHY/D-PHY 實例和 DSI-2 控制器,橋接芯片 MIPI 接口擴展為支持八個 MIPI D-PHY 數(shù)據(jù)通道,與六個 MIPI C-PHY 三重奏共享相同的芯片引腳 每只眼睛。橋接 MIPI 接口具有高度可配置性,可支持不同代的顯示面板、多種分辨率和帶寬選項以及不同的壓縮設(shè)置。下面的表 1 解釋了為什么需要雙模 C-PHY/D-PHY 接口來支持各種應(yīng)用和配置。

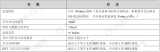

Table 1: Bridge Chip Data Rates Supported in Different Configurations

上表顯示了每只眼睛以 90Hz 顯示器驅(qū)動 2880x1920 顯示器的不同配置示例。在沒有壓縮的情況下,DP 鏈路必須配置為支持 32Gbps 帶寬的 4 通道 HBR3,這必須與 MIPI 接口側(cè)的 6 個 C-PHY 三重奏相匹配,以驅(qū)動 2880x1920 每眼顯示器。D-PHY 不能用于此,因為它支持的最大帶寬低于此類配置中的系統(tǒng)要求。需要 C-PHY 支持才能支持此重要功能。

當(dāng)啟用橋接顯示或 GPU 顯示壓縮時,可以使用 D-PHY 通道或 C-PHY 三重奏的不同配置,以優(yōu)化功耗提供所需的 MIPI 帶寬。

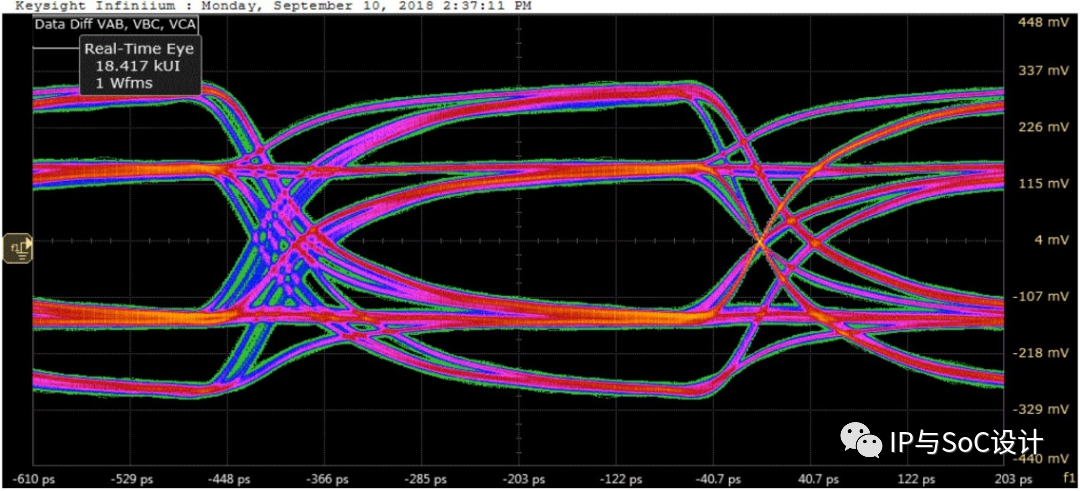

硅結(jié)果

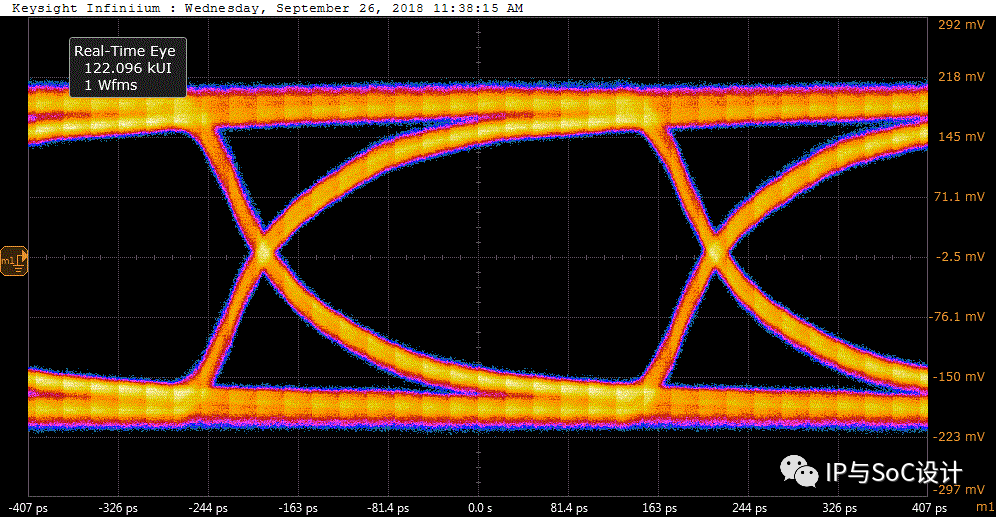

以下兩張快照顯示了集成到 Synaptics VXR7200 VR Bridge IC 中的 Mixel 雙模 C-PHY/D-PHY 的測試結(jié)果。VXR7200 橋接芯片通過 Mixel Combo PHY IP 和 DSI-2 控制器首次在硅片上取得成功,現(xiàn)已投入生產(chǎn),現(xiàn)已上市。

Figure 3: Mixel MIPI C-PHY Eye Diagram at 2.5Gsps

Figure 4: Mixel MIPI D-PHY Eye Diagram at 2.5Gbps

總而言之,VR/AR/MR 應(yīng)用在不同領(lǐng)域不斷發(fā)展壯大,對以最低功耗、延遲和 EMI 支持更高帶寬的需求不斷增加。MIPI 接口屬性非常適合 XR 應(yīng)用程序要求。Mixel 雙模 C-PHY/D-PHY IP 產(chǎn)品是適用于系統(tǒng)啟動和應(yīng)用用例的獨特、靈活和通用的解決方案。Mixel C-PHY/D-PHY 產(chǎn)品支持的多鏈路配置使其成為所有 XR 顯示器和傳感器應(yīng)用的理想選擇。

審核編輯:湯梓紅

-

顯示器

+關(guān)注

關(guān)注

21文章

5010瀏覽量

140405 -

虛擬現(xiàn)實

+關(guān)注

關(guān)注

15文章

2290瀏覽量

96145 -

PHY

+關(guān)注

關(guān)注

2文章

305瀏覽量

51862 -

MIPI

+關(guān)注

關(guān)注

11文章

312瀏覽量

48765 -

vr

+關(guān)注

關(guān)注

34文章

9645瀏覽量

150784

原文標(biāo)題:雙模 C-PHY / D-PHY:支持下一代 VR 顯示器

文章出處:【微信號:IP與SoC設(shè)計,微信公眾號:IP與SoC設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

C-PHY與MIPI D-PHYSM和M-PHY相比如何?

MIPI D-PHY的不同通道

D-PHY接口、C-PHY接口和M-PHY接口的基本概念

是德科技新款 MIPI? D-PHYSM 和 C-PHYSM 測試解決方案 加速移動技術(shù)和物聯(lián)網(wǎng)技術(shù)開發(fā)

MIPI D-PHY物理層、CSI 和 DSI 協(xié)議層測試的了解及執(zhí)行

MIPI C-PHY差分傳輸接口的靜噪特點及相應(yīng)對策

對于MIPI系列之“D-PHY”的性能分析和介紹以及應(yīng)用

MIPI D-PHY的靜噪措施

MIPI C-Phy PCB空間優(yōu)化設(shè)計

采用TekScope PC進行MIPI D-PHY/ C-PHY解碼的使用方法和步驟

MIPI-D/C PHY的PCB布局布線要求

MIPI D-PHY 物理層自動一致性測試

聚焦MIPI 系列之四:一文盤點D-PHY/C-PHY/M-PHY之架構(gòu)與測試解決方案

雙模C-PHY/D-PHY:支持下一代VR顯示器

雙模C-PHY/D-PHY:支持下一代VR顯示器

評論