跨時鐘域操作包括同步跨時鐘域操作和異步跨時鐘域操作。同步跨時鐘域意味著發送時鐘和接收時鐘是同步的,比如兩個時鐘是同一個MMCM生成的,在這種情況下,這兩個時鐘有明確的相位關系。

所以,同步跨時鐘域操作重要的是做好約束。無論是從快時鐘域到慢時鐘域還是從慢時鐘域到快時鐘域,都可以通過多周期路徑約束實現,同時還要注意時鐘偏移對跨時鐘域路徑時序的影響。

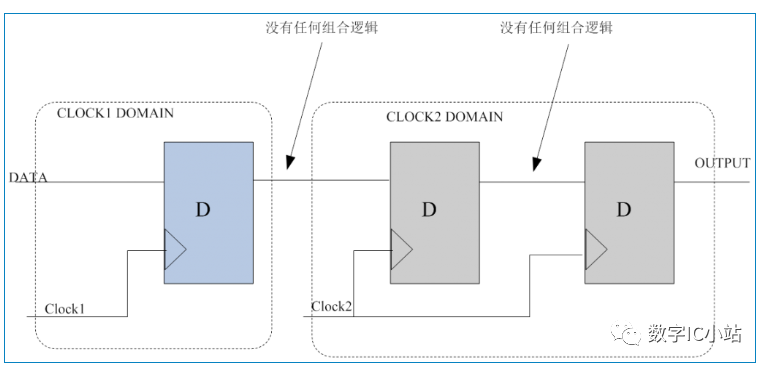

對于異步跨時鐘域操作,由于發送時鐘和接收時鐘是異步的,也就是兩者不存在明確的相位關系,這時既要從硬件電路上保證設計是安全的,又要從約束層面確保數據被穩定接收。

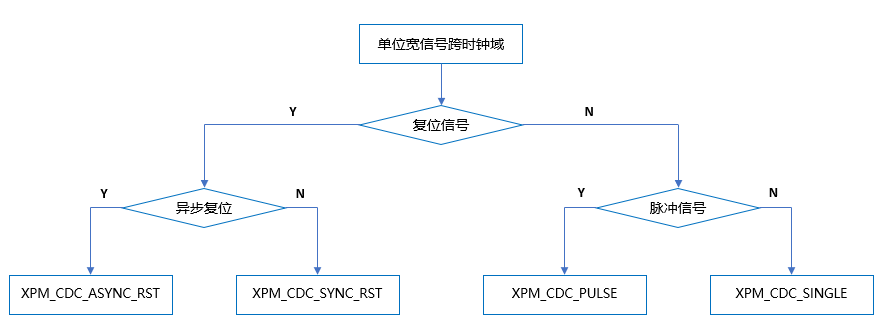

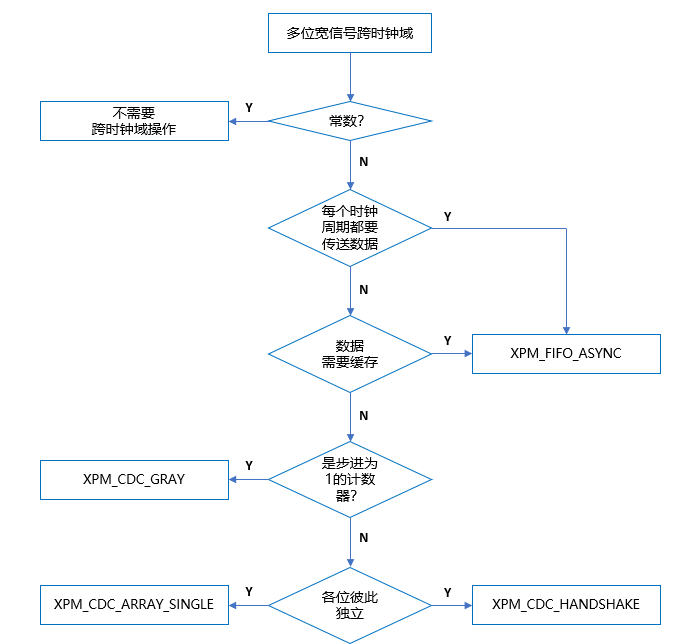

根據數據位寬可分為兩種情形:單位寬信號跨時鐘域和多位寬信號跨時鐘域。此時,可使用XPM_CDC,具體使用哪個模塊,可參考如下兩個流程。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

CDC

+關注

關注

0文章

57瀏覽量

17854 -

XPM

+關注

關注

0文章

12瀏覽量

8694

原文標題:跨時鐘域電路設計(8):總結

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

從電路的角度出發,提出了一種新的SOC跨時鐘域同步電路設計的方法

針對當前SOC內部時鐘越來越復雜、接口越來越多以及亞穩態、漏信號等常見的各種問題,分析了以往的優化方法的優缺點,然后從電路的角度出發,提出了一種新的SOC跨時鐘

關于FPGA中跨時鐘域的問題分析

跨時鐘域問題(CDC,Clock Domain Crossing )是多時鐘設計中的常見現象。在FPGA領域,互動的異步時鐘

發表于 08-19 14:52

?3402次閱讀

跨時鐘域電路設計:多位寬數據通過FIFO跨時鐘域

FIFO是實現多位寬數據的異步跨時鐘域操作的常用方法,相比于握手方式,FIFO一方面允許發送端在每個時鐘周期都發送數據,另一方面還可以對數據進行緩存。需要注意的是對FIFO控制信號的管

跨時鐘域電路設計:單位寬信號如何跨時鐘域

單位寬(Single bit)信號即該信號的位寬為1,通常控制信號居多。對于此類信號,如需跨時鐘域可直接使用xpm_cdc_single,如下圖代碼所示。參數DEST_SYNC_FF決定了級聯觸發器

fpga跨時鐘域通信時,慢時鐘如何讀取快時鐘發送過來的數據?

時,由于時鐘頻率不同,所以可能會產生元件的不穩定情況,導致傳輸數據的錯誤。此時我們需要采取一些特殊的措施,來保證跨時鐘域傳輸的正確性。 FPGA跨

跨時鐘域電路設計總結

跨時鐘域電路設計總結

評論