介紹一下Xilinx公司的新一代Zynq UltraScale+ RFSoC器件,可用于LTE、5G、SDR、衛(wèi)星通信等無(wú)線平臺(tái)。

Zynq UltraScale+RFSoC系列將多頻帶、多模蜂窩無(wú)線電和電纜基礎(chǔ)設(shè)施(DOCSIS)的關(guān)鍵子系統(tǒng)集成到SoC平臺(tái)中,該平臺(tái)包含一個(gè)功能豐富的64位四核Arm Cortex -A53和基于Arm Cortex- R5F的雙核處理系統(tǒng)。

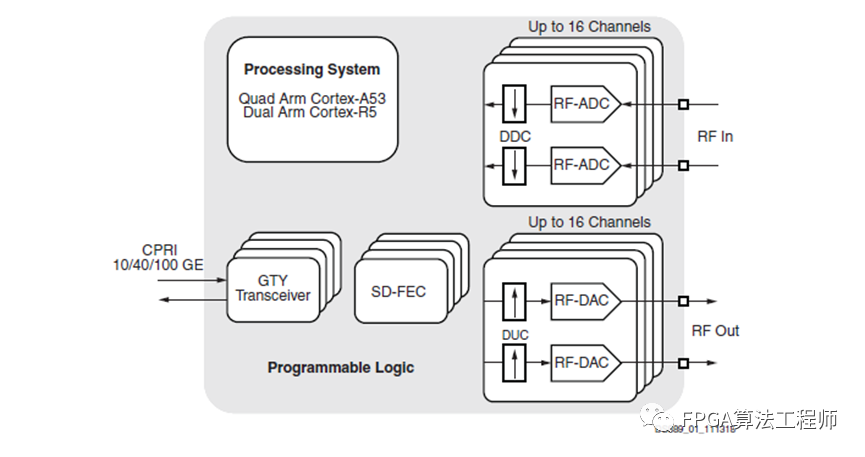

將處理系統(tǒng)與UltraScale架構(gòu)可編程邏輯、RF- ADC、RF- DAC和軟決策FECs相結(jié)合,Zynq UltraScale+ RFSoC家族能夠?qū)崿F(xiàn)完整的軟件定義無(wú)線電(SDR),包括直接射頻采樣數(shù)據(jù)轉(zhuǎn)換器,在單個(gè)、高可編程SoC上實(shí)現(xiàn)CPRI和千兆以太網(wǎng)到射頻。

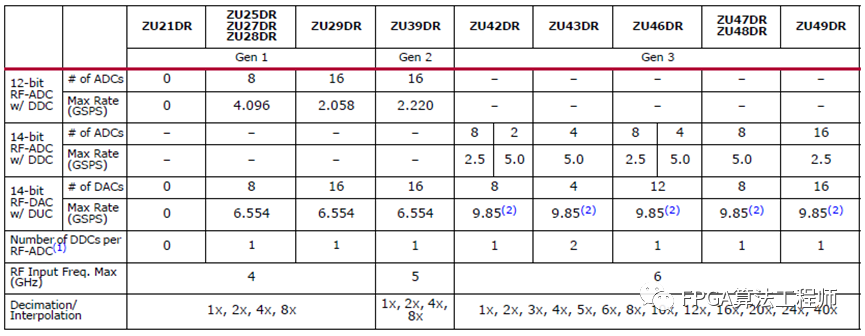

三代ZynqUltraScale+ rfsoc集成了多達(dá)16個(gè)通道的RF - ADC和RF - DAC,均具有優(yōu)良的噪聲譜密度。RF數(shù)據(jù)轉(zhuǎn)換器還包括功率高效的數(shù)字下轉(zhuǎn)換器(DDC)和數(shù)字上轉(zhuǎn)換器(DUC),其中包括可編程插補(bǔ)和抽取、NCO和復(fù)雜混頻器。DDC和DUC也支持雙頻操作。關(guān)鍵特性和采樣率見(jiàn)表1。

表1 射頻數(shù)據(jù)轉(zhuǎn)換器子系統(tǒng)特性

軟判決FEC(SD-FEC)是一種高度靈活的前向糾錯(cuò)引擎,能夠在Turbo解碼模式下運(yùn)行,適用于無(wú)線應(yīng)用,如5G無(wú)線、回程和DOCSIS 3.1電纜調(diào)制解調(diào)器中使用的LTE和LDPC編碼/解碼模式。

Zynq UltraScale+ RFSoC關(guān)鍵組件

圖1Zynq UltraScale+ RFSoC

特性總結(jié)

RF 數(shù)據(jù)轉(zhuǎn)換器字系統(tǒng)概述

大多數(shù)ZynqUltraScale+ RFSOC都包含一個(gè)射頻數(shù)據(jù)轉(zhuǎn)換器子系統(tǒng),其中包含多個(gè)射頻模擬數(shù)字轉(zhuǎn)換器(RF-ADC)和多個(gè)射頻數(shù)字模擬轉(zhuǎn)換器(RF-DAC)。高精度、高速、高效的RF - ADC和RF - DAC可單獨(dú)配置用于實(shí)部數(shù)據(jù),也可成對(duì)配置用于實(shí)部和虛部I/Q數(shù)據(jù)。

Soft Decision Forward Error Correction (SD-FEC)概述

一些ZynqUltraScale+ RFSOC包括高度靈活的軟判決FEC塊,用于解碼和編碼數(shù)據(jù),作為在不可靠或有噪聲的通信信道上控制數(shù)據(jù)傳輸錯(cuò)誤的手段。SD-FEC塊支持低密度奇偶校驗(yàn)(LDPC)解碼/編碼和Turbo解碼,用于5G無(wú)線、回程、DOCSIS和LTE應(yīng)用。

處理器系統(tǒng)(PS)概述

Zynq UltraScale+RFSOC具有四核Arm Cortex-A53 (APU)和雙核Arm Cortex-R5F (RPU)處理系統(tǒng)(PS)。支持處理器的功能,大量的外圍設(shè)備和專(zhuān)用功能都包含在PS。連接到外部數(shù)據(jù)或配置存儲(chǔ)記憶,PS包括一個(gè)多協(xié)議動(dòng)態(tài)內(nèi)存控制器,DMA控制器,NAND閃存控制器,SD / eMMC控制器和一個(gè)四SPI控制器。除了與外部存儲(chǔ)器接口外,APU還包括1級(jí)(L1)和2級(jí)(L2)緩存層次結(jié)構(gòu);RPU包括L1緩存和緊耦合內(nèi)存子系統(tǒng)。每個(gè)芯片都可以訪問(wèn)一個(gè)256KB的片內(nèi)存儲(chǔ)器。

對(duì)于高速接口,PS包括4個(gè)通道的發(fā)送(TX)和接收(RX)對(duì)收發(fā)器,稱(chēng)為PS- GTR收發(fā)器,支持高達(dá)6.0Gb/s的數(shù)據(jù)速率。這些收發(fā)器可以接口到高速外設(shè)塊,支持PCIe在5.0GT/s (Gen2)作為根復(fù)合或端點(diǎn)在x1, x2,或x4配置;串行ATA (SATA) 1.5Gb/s, 3.0Gb/s,或6.0Gb/s的數(shù)據(jù)速率;和多達(dá)兩個(gè)通道的DisplayPort在1.62Gb/s, 2.7Gb/s,或5.4Gb/s的數(shù)據(jù)速率。PS-GTR收發(fā)器還可以通過(guò)USB 3.0和串行千兆媒體獨(dú)立接口(SGMII)與組件接口。

對(duì)于一般連接,PS包括:一對(duì)USB 2.0控制器,可以配置為主機(jī)、設(shè)備或on - go (OTG);一個(gè)I2C控制器;一個(gè)UART;和符合ISO11898-1的CAN2.0B控制器。還有4個(gè)三速以太網(wǎng)MAC和128位GPIO,其中78位通過(guò)MIO和96位通過(guò)EMIO可用。基于ARM AMBA AXI4協(xié)議的高帶寬連接將處理單元與外設(shè)連接起來(lái),并提供PS和可編程邏輯(PL)之間的接口。

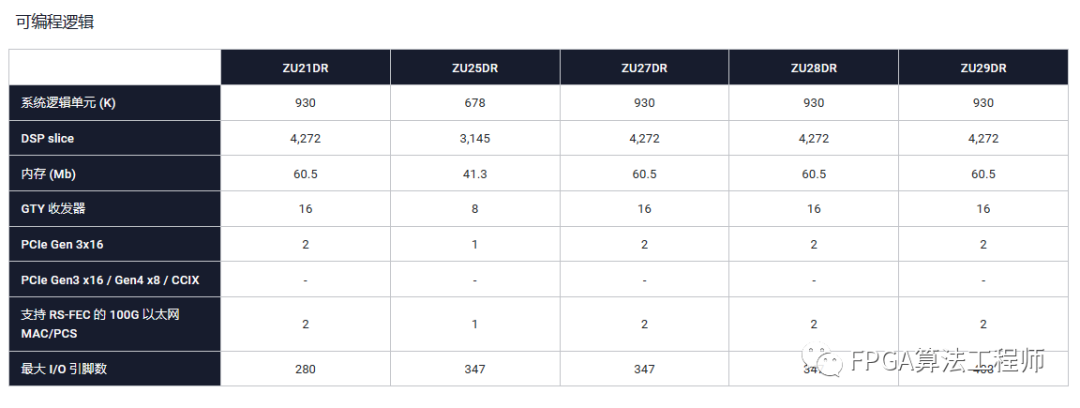

I/O, Transceiver, PCIe, 100G Ethernet, and 150G Interlaken

數(shù)據(jù)通過(guò)高性能并行SelectIO接口和高速串行收發(fā)器連接的組合在芯片上和芯片外傳輸。I/O塊通過(guò)靈活的I/O標(biāo)準(zhǔn)和電壓支持提供對(duì)尖端內(nèi)存接口和網(wǎng)絡(luò)協(xié)議的支持。基于UltraScale架構(gòu)的設(shè)備中的串行收發(fā)器傳輸數(shù)據(jù)最高可達(dá)28.21Gb/s,實(shí)現(xiàn)25G+背板設(shè)計(jì),比上一代收發(fā)器的每位功耗顯著降低。除PS-GTR外,所有模塊均支持PCIe接口卡所需的數(shù)據(jù)速率為8.0GT/s (Gen3)和16.0GT/s (Gen4)。PCIe集成塊可以配置為端點(diǎn)或根端口,根據(jù)目標(biāo)設(shè)備速度等級(jí)和包支持各種鏈路寬度和速度。用于150Gb/s Interlaken和100Gb/s以太網(wǎng)(100G MAC/PCS)的集成塊擴(kuò)展了UltraScale設(shè)備的能力,實(shí)現(xiàn)了對(duì)Nx100G交換機(jī)和橋接應(yīng)用的簡(jiǎn)單、可靠的支持。

時(shí)鐘和內(nèi)存接口

Zynq UltraScale+RFSOC包含強(qiáng)大的時(shí)鐘管理電路,包括時(shí)鐘合成、緩沖和路由組件,共同提供了一個(gè)高能力的框架,以滿足設(shè)計(jì)需求。時(shí)鐘網(wǎng)絡(luò)允許非常靈活的時(shí)鐘分配,以最小化與時(shí)鐘信號(hào)相關(guān)的歪斜、功耗和延遲。時(shí)鐘管理技術(shù)與專(zhuān)用內(nèi)存接口電路緊密集成,以支持高性能外部存儲(chǔ)器,包括DDR4。除了并行內(nèi)存接口,Zynq UltraScale+ RFSOC還支持串行內(nèi)存,比如(HMC)。

路由、邏輯、存儲(chǔ)和信號(hào)處理

可配置邏輯塊(CLB)包含6輸入查找表(LUT和觸發(fā)器,DSP片與27x18乘法器,36Kb Block RAM與內(nèi)置FIFO和ECC支持,和4Kx72 UltraRAM塊都與豐富的高性能,低延遲互連連接。除了邏輯函數(shù)外,CLB還提供移位寄存器、多路復(fù)用器和攜帶邏輯功能,以及將LUT配置為分布式內(nèi)存的能力,以補(bǔ)充高能力和可配置的BRAM。DSP芯片具有96位的異或功能、27位的預(yù)加法器和30位的A輸入,可執(zhí)行多項(xiàng)獨(dú)立的功能,包括乘累加、乘加和模式檢測(cè)。

配置、加密和系統(tǒng)監(jiān)控

Zynq UltraScale+RFSoC通過(guò)配置安全單元(CSU)引導(dǎo),CSU支持通過(guò)256位AES-GCM和SHA/384塊進(jìn)行安全引導(dǎo)。CSU中的加密引擎可以在引導(dǎo)后的RFSoC中用于用戶加密。系統(tǒng)監(jiān)視器可以通過(guò)片上溫度和電源傳感器監(jiān)控物理環(huán)境,還可以監(jiān)控多達(dá)17個(gè)外部模擬輸入。

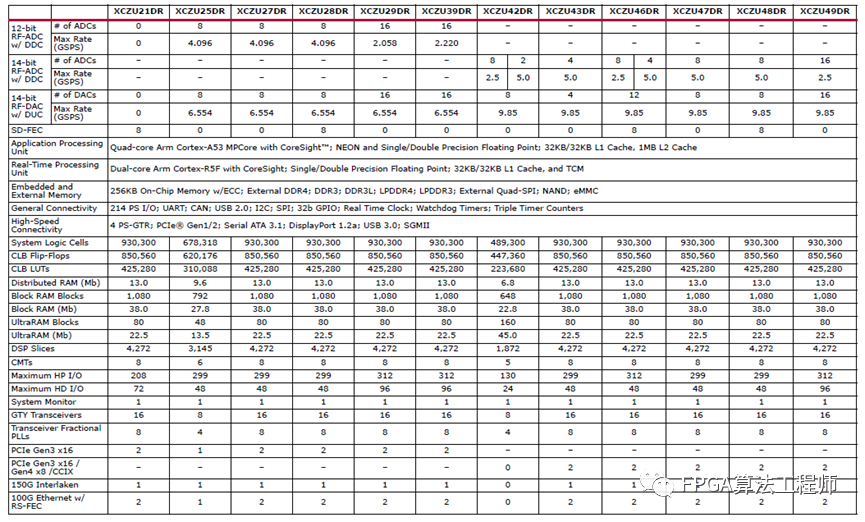

特性總結(jié)如表2所示。

表2 Zynq UltraScale+ RFSOC特性總結(jié)

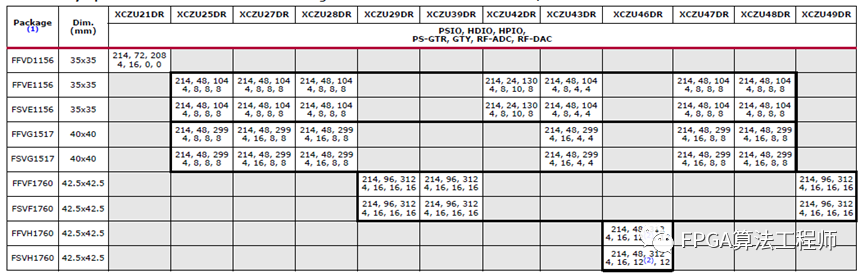

表3 Zynq UltraScale+ RFSoC Device-Package combination and Maximum I/O

相關(guān)產(chǎn)品

審核編輯:劉清

-

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5460瀏覽量

172724 -

soc

+關(guān)注

關(guān)注

38文章

4204瀏覽量

219091 -

ARM處理器

+關(guān)注

關(guān)注

6文章

361瀏覽量

41936 -

數(shù)據(jù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

1文章

366瀏覽量

28112

原文標(biāo)題:Zynq UltraScale+ RFSoC器件介紹

文章出處:【微信號(hào):FPGA算法工程師,微信公眾號(hào):FPGA算法工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

如何調(diào)試Zynq UltraScale+ MPSoC VCU DDR控制器

Xilinx基于ARM的Zynq-7000和Zynq UltraScale+ MPSoC及RFSoC器件是否存在安全漏洞

Zynq UltraScale+ RFSoC的功能特點(diǎn)與應(yīng)用

Zynq UltraScale+ MPSoC的發(fā)售消息

Zynq UltraScale+ MPSoC器件的收發(fā)器技術(shù)演示

支持6GHz以下頻段的Zynq UltraScale+RFSoC

上新:Zynq UltraScale+ RFSoC ZCU111 評(píng)估套件

賽靈思關(guān)于Zynq UltraScale+ RFSoC系列產(chǎn)品介紹

賽靈思公司宣布其Zynq UltraScale+ RFSoC系列開(kāi)始發(fā)貨

Zynq UltraScale+ 器件與PL DNA不同的值

基于Xilinx Zynq UltraScale+ RFSoC ZCU216評(píng)估套件詳細(xì)內(nèi)容介紹

Zynq UltraScale+ RFSoC DFE數(shù)據(jù)表:概述

Zynq UltraScale+器件封裝和管腳用戶指南

Zynq UltraScale+ RFSoC器件介紹

Zynq UltraScale+ RFSoC器件介紹

評(píng)論