PCIE 6.0 (三)

事務(wù)層

⊙transaction layer

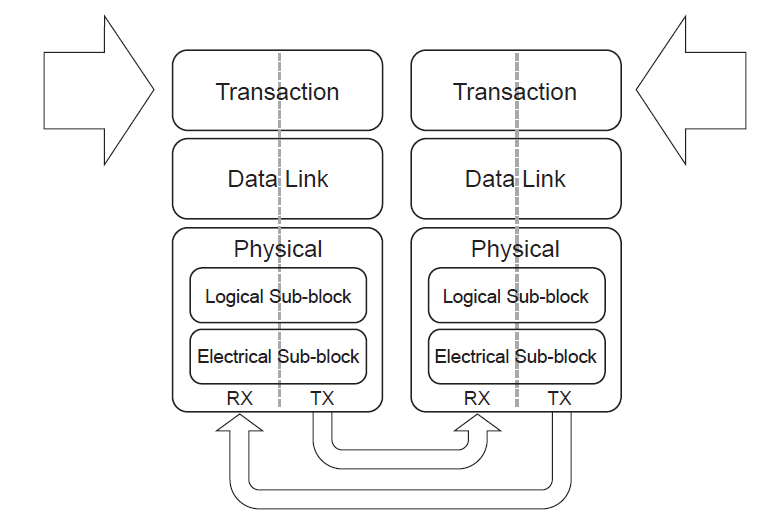

作為協(xié)議的最高層,事務(wù)層的主要功能是:

? 流水線式完整拆分交易協(xié)議

? 區(qū)分事務(wù)層數(shù)據(jù)包 (TLP) 的排序和處理要求的機(jī)制

? 基于credit的流量控制

? 可選支持?jǐn)?shù)據(jù)中毒和端到端數(shù)據(jù)完整性檢測(cè)。

0****1

**###

Transaction Layer Overview

**

PCIe 6.0 增加了一種新的傳輸模式 flit mode,而傳統(tǒng)的傳輸模式就變成了non-flit mode。在傳統(tǒng)模式中,TLP是不定長(zhǎng)的,物理層中需要start end標(biāo)志來(lái)標(biāo)記數(shù)據(jù)包的頭和尾。而且TLP和DLLP是工作在不同的層中,相互之間是獨(dú)立的。

PCIe 6.0的flit mode借用了NoC中flit的概念(也可能不是借用,因?yàn)楣P者是做NoC的,所以可能會(huì)有先入為主的影響),將多個(gè)TLP和一個(gè)DLLP的信息打包成一個(gè)大的數(shù)據(jù)幀,稱為flit,數(shù)據(jù)的傳輸以flit為單位,每個(gè)flit固定為256Byte。需要注意的是,flit既不在事務(wù)層也不在數(shù)據(jù)鏈路層,而是在物理層,就好比NoC的flit是直接定義在物理總線上的,PCIe的flit是直接定義在物理層的lane中的.

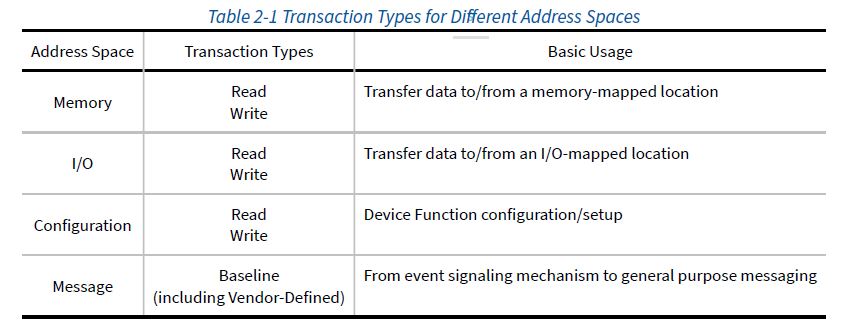

事務(wù)層是請(qǐng)求者和完成者之間信息傳輸?shù)幕A(chǔ)。 在這層協(xié)議中定義了四個(gè)地址空間,并定義了不同的事務(wù)類型,每個(gè)都有自己獨(dú)特的預(yù)期用途,如下所示

事務(wù)層是請(qǐng)求者和完成者之間信息傳輸?shù)幕A(chǔ)。 在這層協(xié)議中定義了四個(gè)地址空間,并定義了不同的事務(wù)類型,每個(gè)都有自己獨(dú)特的預(yù)期用途,如下所示

Memory Transactions

內(nèi)存事務(wù)包括以下類型:

? 讀取請(qǐng)求/完成

? 寫請(qǐng)求

? 可延遲內(nèi)存寫入請(qǐng)求/完成

? 原子操作的請(qǐng)求/完成

I/O Transactions

PCI Express 支持 I/O 空間,以便與需要使用它們的舊設(shè)備兼容。 I/O 事務(wù)包括以下類型:

? 讀取請(qǐng)求/完成

? 寫請(qǐng)求/完成

Message Transactions

message事務(wù),或簡(jiǎn)稱為消息,用于支持設(shè)備之間事件的帶內(nèi)通信。除了協(xié)議中定義的特定消息外,PCI Express 還支持供應(yīng)商定義的消息使用指定的消息代碼。

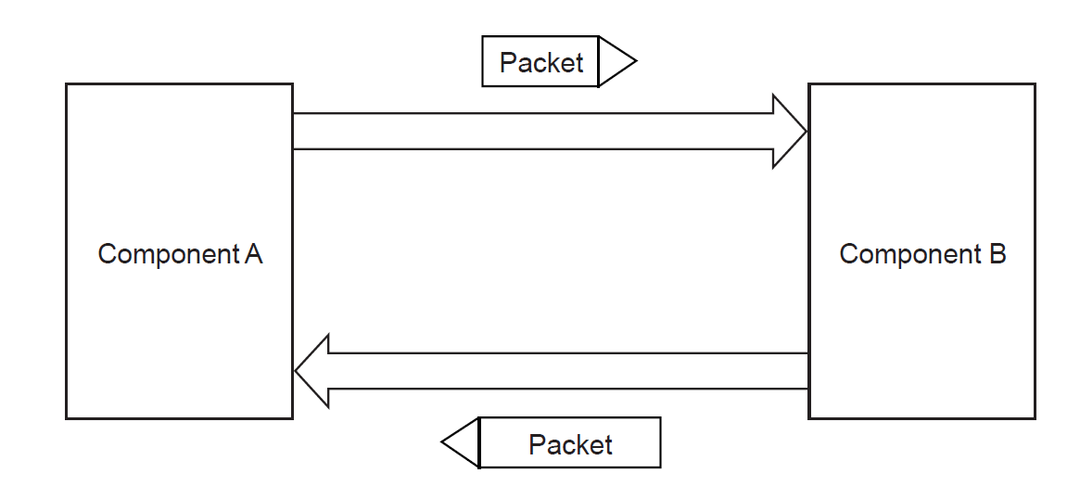

事務(wù)層數(shù)據(jù)包格式

事務(wù)由請(qǐng)求和完成組成,它們使用數(shù)據(jù)包進(jìn)行通信。數(shù)據(jù)包的域斷可見下圖,(一個(gè)數(shù)據(jù)包的大小如果為512Bit,則每個(gè)預(yù)斷的值就是將512Bit的值按順序填在下圖的格式表中)。

0****2

事務(wù)層協(xié)議 - 數(shù)據(jù)包定義

前面給大家介紹了TL的數(shù)據(jù)包格式由TLP Prefix、header,data組成。下面為大家介紹在每個(gè)小部分里不同域斷的含義。

Header Fields For Non-Flit Mode

Fmt 字段指示一個(gè)或多個(gè) TLP 前綴的存在,Type 字段指示相關(guān)的 TLP前綴類型。

- TLP Header 的 Fmt 和 Type 字段提供了確定剩余部分大小所需的信息。同時(shí)TLP 報(bào)頭的 Fmt、Type、TD 和 Length 字段包含確定 TLP 非前綴部分的總體大小所需的所有信息。 Type 字段除了定義 TLP 的類型外,還決定了交換機(jī)如何路由 TLP。 以下各節(jié)將不同類型的 TLP。

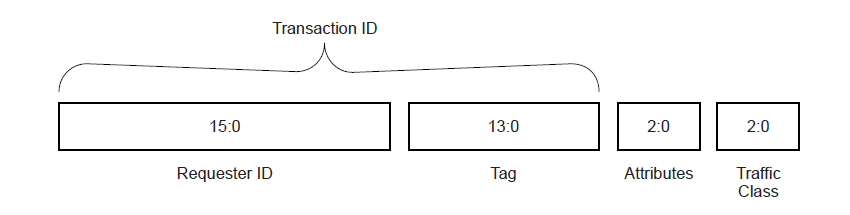

- TC[2:0]:流量類別 (TC) 是一個(gè) 3 位字段,允許將事務(wù)區(qū)分為八個(gè)流量類別。 與 PCI Express 虛擬通道支持一起,TC 機(jī)制是實(shí)現(xiàn)差異化流量服務(wù)的基本要素。(TC0是表示此次傳輸?shù)臄?shù)據(jù)包優(yōu)先級(jí)最高要優(yōu)先通過(guò)) 每個(gè) PCI Express 事務(wù)層數(shù)據(jù)包都使用 TC 信息作為在 PCI Express 結(jié)構(gòu)中端到端攜帶的不變標(biāo)簽。 當(dāng)數(shù)據(jù)包穿過(guò)結(jié)構(gòu)時(shí),此信息將在每個(gè)鏈路和每個(gè)交換機(jī)元素內(nèi)使用,以做出有關(guān)正確處理流量的決策。 服務(wù)的一個(gè)關(guān)鍵方面是根據(jù) TC 標(biāo)簽通過(guò)相應(yīng)的虛擬通道路由數(shù)據(jù)包。

- R:保留;

- TLP Hints (TH):TLP Hints,用以指示 TLP Header 中是否含有 TPH 及 TPH TLP Prefix。(具體參考PCIE協(xié)議介紹)

- Attr:Attributes,通過(guò)該字段提供附加信息給接收端,告知接收端采用非默認(rèn)方式來(lái)處理當(dāng)前 TLP,常用于 TLP 排序、Snoop 硬件一致性管理等方面。

- TD:TLP Digest,用以指示 TLP 末尾的 Digest 字段是否含有 ECRC。僅用于 NFM。FM 的 ECRC 相關(guān)指示放在了 TS。

- Error Poisoned:Error Poisoned,PCIe E2E 數(shù)據(jù)完整性相關(guān),用以指示當(dāng)前 TLP 的 Data Payload 被污染。

- Length[9:0]:Length,用以指示當(dāng)前 TLP 的 Data Payload 長(zhǎng)度,僅對(duì)帶有 Data Payload 的 TLP 有效, 單位為 DW。

Data Payloads For Non-Flit Mode

ARI : Alternative Routing-ID,用于Requester IDs,Completer IDs以及Routing ID。

ARI Device : 與Upstream Port關(guān)聯(lián)的設(shè)備,其Functions均包含 ARI Extended

ARI Downstream Port : 支持 ARI 轉(zhuǎn)發(fā)的Switch Downstream Port或Root Port。

( ARI(Alternative Routing-ID),備選路由ID。在PCIE中,往往數(shù)據(jù)包傳輸通過(guò)TLP的形式。這些TLP大致分為Memory Read/Write TLP , Configuration Read/Write TLP ,Completion TLP, Message TLP以及IO TLP。這些TLP從Request端到Completion端的過(guò)程叫做路由,而路由又大致分為兩類地址路由和ID路由。

所有的ID路由中的ID包括Request端的bus number,device number以及function number。其中ID有16 bits,bus number 8 bits,device number 5 bits,function number 3 bits意味著支持8個(gè)function。

對(duì)于有些device功能比較復(fù)雜或者支持FBP技術(shù)的root port或者device,往往8個(gè)function不足以滿足要求,這個(gè)時(shí)候就出現(xiàn)了ARI技術(shù)。將device number的5 bits也用作function,這樣便可以由原來(lái)的8個(gè)function擴(kuò)展到256個(gè)function。 )

- Length表示DW的數(shù)目,為整數(shù)

- 除了那些明確引用數(shù)據(jù)長(zhǎng)度的消息,Length[9:0] 為所有Message保留

(請(qǐng)參閱協(xié)議第 2.2.8 節(jié)中的Message Code表。) - 有 data payload的 TLP 發(fā)送器不允許TLP Length字段給出的data payload長(zhǎng)度超過(guò)發(fā)送器Device Control寄存器 Max_Payload_Size 字段中的值指定的DW長(zhǎng)度。

- 對(duì)于ARI 設(shè)備,Max_Payload_Size 僅由Function 0 中的設(shè)置決定,忽略其他Function中的 Max_Payload_Size 設(shè)置。

- 如果一個(gè)非ARI Multi-Function Device(MFD)中的所有Functions 的Max_Payload_Size完全相同,如果有個(gè)Upstream Port與這個(gè)MFD相關(guān)聯(lián),它傳輸?shù)?TLP data payload不得超過(guò)通用 Max_Payload_Size 設(shè)置。

- 如果一個(gè)非ARI Multi-Function Device(MFD)中的所有Functions 的Max_Payload_Size不完全相同,如果有個(gè)Upstream Port與這個(gè)MFD相關(guān)聯(lián),它傳輸?shù)?TLP data payload不得超過(guò)我們自定義的 Max_Payload_Size 設(shè)置。

- 由 TLP 的 Length 字段給出的已接收 TLP 的data payload大小不得超過(guò)接收器設(shè)備Controller 寄存器的 Max_Payload_Size 字段中的值指定的長(zhǎng)度。接收者必須檢查是否違反此規(guī)則。 如果接收器確定 TLP 違反此規(guī)則,則該 TLP 是格式錯(cuò)誤的 TLP,這是一個(gè)與接收端口相關(guān)的報(bào)告錯(cuò)誤。

- 對(duì)于 ARI 設(shè)備,Max_Payload_Size 僅由Function 0 中的設(shè)置確定。其他Function中的 Max_Payload_Size 設(shè)置將被忽略。

- 如果一個(gè)非ARI Multi-Function Device(MFD)中的所有Functions 的Max_Payload_Size完全相同,如果有個(gè)Upstream Port與這個(gè)MFD相關(guān)聯(lián),接收器需要根據(jù)通用 Max_Payload_Size 的設(shè)置檢查 TLP data payload大小。

- 如果一個(gè)非ARI Multi-Function Device(MFD)中的所有Functions 的Max_Payload_Size不完全相同,如果有個(gè)Upstream Port與這個(gè)MFD相關(guān)聯(lián),接收器需要根據(jù)自定義的Max_Payload_Size 設(shè)置檢查 TLP 的data payload。

對(duì)于包含數(shù)據(jù)的 TLP,Length字段中的值與 TLP 中包含的實(shí)際數(shù)據(jù)量必須匹配。同時(shí),接收者必須檢查是否違反此規(guī)則。 如果接收器確定 TLP 違反此規(guī)則,則該 TLP 是Malformed TLP,這是一個(gè)跟Receiving Port相關(guān)的Reported Error。(RTL實(shí)現(xiàn)中要實(shí)現(xiàn)的ERROR異常)

-

PCIe

+關(guān)注

關(guān)注

15文章

1260瀏覽量

83193 -

數(shù)據(jù)包

+關(guān)注

關(guān)注

0文章

267瀏覽量

24500 -

TLP

+關(guān)注

關(guān)注

0文章

32瀏覽量

15672

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Oracle核心技術(shù)之事務(wù)和鎖

一個(gè)簡(jiǎn)單地的例子來(lái)回顧PCIe總線的結(jié)構(gòu)、事務(wù)層、數(shù)據(jù)鏈路層和物理層

數(shù)據(jù)庫(kù)設(shè)計(jì)開發(fā)技術(shù)案例教程之事務(wù)控制與鎖定

楷登電子發(fā)布PCIe 6.0規(guī)范Cadence IP

PCIe 6.0的新變化與新挑戰(zhàn)

是德科技發(fā)布新款端到端的PCIe5.0/6.0測(cè)試解決方案

CXL事務(wù)層詳解

干貨:PCIE6.0技術(shù)剖析

如何破解PCIe 6.0帶來(lái)的芯片設(shè)計(jì)新挑戰(zhàn)?

PCIe 6.0入門之什么是 PCIe 6.0

PCIe 6.0入門基本結(jié)構(gòu)和功能層介紹

PCIe 6.0入門之事務(wù)層報(bào)文格式

PCIe 6.0入門之事務(wù)層

PCIe 6.0入門之事務(wù)層

評(píng)論