本博客的第 1 部分探討了從事片上系統 (SoC) 目標高能效設計的設計人員面臨的問題,以及 Synopsys 的 PrimeShield 設計魯棒性解決方案如何幫助優化低功耗設計,同時實現積極的上市時間目標。

最后一部分將深入探討PrimeShield設計魯棒性解決方案如何幫助SoC設計人員優化其設計以實現高性能,同時滿足緊迫的設計計劃,并提供一些實際示例。

設計穩健性,實現高性能設計

在時序的情況下,經過驗證的方法使用靜態時序分析 (STA) 來分析每個時序路徑,并根據頻率指標單獨檢查它們。由于高級節點的顯著可變性,特別是在低電壓下,非常需要分析由高可變性引起的潛在性能瓶頸。通過對所有關鍵路徑進行統計關聯來識別這些瓶頸的統計分析可以避免過度補償,同時提高設計性能、功耗和面積 (PPA) 指標。在時序性能方面也出現了新的PPA機會。

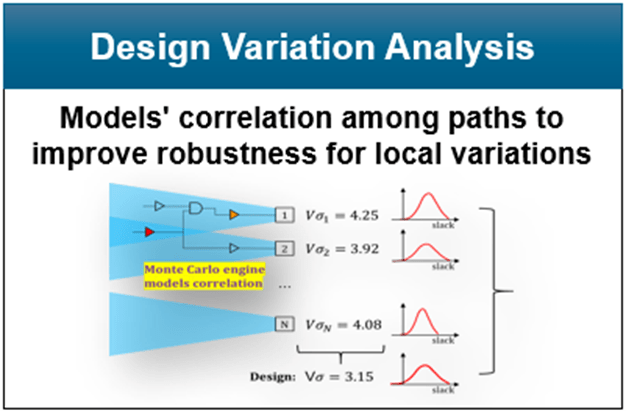

PrimeShield設計變異分析(DVA)通過顯式跟蹤通過公共單元的路徑之間的相關性來計算準確的每個端點西格瑪。它使用 STA 蒙特卡羅分析以及來自現有 LVF 庫的精確時序數據實現可預測的時序,并針對運行時進行了高度優化。DVA的路徑相關性感知方法顯著降低了悲觀情緒,而不是假設路徑是獨立的傳統方法。變化魯棒性功能還可以識別芯片上的瓶頸單元,通常是變化較大且引腳松弛不足的單元;修復這些電池可以顯著提高設計魯棒性,而功耗可以忽略不計。

在基于時序裕量的傳統方法中,旨在確保穩健性的增加裕量會對性能產生負面影響。降低時序裕量的關鍵是通過控制晶體管之間對時鐘路徑工藝變化的跟蹤來減少時鐘和信號偏斜冗余。為了減少時序悲觀情緒,PrimeShield設計魯棒性解決方案執行全局偏斜分析。全局偏斜分析計算與全局和互連 VT 偏斜相關的路徑魯棒性。

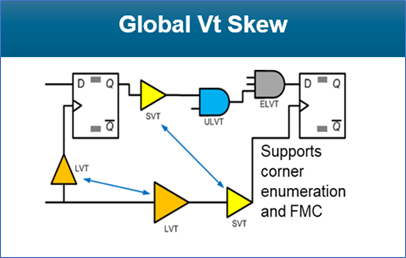

全局 V T 變化在單個 V T 類中具有很強的相關性,但在不同的 VT 類之間僅部分相關。與傳統分析一樣,同時應用最小/最大時序降額過于悲觀;然而,對N VT類的2種N組合的分析是極其成本和資源密集型的。因此,設計人員被迫在時鐘網絡中僅使用一種VT類型,并背負著額外的時序悲觀的懲罰。

PrimeShield全局V T偏斜分析允許用戶在發射和捕獲路徑中對相同VT類的所有單元應用相同的降額。因此,它抵消了同一VT級變化的發射/捕獲影響,顯著降低了悲觀情緒,同時仍確保簽核安全。該分析還允許在時鐘網絡中使用多個V T類,同時提高簽核安全性,即使在時鐘網絡中使用一種VT類型也是如此。

此外,PrimeShield 設計魯棒性解決方案通過顯著減少全局 V T 變化所需的 STA 角庫數量以及 N V T 類確定最差混合 V T 時序松弛所需的 2N V T 組合運行,提高了設計人員的工作效率。

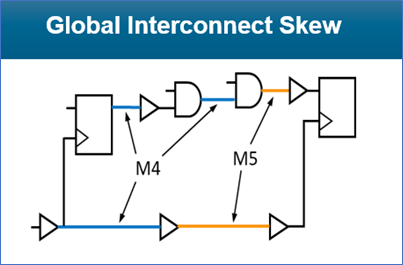

同樣,金屬/互連變化在每層內也高度相關,但在不同的金屬層之間僅部分相關。與傳統分析一樣,同時應用最小/最大寄生邊界過于悲觀;然而,對N種金屬層的2種N組合進行分析是極其成本和資源密集型的。

PrimeShield 全局互連偏斜分析明確模擬了發射和捕獲路徑中相同金屬層內變化的延遲影響的抵消。它減少了時序悲觀情緒,同時仍然提供簽核安全性;可以采用基于蒙特卡羅的快速分析來實現最高精度。全面的設計變化和全局偏斜分析可最大限度地減少時序悲觀保護帶和過裕量,從而改善設計性能并提升 FMAX。

證據就在布丁里

通過早期的合作伙伴關系和廣泛的合作,燈塔客戶已轉向PrimeShield設計魯棒性解決方案,以利用相互技術和專有技術來提高先進節點設計的魯棒性,并實現新的功耗和性能水平。

PrimeShield設計穩健性解決方案已經在多個客戶部署中證明了其有效性:

移動/5G、HPC 和汽車領域的全球半導體領導者在多個模塊的總功耗降低 4% 后,在 3/6 納米超低功耗設計流片上部署了 PrimeShield。

一家大型北美半導體領導者在 5/4 nm 設計上部署了 PrimeShield 設計魯棒性解決方案,通過設計變化分析、7:13 VT 庫角落和運行時間縮短以及 1× 蒙特卡羅仿真性能改進,FMAX 提升了 120%。

亞洲一家大型手機芯片供應商能夠在保持相同功率和面積的同時,將下一代 8 納米高性能 CPU 的 FMAX 提高近 5%。

一家供應商通過使用PrimeShield電壓松弛分析,同時保持時序,在為美國領先的超大規模企業設計的11 nm SoC上,將動態功耗降低了5%。

總結

如今,由于統計魯棒性分析的成本和復雜性,它通常在設計周期的后期進行,甚至作為事后分析。但對于領先的客戶來說,魯棒性已成為除功耗、性能和面積之外必不可少的設計質量指標。PrimeShield設計魯棒性解決方案的快速、高容量魯棒性分析引擎意味著設計人員最終可以在整個設計流程中優化最佳設計性能、功耗、面積和魯棒性(PPA-R)。

PrimeShield 設計魯棒性解決方案在 Synopsys 融合設計平臺中提供,可提供具有最小統計魯棒性損失和最佳設計 PPA-R 的設計。它為客戶設計團隊提供全面的全局魯棒性、偏斜和電壓松弛分析和優化,以解決由變化引起的設計漏洞,同時最大限度地提高下一代設計的能效和性能。

審核編輯:郭婷

-

半導體

+關注

關注

334文章

27703瀏覽量

222630 -

soc

+關注

關注

38文章

4204瀏覽量

219093 -

STA

+關注

關注

0文章

51瀏覽量

19033

發布評論請先 登錄

相關推薦

NVIDIA火熱招聘GPU高性能計算架構師

時鐘設備如何滿足復雜系統的高性能時序需求?

高性能DAQ系統的ADC電壓基準兩級緩沖器優化設計

滿足各種不同應用需求的RF功率測量優化方法討論

時鐘IC怎么滿足高性能時序需求?

AutoKernel高性能算子自動優化工具

卓越性能電源計劃的目的

怎么把電源計劃設置為高性能呢

Hitek Systems開發基于PCIe的高性能加速器以滿足行業需求

優化設計以實現高性能,同時滿足嚴格的設計計劃

優化設計以實現高性能,同時滿足嚴格的設計計劃

評論