長期以來,IC測試的基本挑戰一直保持不變。所有測試策略的核心是可控性和可觀察性。首先,使用已知的測試向量控制芯片的狀態,然后觀察芯片以確定其行為是良好還是錯誤。多年來,已經有許多創新使所需的芯片測試更容易處理。得益于 EDA 社區的創新,可測試性設計 (DFT) 和自動測試模式生成 (ATPG) 為 IC 測試 的挑戰帶來了豐富的方法。

當前限制

這些方法的主要內容是掃描測試。在這里,普通人字拖被具有雙重用途的掃描人字拖所取代。在正常操作中,它們的功能與任何其他翻牌一樣。然而,當啟用掃描模式時,這些器件形成一個鏈,允許將測試向量轉移到電路中,基本上將電路的狀態設置為已知值。這解決了測試挑戰的可控性部分。然后,這些觸發器返回正常工作狀態,以允許電路處理已知數據。然后,重新啟用掃描模式,并將內部數據值移出電路,以便在芯片的主輸出端口進行檢查。這將處理測試質詢的可觀測性部分。

雖然簡單而優雅,但基于掃描的設計有兩個基本限制。首先,這個過程可能很慢,需要許多時鐘周期來掃描數據,然后掃描出來進行觀察。請記住,您是在生產測試儀上運行這些測試。這些是非常大且昂貴的設備,每一秒的使用都會增加額外的成本。第二個問題是芯片I/O子系統的負擔。掃描設計需要大量額外的引腳,而芯片I/O通常供不應求。因此,支持許多芯片I/O的掃描模式的額外開銷可能很麻煩。

目前的方法還有第三個缺點,相對較新。如上一篇文章所述,芯片測試在零件交付時不再停止。隨著硅生命周期管理(SLM)的興起,從芯片收集數據將貫穿其整個生命周期。這里描述的掃描測試方法依賴于IC測試儀提供的大量特殊設置。外地沒有這種設備。

建議的解決方案

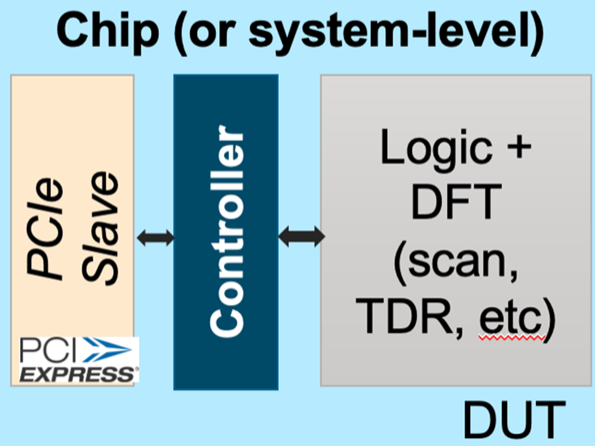

解決這些問題的新方法隱藏在眾目睽睽之下。I/O幾乎是每個設計的瓶頸,因此高速協議已成為最小化此問題的常用方法。幾乎每個芯片都有一個PCIe或USB接口。這些是支持各種 I/O 要求的高性能端口。如果這些端口成為未來設計的新掃描端口會怎樣?測試性能將得到增強(成本將下降),引腳電子器件將更簡單,在現場訪問芯片的測試功能將容易得多。將掃描測試與系統級測試相結合,還有另一個潛在的成本優勢。下圖說明了為板載 PCIe 接口創建另一種模式的基本方法。

圖 1: 新的測試訪問電子設備

交付解決方案

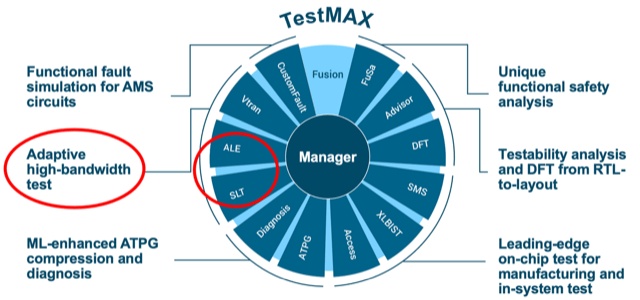

Synopsys TestMAX 系列測試產品于今年 3 月推出。它代表了業界最全面的測試解決方案集,可滿足制造測試要求以及汽車和其他功能安全相關應用的快速發展的在系統測試要求。該平臺提供廣泛的測試支持,如下所示。

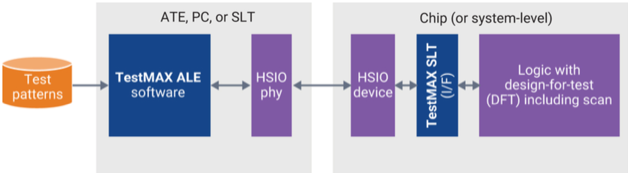

該平臺的兩個部分,TestMAX SLT和TestMAX ALE實現了這種革命性的新掃描測試方法。讓我們來看看這是如何工作的。

圖2:TestMAX平臺

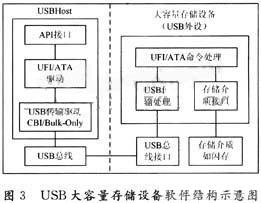

首先,TestMAX SLT在現有的高速接口(HSIO,例如USB,PCIe)和DFT邏輯之間生成前面描述的片上接口,DFT邏輯通常由掃描和壓縮功能組成。然后,TestMAX ALE為HSIO提供類似于軟件設備驅動程序的軟件接口。它支持操作系統文件 I/O 與驅動主機 HSIO 的軟件層之間的通信。下圖說明了完整的端到端雙向路徑。

圖3:一種新的掃描測試方法

這種方法的好處包括:

高帶寬測試數據,降低測試成本

引腳數最少的接口,適用于大多數設計

輕松適應支持不同的高速輸入輸出接口 (HSIO)

更簡單的自動測試儀設備 (ATE) 引腳電子元件,可降低測試儀成本

通過應用初始制造測試(硅生命周期管理支持)確保系統內器件的高質量

我們對IC測試的這種新范式感到非常興奮,并相信它將降低測試成本,同時提高質量。我們還與測試領導者愛德萬測試和泰瑞達合作,以確保這項新技術的順利部署。

審核編輯:郭婷

-

芯片

+關注

關注

456文章

51182瀏覽量

427277 -

接口

+關注

關注

33文章

8691瀏覽量

151919 -

eda

+關注

關注

71文章

2788瀏覽量

173866

發布評論請先 登錄

相關推薦

泰克在2013 IDF展示業界最完整、最靈活的高速串行信號測試解決方案

FPGA的PCIE接口應用需要注意哪些問題

如何進行PCI-Express的一致性測試和分析

高速 ADC/DAC 測試原理及測試方法

對RIFFA架構的的DMA性能(Scatter-Gather DMA)進行測試

基于USB接口的通用測試儀的設計與實現

測試行業三家企業聯手,舉辦2021高速數字接口測試巡回研討會

網絡研討會-高速接口測試:PCIe5.0測試方案

M8040A誤碼儀助力高速數字接口測試

使用高速PCIe或USB接口提高測試性能并允許在現場進行測試

使用高速PCIe或USB接口提高測試性能并允許在現場進行測試

評論