預計在不久的將來,數十億的互聯網連接設備和數據密集型實時應用程序將出現在市場上,而當今數據中心常見的100千兆以太網(GE)速度將不足以處理帶寬。因此,我們已經預計數據中心運營商需要將其網絡從100 GE遷移到400 GE,從而產生對更快內存和更快串行總線通信的需求。

PCIe 是用于點對點通信的高速差分串行標準。每一代 PCIe 標準都提供比上一代產品更多的功能和更快的數據傳輸速率。最新一代 PCIe 5.0 將使 PCIe 4.0 的吞吐率翻倍。PCIe 5.0 的傳輸速率為每秒 32 千兆傳輸 (GT/s),而 PCIe 16.4 支持的傳輸速率為 0 GT/s。PCIe 64.5 具有每秒 0 千兆字節 (GB/s) 的單向傳輸帶寬,以 128 GB/s 的雙向流量提供數據。

除了將帶寬翻倍外,PCIe 5.0 還提供其他新功能,例如:

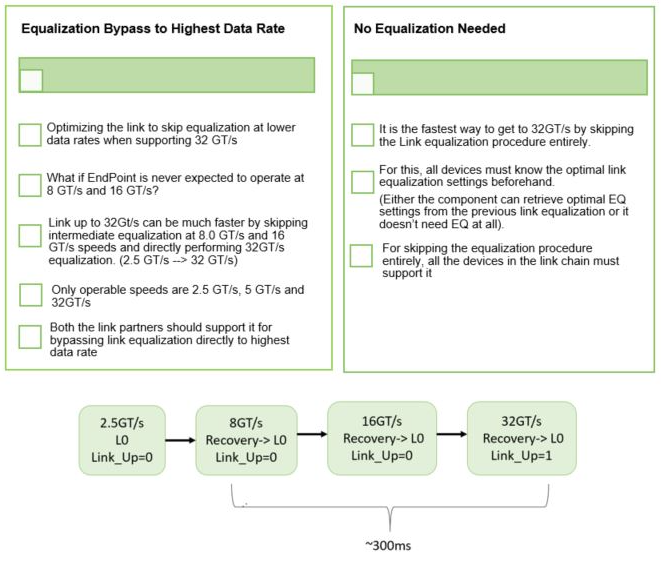

? 均衡旁路模式,可加快鏈路初始化速度

? 允許備用協議通過鏈路訓練

進行協商 ? 預編碼支持,幫助避免突發錯誤

? 環回增強功能允許模擬串擾行為

在本博客中,我們將介紹 32 GT/s 時的 PHY 邏輯變化,并介紹均衡過程中發生的主要變化。

但是,在深入研究新的均衡模式之前,讓我們先談談為什么我們需要新模式......

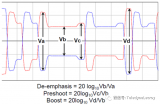

數據速率的提高也意味著信號衰減的增加,這對更高頻率的分量影響最大。這最終會導致失真,需要通過均衡程序進行補償。與 PCIe 3.0 和 4.0 一樣,對于以 32GT/s 運行的設備,建議使用均衡來調整發射器和接收器設置以提高信號質量。PCIe 0.1 的均衡階段(階段 2、3、5、0)與前幾代相同。

讓我們看一下啟動鏈接到 32 GT/s 所涉及的步驟。鏈路最初必須以 0.2 GT/s 的速度訓練到 L5,然后依次以 8.0 GT/s、16 GT/s 和 32 GT/s 的速度進行均衡。這被稱為傳統的“完全均衡”模式。

隨著數據速率越來越高,這種方法變得越來越耗時,并增加了鏈路啟動的延遲。根據一些供應商的說法,具有均衡功能的單速轉換大約需要~100ms,這意味著啟動到300GT / s的鏈路需要~32ms。優化鏈路啟動的需求導致引入了兩種新的可選模式:

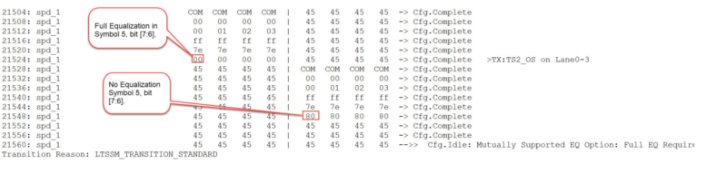

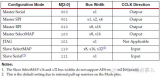

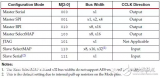

為了方便這些可選的均衡模式,修改了 TS OS 的 Symbol5(訓練控制)。鏈路均衡模式由配置狀態中通告的相互支持的 EQ 模式決定

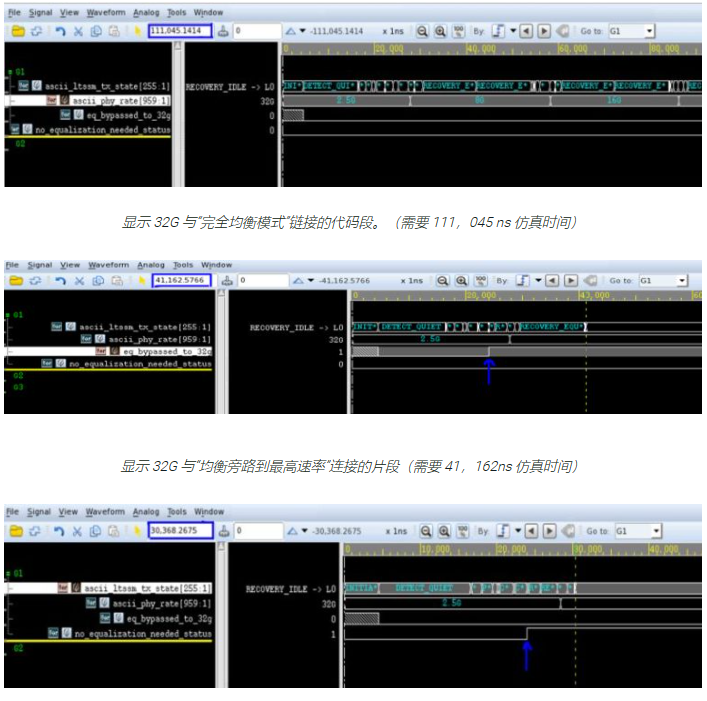

以下是 Synopsys 內部模擬的一些片段,顯示了不同均衡模式下高達 32GT/s 的連接時間

顯示 32G 連接“無需均衡”模式的代碼片段(需要 30,368 ns 仿真時間)

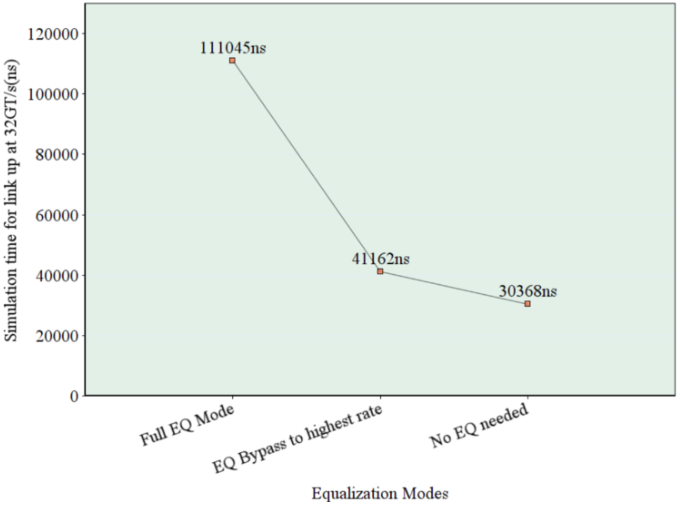

下圖顯示了如何通過新的均衡模式大幅縮短至32GT/s的鏈路啟動時間:

Synopsys PCIe 5.0 VIP 完全符合最新的 PCIe 5.0 規范。我們的VIP有助于解決鏈路均衡的主要驗證挑戰,以確保LTSSM在上圖中列出的所有三種均衡模式下正確轉換。選擇可選的均衡功能支持,允許覆蓋整個LTSSM狀態范圍,以及連接期間的速度轉換可能性都是完全可配置的。用戶還可以配置預設、預設提示或系數等。以確保 DUT 可以正確執行鏈路均衡。

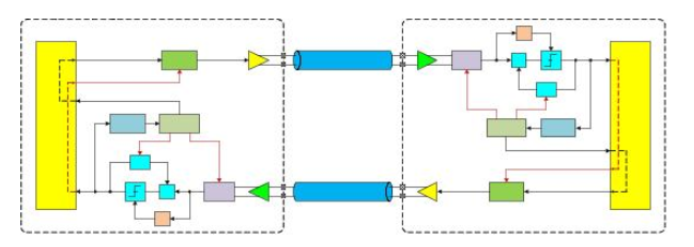

Synopsys VIP 和測試套件提供完整的解決方案,其中包含一系列測試,以驗證 PCIe 5.0 均衡功能的各種類型的 DUT(EP DUT、RC DUT、PHY DUT 和重定時 DUT)。

審核編輯:郭婷

-

以太網

+關注

關注

40文章

5460瀏覽量

172726 -

數據中心

+關注

關注

16文章

4858瀏覽量

72380 -

PCIe

+關注

關注

15文章

1260瀏覽量

83188

發布評論請先 登錄

相關推薦

PCIe Gen3/Gen4接收端鏈路均衡測試(上篇:理論篇)

使用Zynq設備和Tandem配置的PCIe BOOTUP時間有什么要求?

PCIe 3.0/4.0的鏈路均衡的工作原理

從Bootloader的角度探討如何優化進而縮短啟動時間

電機啟動時間一般是多久?怎么縮短啟動時間呢?

Xilinx7系列基于PCIe的設計如何滿足PCIe啟動時間的要求

基于FPGA的PCIe設備如何才能滿足PCIe設備的啟動時間的要求?

什么是 PCIe 5.0? PCIe 5.0規范以及挑戰

[PCIe] [電源管理] 面向硬件的ASPM鏈路狀態和L1子狀態

![[<b class='flag-5'>PCIe</b>] [電源管理] 面向硬件的ASPM<b class='flag-5'>鏈</b><b class='flag-5'>路</b>狀態和L1子狀態](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

開關電源啟動性能檢測之啟動時間測試方法

在i.MXRT1xxx系列上用NAND型啟動設備時可用兩級設計縮短啟動時間

PCIe 5.0均衡模式:縮短鏈路啟動時間

PCIe 5.0均衡模式:縮短鏈路啟動時間

評論