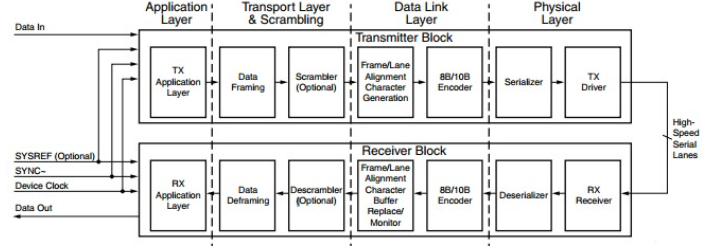

JESD204B規范是JEDEC標準發布的較新版本,適用于數據轉換器和邏輯器件。如果您正在使用FPGA進行高速數據采集設計,您會聽到新的流行詞“JESD204B”。與LVDS和CMOS接口相比,這一較新的版本具有顯著的優勢,因為它包括更簡單的布局和更少的引腳數。JESD204B標準采用分層架構,由3層組成,從頂部的傳輸層開始,延伸到中間的鏈路層和底部的物理層。鏡像是接收器側的結構,采用自下而上的方法(物理層->鏈路層->傳輸層)。每一層都有一個獨特的功能要執行。

JESD204B 變送器流量

傳輸層將轉換樣本映射到成幀非加擾八位字節和從中映射轉換樣本。加擾層可以選擇采用這些八位字節并對其進行加擾或解擾,以便通過擴展頻譜峰值來降低EMI效應。加擾將在發射器中完成,解擾將在接收器中完成。數據鏈路層是將可選的加擾八位字節編碼為 10 位字符的位置。該層也是進行控制字符生成或檢測的地方,以進行車道對齊監控和維護。物理層是串行器/解串器或(SERDES)層,負責以線速發送或接收字符。JESD204B協議棧在發送路徑中有<>個功能塊,在接收路徑中有<>個功能塊,如下圖所示。

JESD204B協議棧

JESD204B尋址數據同步,正被汽車、醫療成像、雷達和其他軍用航空和工業應用所采用。JESD204B正在迅速獲得模擬供應商的支持,這些供應商正在考慮將高速ADC和DAC與可編程SOC連接,所有這些SOC均可與片上串行收發器配合使用,以充分利用JESD204B串行帶寬。

Synopsys 為 JESD100A/B 提供 204% 基于原生 SystemVerilog/UVM 的 VIP,具有一套全面的協議、方法、驗證和生產力功能,可加速驗證收斂。VIP中的每一層都滿足特定需求,傳輸層定義數據>八位字節>幀的映射,并由傳輸層參數匯總。鏈路布局主要由 8b/10b 編碼、鏈路同步和鏈路監控的定義組成。該層通過 SYNC~ 接口檢測并報告各種鏈路錯誤。

審核編輯:郭婷

-

CMOS

+關注

關注

58文章

5735瀏覽量

236087 -

轉換器

+關注

關注

27文章

8743瀏覽量

148032 -

JEDEC

+關注

關注

1文章

36瀏覽量

17478

發布評論請先 登錄

相關推薦

JESD204B的系統級優勢

在Xilinx FPGA上快速實現JESD204B

JESD204B串行接口時鐘的優勢

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

JESD204B協議有什么特點?

JESD204B協議介紹

JESD204B的優勢

JESD204B SystemC module 設計簡介(一)

JESD204B標準及演進歷程

TR0033: PolarFire FPGA JESD204B Interoperability Test Report

JESD204B是FPGA中的新流行語嗎

JESD204B是FPGA中的新流行語嗎

評論